FPGA 浮動小数点ライブラリ IP マッピング

この例では、Altera® や Xilinx® などのベンダー固有の浮動小数点 IP ライブラリを使用してターゲット固有の HDL コードを生成する方法を示します。設計を浮動小数点ライブラリにマッピングする方法の詳細については、ベンダー固有の FPGA 浮動小数点ターゲット ライブラリの HDL コードの生成を参照してください。

浮動小数点演算をもつ設計を実装すると、より高い精度とより広いダイナミック レンジでのモデル化が可能になり、浮動小数点データから固定小数点データへの変換も回避できます。浮動小数点設計は、モデルベース デザインに特に有益です。モデルベース デザインでは、高水準なアルゴリズムが浮動小数点データでモデル化され、パイプラインやタイミング制約のような実装のタイミングに関する詳細がありません。しかし、演算を浮動小数点 IP モジュールにマッピングするにはタイミングの詳細が必要です。HDL Coder™ は、それらのタイミングの詳細をもつ設計を自動的に最適化して実装し、それらを調整するためのインターフェイスを提供します。その後、HDL Coder はベンダー ライブラリの浮動小数点 IP モジュールと統合して浮動小数点演算を実装します。

モデルを開く

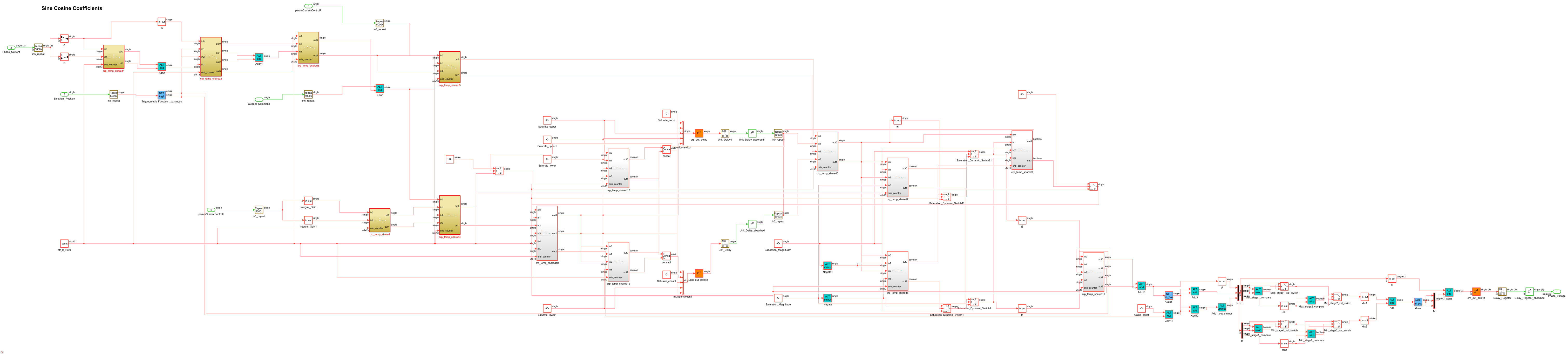

このベクトル制御 (FOC) アルゴリズムの例では、設計を浮動小数点ライブラリにマッピングする方法を示します。このアルゴリズムの詳細については、永久磁石同期機のベクトル制御を参照してください。

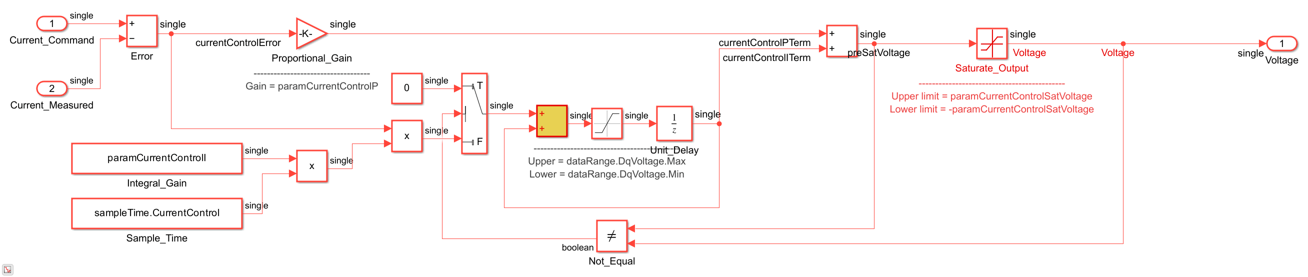

このモデルでは単精度データ型を使用しており、加算器、乗算器、比較器、複雑な正弦関数と余弦関数など、基本的な数学演算子を実行するブロックが含まれています。

このモデルでは、信号レートは 20  または 50 KHz でモデル化されています。このモデルには数値実装のみが含まれ、演算のレイテンシなどの FPGA 実装のタイミングに関する詳細はありません。数値演算は、正弦関数と余弦関数も含め、すべて単一のサンプル タイムステップで計算されます。

または 50 KHz でモデル化されています。このモデルには数値実装のみが含まれ、演算のレイテンシなどの FPGA 実装のタイミングに関する詳細はありません。数値演算は、正弦関数と余弦関数も含め、すべて単一のサンプル タイムステップで計算されます。

load_system('hdlcoderFocCurrentSingleTargetHdl'); open_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Sine_Cosine');

浮動小数点マッピングのための FPGA の設定

ベンダー固有の浮動小数点ライブラリにマッピングするには、ターゲットにする合成ツールとチップを選択して FPGA デバイスを設定します。合成ツールを設定する前に、関数 hdlsetuptoolpath を使用して合成ツールのパスを設定します。この例では、Altera Quartus と XILINX ISE の両方を合成ツールとして使用します。quartuspath と isepath は、Altera Quartus II 合成ツールと Xilinx ISE 合成ツールの合成ツールのパスをそれぞれ返します。環境でのツールの設定方法の詳細については、hdlsetuptoolpathを参照してください。

hdlsetuptoolpath('ToolName', 'Altera Quartus II','ToolPath', quartuspath); hdlsetuptoolpath('ToolName', 'XILINX ISE','ToolPath', isepath);

Prepending following Altera Quartus II path(s) to the system path: D:\share\apps\HDLTools\Altera\22.1.1-mw-0\Windows\quartus\bin64 Setting XILINX environment variable to: D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\ISE Setting XILINX_EDK environment variable to: D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\EDK Setting XILINX_PLANAHEAD environment variable to: D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\PlanAhead Prepending following XILINX ISE path(s) to the system path: D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\ISE\bin\nt64;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\ISE\lib\nt64;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\EDK\bin\nt64;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\EDK\lib\nt64;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\EDK\gnuwin\bin;D:\share\apps\HDLTools\Xilinx_ISE\14.7-mw-0\Win\ISE_DS\PlanAhead\bin

関数 hdlset_param を使用して、HDL モデル プロパティ SynthesisTool と SynthesisToolChipFamily を Altera Quartus II と Arria 10 にそれぞれ設定します。

hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'SynthesisTool', 'Altera Quartus II'); hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'SynthesisToolChipFamily', 'Arria 10');

FPGA IP ライブラリの選択と浮動小数点構成オブジェクトの作成

ネイティブ浮動小数点ライブラリとベンダー固有の FPGA 浮動小数点ライブラリにマッピングするには、ターゲットにするベンダー ライブラリを選択します。Xilinx デバイスの場合は、XILINXLOGICORE ライブラリを使用します。Altera デバイスの場合は、ALTERAFPFUNCTIONS ライブラリまたは ALTFP ライブラリを使用します。サポートされるデバイスについては、ライブラリのドキュメンテーションを確認してください。

関数 createFloatingPointTargetConfig を使用して名前と値の引数 VendorFloatingPointLibrary を ALTERAFPFUNCTIONS に設定し、ネイティブ浮動小数点ライブラリと ALTERAFPFUNCTIONS ライブラリの組み合わせに対する浮動小数点ターゲット構成オブジェクトを作成します。浮動小数点ターゲット構成オブジェクトの作成の詳細については、createFloatingPointTargetConfigを参照してください。

fc = hdlcoder.createFloatingPointTargetConfig(VendorFloatingPointLibrary = 'ALTERAFPFUNCTIONS')

fc =

FloatingPointTargetConfig with properties:

Library: 'NATIVEFLOATINGPOINT'

LibrarySettings: [1×1 fpconfig.NFPLatencyDrivenMode]

IPConfig: [1×1 hdlcoder.FloatingPointTargetConfig.IPConfig]

VendorLibrary: 'ALTERAFPFUNCTIONS'

VendorLibrarySettings: [1×1 fpconfig.FrequencyDrivenMode]

VendorIPConfig: [1×1 hdlcoder.FloatingPointTargetConfig.IPConfig]

モデルの浮動小数点構成オブジェクトを構成オブジェクト fc に設定します。

hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'FloatingPointTargetConfiguration', fc);

生成されたコードを QuestaSim でコンパイルしてシミュレートするには、Altera シミュレーション ライブラリをコンパイルし、そのパスを SimulationLibPath パラメーターを使用して設定します。詳細については、ツールの設定を参照してください。alterasimulationlibpath は、コンパイルされた Altera シミュレーション ライブラリのパスを返します。

hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'SimulationLibPath', alterasimulationlibpath);

Altera Megafunction (ALTERAFPFUNCTIONS) ライブラリでは、特定のターゲット周波数の IP モジュールを生成できます。この例では、ターゲット周波数を 250 MHz に設定します。

hdlset_param('hdlcoderFocCurrentSingleTargetHdl', 'TargetFrequency', 250);

IP マッピングのためのコードの生成とモデルの調整

makehdl コマンドを使用して、DUT サブシステム FOC_Current_Control の HDL コードを生成します。

try makehdl('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control'); catch me disp(me.message); end

### Working on the model <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl')">hdlcoderFocCurrentSingleTargetHdl</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control')">hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocCurrentSingleTargetHdl', { 'HDL Code Generation' } )">hdlcoderFocCurrentSingleTargetHdl</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocCurrentSingleTargetHdl'.

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Working on the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Using D:\share\apps\HDLTools\Altera\22.1.1-mw-0\Windows\quartus\bin64\..\sopc_builder\bin\ip-generate for the selected floating point IP library.

### Generating Altera(R) megafunction: alterafpf_add_single for target frequency of 250 MHz.

### alterafpf_add_single takes 3 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_mul_single for target frequency of 250 MHz.

### alterafpf_mul_single takes 3 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_lt_single_LT for target frequency of 250 MHz.

### alterafpf_lt_single_LT takes 1 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_gt_single_GT for target frequency of 250 MHz.

### alterafpf_gt_single_GT takes 1 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_sub_single for target frequency of 250 MHz.

### alterafpf_sub_single takes 3 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_neq_single_NEQ for target frequency of 250 MHz.

### alterafpf_neq_single_NEQ takes 0 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_le_single_LE for target frequency of 250 MHz.

### alterafpf_le_single_LE takes 1 cycles.

### Done.

### Generating Altera(R) megafunction: alterafpf_ge_single_GE for target frequency of 250 MHz.

### alterafpf_ge_single_GE takes 1 cycles.

### Done.

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightDelayAbsorption')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightDelayAbsorption.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\clearhighlighting.m')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\clearhighlighting.m</a>

### Creating HDL Code Generation Check Report file:///C:/Users/user/OneDrive%20-%20MathWorks/Documents/MATLAB/ExampleManager/user.Dec27/hdlcoder-ex07589604/hdlsrc/hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocCurrentSingleTargetHdl' complete with 1 errors, 0 warnings, and 1 messages.

### HDL check for 'hdlcoderFocCurrentSingleTargetHdl' complete with 1 errors, 0 warnings, and 1 messages.

For the block 'hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/Q_Current_Control'

Delay balancing unsuccessful. Cause:

The input and output configurations of this atomic subsystem cause delay balancing to fail. Consider making it non-atomic. Offending block: hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/Q_Current_Control

エラー メッセージは、フィードバック ループの遅延が HDL Coder で置き換えようとしている浮動小数点 IP モジュールのレイテンシよりも少ないため、それらのループ内の演算を HDL Coder で浮動小数点 IP モジュールに置き換えることができないことを示しています。HDL Coder では、浮動小数点 IP モジュールをパイプライン方式のブロックとして実装します。一部のモジュールには最小レイテンシの要件があります。フィードバック ループのレイテンシが変わると正しい実装が生成されないため、HDL Coder では、それらのフィードバック ループ内のレイテンシは追加できないようになっています。

このエラーは、フィードバック ループ内の加算器に複数のサイクルのレイテンシの割り当てが必要であるのに対し、ループに遅延が 1 つしかないことを示しています。

hilite_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add');

これらのエラーに対処するには、次のいずれかの方法を使用できます。

ターゲット周波数を小さくすると、パイプラインの深さの要件が軽減されることがあります。この変更により、設計内の他のすべての IP モジュールも遅くなる可能性があります。

ループで使用される IP モジュールをレイテンシが小さくなるように構成します。この場合、IP モジュールの動作周波数も遅くなりますが、影響を受けるのは指定した IP モジュールのみです。

クロック レート パイプラインを適用します。データ レートが FPGA のクロック レートよりも遅い場合、FPGA では、演算が終了するまでにクロック レートで複数のサイクルが必要になり、引き続き数値の整合性が維持されます。クロック レート パイプラインの詳細については、クロックレート パイプラインを参照してください。

サンプル時間が 20  で、FPGA のターゲット周波数が 250 MHz (4 ナノ秒) であるため、

で、FPGA のターゲット周波数が 250 MHz (4 ナノ秒) であるため、TreatRatesAsHardwareRates を on に設定することで、クロックレート パイプラインを適用してフィードバック ループの問題を解決できます。TreatRatesAsHardwarRates により、HDL Coder は、Simulink 基本レートを実際のハードウェアのレートとして扱い、ターゲット周波数と Simulink 基本レートの比としてオーバーサンプリング値を計算することで、設計に対して自動的にオーバーサンプリング値を決定できます。その後、HDL Coder はクロックレート パイプライン用にそのオーバーサンプリング値を使用します。詳細については、Simulink のレートを実際のハードウェアのレートとして扱うを参照してください。この例では、計算されたオーバーサンプリング値は 5000 です。これは、モデルにおける 20  のサンプル時間の 1 単位遅延が、FPGA での 4 ナノ秒のサンプル時間では 5000 クロックレート サイクルに相当することを意味します。この値はループ内の浮動小数点 IP モジュールに対して十分です。

のサンプル時間の 1 単位遅延が、FPGA での 4 ナノ秒のサンプル時間では 5000 クロックレート サイクルに相当することを意味します。この値はループ内の浮動小数点 IP モジュールに対して十分です。

TreatRatesAsHardwareRates を有効にし、生成モデルと検証モデルの生成を有効にします。

hdlset_param('hdlcoderFocCurrentSingleTargetHdl','TreatRatesAsHardwareRates','on'); hdlset_param('hdlcoderFocCurrentSingleTargetHdl','GenerateModel','on'); hdlset_param('hdlcoderFocCurrentSingleTargetHdl','GenerateValidationModel','on');

makehdl コマンドを使用して、DUT サブシステム FOC_Current_Control の HDL コードを生成します。

makehdl('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control');

### Working on the model <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl')">hdlcoderFocCurrentSingleTargetHdl</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control')">hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocCurrentSingleTargetHdl', { 'HDL Code Generation' } )">hdlcoderFocCurrentSingleTargetHdl</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocCurrentSingleTargetHdl'.

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Working on the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Using D:\share\apps\HDLTools\Altera\22.1.1-mw-0\Windows\quartus\bin64\..\sopc_builder\bin\ip-generate for the selected floating point IP library.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_lt_single_LT.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_lt_single_LT for target frequency of 250 MHz.

### alterafpf_lt_single_LT takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_gt_single_GT.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_gt_single_GT for target frequency of 250 MHz.

### alterafpf_gt_single_GT takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_mul_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_mul_single for target frequency of 250 MHz.

### alterafpf_mul_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_le_single_LE.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_le_single_LE for target frequency of 250 MHz.

### alterafpf_le_single_LE takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_ge_single_GE.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_ge_single_GE for target frequency of 250 MHz.

### alterafpf_ge_single_GE takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_sub_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_sub_single for target frequency of 250 MHz.

### alterafpf_sub_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_add_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_add_single for target frequency of 250 MHz.

### alterafpf_add_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_neq_single_NEQ.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_neq_single_NEQ for target frequency of 250 MHz.

### alterafpf_neq_single_NEQ takes 0 cycles.

### Done.

### The code generation and optimization options you have chosen have introduced additional pipeline delays.

### The delay balancing feature has automatically inserted matching delays for compensation.

### The DUT requires an initial pipeline setup latency. Each output port experiences these additional delays.

### Output port 1: 2 cycles.

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocCurrentSingleTargetHdl', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderFocCurrentSingleTargetHdl'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl.slx')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl.slx</a>

### Clock-rate pipelining obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightClockRatePipelining')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightClockRatePipelining.m</a>

### Delay absorption obstacles can be diagnosed by running this script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightDelayAbsorption')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\highlightDelayAbsorption.m</a>

### To clear highlighting, click the following MATLAB script: <a href="matlab:run('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\clearhighlighting.m')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\clearhighlighting.m</a>

### Generating new validation model: <a href="matlab:open_system('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl_vnl')">gm_hdlcoderFocCurrentSingleTargetHdl_vnl</a>.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderFocCurrentSingleTargetHdl'.

### MESSAGE: The design requires 5000 times faster clock with respect to the base rate = 2e-05.

### Begin VHDL Code Generation for 'FOC_Current_Control_tc'.

### Working on FOC_Current_Control_tc as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control_tc.vhd.

### Code Generation for 'FOC_Current_Control_tc' completed.

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocCurrentSingleTargetHdl', 'Traceability')">Traceability</a>

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Saturate_Output/nfp_uminus_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_uminus_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Saturate_Output as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Saturate_Output.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\D_Current_Control.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\DQ_Current_Control.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Clarke_Transform as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Clarke_Transform.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Sine_Cosine/nfp_sincos_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_sincos_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Sine_Cosine as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Sine_Cosine.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Park_Transform as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Park_Transform.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Inverse_Park_Transform as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Inverse_Park_Transform.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Inverse_Clarke_Transform/nfp_gain_pow2_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_gain_pow2_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Inverse_Clarke_Transform as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Inverse_Clarke_Transform.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/Space_Vector_Modulation as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Space_Vector_Modulation.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control.vhd.

### Generating package file hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control_pkg.vhd.

### Code Generation for 'hdlcoderFocCurrentSingleTargetHdl' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openDdg('C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\html\hdlcoderFocCurrentSingleTargetHdl_codegen_rpt.html')">hdlcoderFocCurrentSingleTargetHdl_codegen_rpt.html</a>

### Creating HDL Code Generation Check Report file:///C:/Users/user/OneDrive%20-%20MathWorks/Documents/MATLAB/ExampleManager/user.Dec27/hdlcoder-ex07589604/hdlsrc/hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocCurrentSingleTargetHdl' complete with 0 errors, 0 warnings, and 5 messages.

### HDL code generation complete.

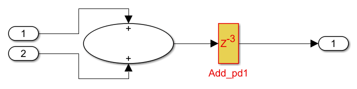

これで、設計が浮動小数点 IP モジュールにマッピングされます。ターゲット コード生成レポートに、浮動小数点 IP モジュールの使用についての概要が示されます。生成されたモデルを開いて確認します。たとえば、サブシステム hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add に対応するサブシステム gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add について、この演算に 3 サイクルかかることがわかります。

hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add/Add_pd1'); get_param('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/DQ_Current_Control/D_Current_Control/Add/Add_pd1', ... 'DelayLength')

ans =

'3'

浮動小数点 IP モジュールによって設計全体にレイテンシが導入されるため、HDL Coder は、データの同期を維持するために一致する遅延を追加します。詳細については、HDL Coder での遅延の均衡化の理解を参照してください。

浮動小数点 IP の共有

浮動小数点 IP モジュールは、同じ種類であれば通常は同じであるため、共有に適しています。浮動小数点 IP は一般に計算量の多い演算であり、可能であれば、それらのリソースを共有して面積のフットプリントを削減することが推奨されます。HDL Coder は、同じサブシステム内のリソースを共有します。より多くのリソースが共有されるように、サブシステムの階層をフラット化し、最上位のネットワークでリソース共有係数を 4 に設定します。

hdlset_param('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control', 'FlattenHierarchy', 'on'); hdlset_param('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control', 'SharingFactor', 4);

makehdl コマンドを使用して、DUT サブシステム FOC_Current_Control の HDL コードを生成します。

makehdl('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control');

### Working on the model <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl')">hdlcoderFocCurrentSingleTargetHdl</a>

### Generating HDL for <a href="matlab:open_system('hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control')">hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control</a>

### Using the config set for model <a href="matlab:configset.showParameterGroup('hdlcoderFocCurrentSingleTargetHdl', { 'HDL Code Generation' } )">hdlcoderFocCurrentSingleTargetHdl</a> for HDL code generation parameters.

### Running HDL checks on the model 'hdlcoderFocCurrentSingleTargetHdl'.

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Begin compilation of the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Working on the model 'hdlcoderFocCurrentSingleTargetHdl'...

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_add_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_add_single for target frequency of 250 MHz.

### alterafpf_add_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_sub_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_sub_single for target frequency of 250 MHz.

### alterafpf_sub_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_mul_single.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_mul_single for target frequency of 250 MHz.

### alterafpf_mul_single takes 3 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_lt_single_LT.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_lt_single_LT for target frequency of 250 MHz.

### alterafpf_lt_single_LT takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_gt_single_GT.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_gt_single_GT for target frequency of 250 MHz.

### alterafpf_gt_single_GT takes 1 cycles.

### Done.

### Using D:\share\apps\HDLTools\Altera\22.1.1-mw-0\Windows\quartus\bin64\..\sopc_builder\bin\ip-generate for the selected floating point IP library.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_neq_single_NEQ.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_neq_single_NEQ for target frequency of 250 MHz.

### alterafpf_neq_single_NEQ takes 0 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_ge_single_GE.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_ge_single_GE for target frequency of 250 MHz.

### alterafpf_ge_single_GE takes 1 cycles.

### Done.

### Found an existing generated file in a previous session: (C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\Altera\Arria_10\unspecified\F250\synth\alterafpf_le_single_LE.vhd). Reusing the generated file.

### Generating Altera(R) megafunction: alterafpf_le_single_LE for target frequency of 250 MHz.

### alterafpf_le_single_LE takes 1 cycles.

### Done.

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocCurrentSingleTargetHdl', 'GenerateModel')">GenerateModel</a>

### Begin model generation 'gm_hdlcoderFocCurrentSingleTargetHdl'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Model generation complete.

### Generated model saved at <a href="matlab:open_system('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl.slx')">hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl.slx</a>

### Generating new validation model: <a href="matlab:open_system('hdlsrc\hdlcoderFocCurrentSingleTargetHdl\gm_hdlcoderFocCurrentSingleTargetHdl_vnl')">gm_hdlcoderFocCurrentSingleTargetHdl_vnl</a>.

### Validation model generation complete.

### Begin VHDL Code Generation for 'hdlcoderFocCurrentSingleTargetHdl'.

### MESSAGE: The design requires 5000 times faster clock with respect to the base rate = 2e-05.

### Begin VHDL Code Generation for 'FOC_Current_Control_tc'.

### Working on FOC_Current_Control_tc as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control_tc.vhd.

### Code Generation for 'FOC_Current_Control_tc' completed.

### Working on... <a href="matlab:configset.internal.open('hdlcoderFocCurrentSingleTargetHdl', 'Traceability')">Traceability</a>

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/nfp_gain_pow2_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_gain_pow2_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/nfp_uminus_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_uminus_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/nfp_sincos_single as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\nfp_sincos_single.vhd.

### Working on hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control as hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control.vhd.

### Generating package file hdlsrc\hdlcoderFocCurrentSingleTargetHdl\FOC_Current_Control_pkg.vhd.

### Code Generation for 'hdlcoderFocCurrentSingleTargetHdl' completed.

### Generating HTML files for code generation report at <a href="matlab:hdlcoder.report.openDdg('C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Dec27\hdlcoder-ex07589604\hdlsrc\hdlcoderFocCurrentSingleTargetHdl\html\hdlcoderFocCurrentSingleTargetHdl_codegen_rpt.html')">hdlcoderFocCurrentSingleTargetHdl_codegen_rpt.html</a>

### Creating HDL Code Generation Check Report file:///C:/Users/user/OneDrive%20-%20MathWorks/Documents/MATLAB/ExampleManager/user.Dec27/hdlcoder-ex07589604/hdlsrc/hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control_report.html

### HDL check for 'hdlcoderFocCurrentSingleTargetHdl' complete with 0 errors, 0 warnings, and 3 messages.

### HDL code generation complete.

生成されたモデルで推定される IP モジュールが少なくなっています。この変化は浮動小数点リソース レポートで確認できます。

生成されたモデルを開いてリソース共有の結果を確認します。

open_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control'); set_param('gm_hdlcoderFocCurrentSingleTargetHdl', 'SimulationCommand', 'update'); set_param('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control', 'ZoomFactor', 'FitSystem'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared1'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared2'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared3'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared4'); hilite_system('gm_hdlcoderFocCurrentSingleTargetHdl/FOC_Current_Control/crp_temp_shared5');

IP ライブラリの構成

浮動小数点 IP ライブラリのカスタマイズの構成を設計要件に合わせて編集して制御できます。

ネイティブ浮動小数点ライブラリと XILINX LOGICORE ライブラリに対する混合モードの浮動小数点ターゲット構成オブジェクトを作成します。

fc = hdlcoder.createFloatingPointTargetConfig(VendorFloatingPointLibrary = 'XILINXLOGICORE');

構成オブジェクトに Library、LibrarySettings、および IPConfig としてそれぞれ格納されるネイティブ浮動小数点ライブラリのライブラリ名、ライブラリ設定、および個々の IP 構成の設定に加え、構成オブジェクトには、VendorLibrary、VendorLibrarySettings、および VendorIPConfig として指定される XILINX LOGICORE ライブラリのそれらのプロパティも含まれます。構成オブジェクト fc を確認します。

fc

fc =

FloatingPointTargetConfig with properties:

Library: 'NATIVEFLOATINGPOINT'

LibrarySettings: [1×1 fpconfig.NFPLatencyDrivenMode]

IPConfig: [1×1 hdlcoder.FloatingPointTargetConfig.IPConfig]

VendorLibrary: 'XILINXLOGICORE'

VendorLibrarySettings: [1×1 fpconfig.LatencyDrivenMode]

VendorIPConfig: [1×1 hdlcoder.FloatingPointTargetConfig.IPConfig]

VendorLibrarySettings プロパティには、ベンター固有の浮動小数点ライブラリのライブラリ全体の設定が含まれます。XILINX LOGICORE ライブラリの設定を確認します。

fc.VendorLibrarySettings

ans =

LatencyDrivenMode with properties:

LatencyStrategy: 'MIN'

Objective: 'SPEED'

Objective プロパティは、XILINX LOGICORE に対して c_optimization パラメーターを指定します。Objective プロパティを AREA に設定します。

fc.VendorLibrarySettings.Objective = 'AREA';

fc.VendorLibrarySettings

ans =

LatencyDrivenMode with properties:

LatencyStrategy: 'MIN'

Objective: 'AREA'

ベンダー ライブラリの設定はライブラリに固有です。特定のライブラリの設定を確認するには、hdlcoder.FloatingPointTargetConfigを参照してください。

VendorIPConfig プロパティは、ベンダー固有のライブラリの IPConfig オブジェクトを保持します。このオブジェクトには、Latency や ExtraArgs など、関数 customize を使用して変更できる個々の IP モジュールの設定が含まれます。

関数 customize を使用して、個々の IP モジュールのレイテンシを構成オブジェクトで指定します。設定した Latency 入力引数の値が HDL Coder でコード生成と最適化に使用されます。

fc.VendorIPConfig.customize('ADDSUB', 'SINGLE', 'Latency', 11); fc.VendorIPConfig

ans =

Name DataType MinLatency MaxLatency Latency ExtraArgs

__________ __________ __________ __________ _______ __________

{'ADDSUB'} {'DOUBLE'} 12 12 -1 {0×0 char}

{'ADDSUB'} {'SINGLE'} 12 12 11 {0×0 char}

{'DIV' } {'DOUBLE'} 57 57 -1 {0×0 char}

{'DIV' } {'SINGLE'} 28 28 -1 {0×0 char}

{'MUL' } {'DOUBLE'} 9 9 -1 {0×0 char}

{'MUL' } {'SINGLE'} 8 8 -1 {0×0 char}

{'RELOP' } {'DOUBLE'} 2 2 -1 {0×0 char}

{'RELOP' } {'SINGLE'} 2 2 -1 {0×0 char}

{'SQRT' } {'DOUBLE'} 57 57 -1 {0×0 char}

{'SQRT' } {'SINGLE'} 28 28 -1 {0×0 char}

ADDSUB IP のレイテンシが既定値の 12 ではなく 11 になります。

その他の IP 固有の設定は、個々の IP モジュールの ExtraArgs プロパティを設定して指定できます。たとえば、HDL Coder は、XILINX LOGICORE を呼び出して浮動小数点 IP モジュールを生成する際、既定では DSP ブロックを使用しません。XILINX LOGICORE では、DSP の使用方法の制御に c_mult_usage パラメーターを使用します。DSP ブロックを使用する場合は、ExtraArgs 入力引数を使用して別の設定を渡して既定の動作をオーバーライドします。ExtraArgs の文字列は既定の IP モジュール生成パラメーターに加えられるため、ライブラリの設定の構文に準拠しなければなりません。パラメーターの使用法と構文については、IP ライブラリのドキュメントを確認してください。

fc.VendorIPConfig.customize('ADDSUB', 'SINGLE', 'ExtraArgs', 'CSET c_mult_usage=Full_Usage'); fc.VendorIPConfig

ans =

Name DataType MinLatency MaxLatency Latency ExtraArgs

__________ __________ __________ __________ _______ ________________________________

{'ADDSUB'} {'DOUBLE'} 12 12 -1 {0×0 char }

{'ADDSUB'} {'SINGLE'} 12 12 11 {'CSET c_mult_usage=Full_Usage'}

{'DIV' } {'DOUBLE'} 57 57 -1 {0×0 char }

{'DIV' } {'SINGLE'} 28 28 -1 {0×0 char }

{'MUL' } {'DOUBLE'} 9 9 -1 {0×0 char }

{'MUL' } {'SINGLE'} 8 8 -1 {0×0 char }

{'RELOP' } {'DOUBLE'} 2 2 -1 {0×0 char }

{'RELOP' } {'SINGLE'} 2 2 -1 {0×0 char }

{'SQRT' } {'DOUBLE'} 57 57 -1 {0×0 char }

{'SQRT' } {'SINGLE'} 28 28 -1 {0×0 char }

モデル hdlcoder_targetIP_configuration を開き、浮動小数点構成オブジェクト fc をモデルの浮動小数点ターゲット構成に設定します。

open_system('hdlcoder_targetIP_configuration'); hdlset_param('hdlcoder_targetIP_configuration', 'FloatingPointTargetConfiguration', fc);

次のコマンドを使用して合成とマッピングを実行し、DSP ブロックの使用方法を確認します。

hWC = hdlcoder.WorkflowConfig('SynthesisTool','Xilinx ISE', ...

'TargetWorkflow','Generic ASIC/FPGA');

hWC.SkipPreRouteTimingAnalysis = true;

hWC.RunTaskAnnotateModelWithSynthesisResult = false;

hWC.GenerateRTLCode = true;

hWC.validate;

hdlcoder.runWorkflow('hdlcoder_targetIP_configuration/Add_Subsystem', hWC);参考

hdlcoder.FloatingPointTargetConfig | createFloatingPointTargetConfig | hdlcoder.FloatingPointTargetConfig.IPConfig | customize