このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

PN Sequence Generator

疑似ノイズ シーケンスを生成する

ライブラリ:

Communications Toolbox /

Comm Sources /

Sequence Generators

Communications Toolbox HDL Support /

Comm Sources

説明

PN Sequence Generator ブロックは、線形フィードバック シフト レジスタ (LFSR) を使って一連の 2 値疑似乱数を生成します。疑似ノイズ シーケンスは、通常、疑似乱数スクランブルや直接シーケンス スペクトル拡散システムで使用されます。詳細については、詳細を参照してください。

これらのアイコンには、利用可能なすべての端子を使用したブロックが表示されています。

![]()

![]()

例

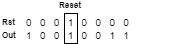

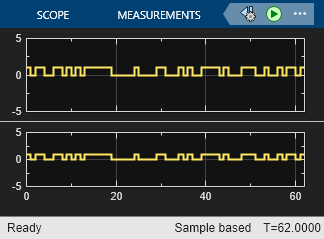

基本的な Simulink® ブロックで作成された線形フィードバック シフト レジスタ (LFSR) を使用することで、PN Sequence Generator ブロックから出力されるシーケンスをモデル化できます。

cm_ex__pnseq_vs_prim_sl モデルは、PN Sequence Generator ブロックを使用し、基本的な Simulink ブロックを使用して LFSR をモデル化することによって、生成多項式 p(z)=z^6+z+1 を生成します。離散ブロックの LFSR 図式モデルは、PN Sequence Generator ブロックの [初期状態] パラメーターおよび [出力マスク ベクトル (またはスカラー シフト値)] パラメーターを解釈します。PreLoadFcn コールバック関数は、ランタイム パラメーターを初期化します。Simulink ツールストリップからコールバック関数を表示するには、[モデル化] タブの [設計] ギャラリーで、[プロパティ インスペクター] をクリックします。

スコープの出力は、2 つの実装によって、一致する PN シーケンスが生成されることを示しています。

PN Sequence Generator ブロックを使用することで、長い周期の PN シーケンスを簡単に生成できます。さらに実験を行うため、モデルを開きます。設定を変更し、異なるパス遅延に対してパフォーマンスがどのように変化するかを確認したり、PN シーケンス発生器パラメーターを調整します。シミュレーションを実行する前に [初期状態] の値を変更することで、さまざまな初期状態で実験できます。すべての値において、生成される 2 つのシーケンスは同じです。

デジタル通信システムでは、タイミング同期のため、またパワー スペクトルの要件を満たすため、一般に加法スクランブルと加法デスクランブルを使用して入力データをランダム化します。Scramblerブロックは乗法スクランブルをサポートしますが、加法スクランブルはサポートしません。加法スクランブルを実行するには、PN Sequence Generatorブロックを使用できます。この例では、PN Sequence Generatorブロックによって生成された出力シーケンスで入力データをスクランブルすることにより、IEEE 802.11™ [1] で規定されている加法スクランブルを実装します。同様のワークフローをもつ MATLAB® の例については、comm.PNSequenceリファレンス ページの "入力データの加法スクランブル" の例を参照してください。

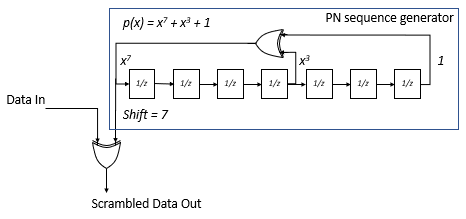

次の図は、IEEE 802.11™ の Section 17.3.5.5 [1] の図 17-7 で規定されている、生成多項式 ![]() を使用する加法スクランブラーを示しています。

を使用する加法スクランブラーを示しています。

802.11 で規定されているシフト レジスタと、PN Sequence Generator ブロックを使用して実装されたシフト レジスタを比較し、この 2 つのシフト レジスタの図が互いに鏡像になることを観察します。したがって、PN Sequence Generator ブロックを構成して加法スクランブラーを実装する場合、生成多項式、初期状態、およびマスク出力の値を逆にしなければなりません。レジスタの出力を先頭から取り出すには、シフト値に 7 を指定します。

802.11 スクランブラーの詳細については、[1] およびwlanScramble (WLAN Toolbox)リファレンス ページを参照してください。

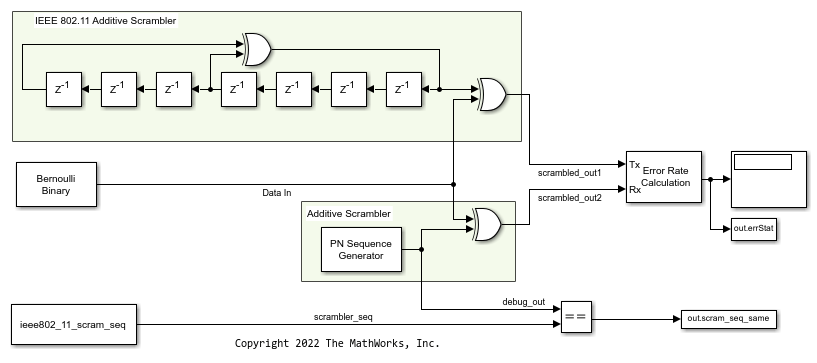

cm_additive_scrambling モデルは、次の 2 つの加法スクランブラーの実装を使用して、生成されたスクランブリング シーケンスと、802.11 で規定された加法スクランブラーに従ってスクランブルされたデータ フレームを、スクランブルして比較します。

離散のDelay (Simulink)ブロックと、XOR 演算子として構成されたLogical Operator (Simulink)ブロックから成るシフト レジスタ。

PN Sequence Generator ブロックと XOR 演算子。

加法スクランブラーの実装を比較するために、cm_additive_scrambling モデルでは以下を使用します。

スクランブルする入力信号を提供するBernoulli Binary Generatorブロック。

生成多項式として

を使用し、シフト レジスタの初期状態として [1 1 1 1 1 1 1] を使用し、スクランブル出力のシフト値として 7 を使用するように構成されたPN Sequence Generatorブロック。

を使用し、シフト レジスタの初期状態として [1 1 1 1 1 1 1] を使用し、スクランブル出力のシフト値として 7 を使用するように構成されたPN Sequence Generatorブロック。入力データにスクランブル シーケンスを適用するための XOR 演算子として構成されたLogical Operator (Simulink)ブロック。

離散ブロックから成るシフト レジスタから出力されたスクランブル後のデータと、加法スクランブラーの PN シーケンス版が一致することを確認するError Rate Calculationブロック。

IEEE 802.11 規格の Section 17.3.5.5 で規定されている 127 ビット スクランブラー出力シーケンスを含むワークスペース変数を作成する

PreLoadFcnコールバック関数。==演算用に構成されたRelational Operator (Simulink)は、Signal From Workspaceブロックからの出力である 127 ビットのスクランブラー シーケンスを PN Sequence ブロックの出力と比較します。

加法スクランブルのシミュレーション

モデルを実行し、スクランブルされた入力シーケンスのエラー レートの計算結果、およびスクランブラー シーケンスの場合と等しいかどうかの比較結果を表示します。

Number of errors in scrambled output comparison is 0. Number of mismatches comparing PN sequence output to IEEE 802.11 scrambler sequence 0.

参考文献

[1] IEEE Std 802.11™-2020 (Revision of IEEE Std 802.11-2016). "Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications." IEEE Standard for Information technology - Telecommunications and information exchange between systems. Local and metropolitan area networks - Specific requirements.

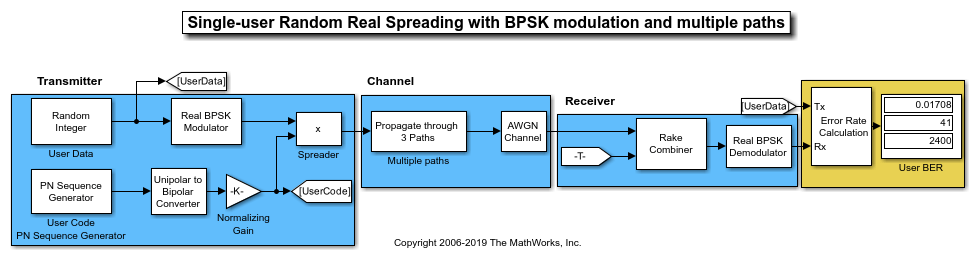

このモデルは、マルチパス伝送環境におけるシングルユーザー システムの疑似ランダム拡散をシミュレートします。これは、信号が複数のパスで受信される移動体チャネル環境と同等です。各パスの振幅と遅延は異なる場合があります。受信機は、ダイバーシティ受信を使用して独立したパスをコヒーレントに結合し、受信したマルチパス伝送からゲインを実現します。モデル化されたシステムではフェージング効果はシミュレートされず、受信機はパスの数とそれぞれの遅延を完全に認識します。

このモデルは、BPSK 変調されるランダムなバイナリ データ (実数) を使用します。これは、PN シーケンスで拡散されてから、マルチパス AWGN チャネルで送信されます。受信機は、逆拡散器、ダイバーシティ コンバイナー、および BPSK 復調器で構成されます。受信機は、データの拡散時に使用される PN シーケンスが理想的な自己相関特性をもつことによって、ダイバーシティ合成からゲインを達成します。

さらに実験を行うため、モデルを開きます。設定を変更し、異なるパス遅延に対してパフォーマンスがどのように変化するかを確認したり、PN シーケンス発生器パラメーターを調整します。

このモデルは、マルチパス伝送環境における 2 ユーザーの疑似ランダム拡散をシミュレートします。これは、信号が複数のパスで受信される移動体チャネル環境と同等です。各パスの振幅と遅延は異なる場合があります。受信機は、ダイバーシティ受信を使用して独立したパスをコヒーレントに結合し、受信したマルチパス伝送からゲインを実現します。モデル化されたシステムではフェージング効果はシミュレートされず、受信機はパスの数とそれぞれの遅延を完全に認識します。

このモデルは、BPSK 変調されるランダムなバイナリ データ (実数) を使用します。これは、PN シーケンスで拡散されてから、マルチパス AWGN チャネルで送信されます。受信機は、逆拡散器、ダイバーシティ コンバイナー、および BPSK 復調器で構成されます。

このモデルは、同じ送信データを使用して、一様に構成されたマルチパス AWGN チャネルでの 2 ユーザーの送信についてパフォーマンスを計算します。

個々のユーザーの送信が異なる PN シーケンスを使用して拡散されているため、ユーザーに対して計算されるエラー レートは異なります。データの拡散に使用されている非直交 PN シーケンスの相互相関特性が高いため、マルチパス環境では BER 性能が低下します。マルチパス環境には、アダマール シーケンスやカサミ シーケンスなど、直交性の高いシーケンスの方が適しています。ユーザー データの拡散時にアダマール符号シーケンスを使用するマルチパスの例については、単一パス チャネルにおけるマルチユーザー システムの直交拡散を参照してください。ユーザー データの拡散時にカサミ符号シーケンスを使用するマルチパスの例については、マルチパス チャネルにおけるマルチユーザー システムのカサミ拡散を参照してください。

さらに実験を行うため、モデルを開きます。設定を変更し、異なるパス遅延に対して、または個々のユーザーに異なる PN シーケンスを使用することでパフォーマンスがどのように変化するかを確認します。

端子

入力

PN シーケンスを初期時間から遅延させる出力マスク。N 個の要素をもつバイナリ ベクトルとして指定します。N は生成多項式の次数です。

依存関係

この端子を有効にするには、[出力マスク ソース] を [入力端子] に設定します。

データ型: double | uint8 | ufix1

可変サイズ出力信号の出力サイズ。整数として指定します。可変サイズ信号の詳細については、可変サイズの信号の基礎 (Simulink)を参照してください。

依存関係

この端子を有効にするには、[可変サイズの信号の出力] を選択し、[最大出力サイズ ソース] を [ダイアログ パラメーター] に設定します。

データ型: double

参照入力。最大および現在の出力シーケンス長を決定する列ベクトルとして指定します。Ref 入力は可変サイズ信号でなければなりません。可変サイズ信号の詳細については、可変サイズの信号の基礎 (Simulink)を参照してください。

依存関係

この端子を有効にするには、[可変サイズの信号の出力] を選択し、[最大出力サイズ ソース] を [Inherit from reference input] に設定します。

データ型: double

データ型: Boolean

パラメーター

ブロック パラメーターを対話的に編集するには、プロパティ インスペクターを使用します。Simulink® ツールストリップの [シミュレーション] タブの [準備] ギャラリーで [プロパティ インスペクター] を選択します。

シフト レジスタのフィードバック接続を決定する生成多項式。次のいずれかのオプションとして指定します。

定数項が

1の多項式の文字ベクトルまたは string スカラー。詳細については、Communications Toolbox での多項式の表現を参照してください。バイナリ値行ベクトル。降べきの順に並べた多項式の係数を表します。このベクトルの長さは N+1 でなければなりません。ここで N は多項式の次数です。最初と最後のエントリは

1でなければなりません。これは、次数 N の最初の項と、定数項 1 を示します。整数値の行ベクトル。降べきの順に並べた多項式の非ゼロの項の指数を表す要素からなります。最後のエントリは

0でなければなりません。これは定数項 1 を示します。

詳細については、単純なシフト レジスタ発生器および多項式の順序とシフト レジスタの方向を参照してください。

例: 'z^8 + z^2 + 1'、[1 0 0 0 0 0 1 0 1]、および [8 2 0] は同一の多項式 p(z) = z 8 + z 2 + 1 を表します。

シミュレーション開始時の PN シーケンス発生器のシフト レジスタの初期状態。バイナリ値行ベクトルとして指定します。ベクトルの長さは、[生成多項式] で指定される生成多項式の次数と等しくなければなりません。詳細については、単純なシフト レジスタ発生器および多項式の順序とシフト レジスタの方向を参照してください。

メモ

ブロックで非ゼロのシーケンスを生成するには、[初期状態] ベクトルに、非ゼロ要素が少なくとも 1 つ含まれていなければなりません。

出力マスク情報がブロックにどのように提供されるかを示す出力マスク ソース。次のいずれかとして指定します。

[Output mask vector (or scalar shift value)]パラメーター設定を使用するには[Dialog parameter]。Mask入力端子を追加して使用するには[Input port]。

出力マスク ベクトルまたはスカラー シフト値。整数スカラーまたは長さ N のバイナリ行ベクトルとして指定します。ここで、N は生成多項式の次数です。このパラメーターは、初期時間からの PN シーケンスの遅延を判断します。詳細については、PN シーケンスの開始点のシフトを参照してください。

依存関係

このパラメーターを有効にするには、[出力マスク ソース] を [ダイアログ パラメーター] に設定します。

シミュレーション中に可変長の出力シーケンスを有効にするには、このパラメーターを選択します。このパラメーターをオフにすると、ブロックは固定長のシーケンスを出力します。このパラメーターを選択すると、ブロックは可変長のシーケンスを出力できます。可変サイズ信号の詳細については、可変サイズの信号の基礎 (Simulink)を参照してください。

正のスカラーは、出力信号の各サンプル間の時間を秒単位で指定します。[サンプル時間] を -1 に設定すると、出力信号は下流からサンプル時間を継承します。[サンプル時間] パラメーターと [フレームあたりのサンプル数] パラメーターの関係の詳細については、サンプル タイミングを参照してください。

例: 1 は 1 秒のサンプル時間を指定します。

依存関係

このパラメーターを有効にするには、[可変サイズの信号の出力] をオフにします。

出力信号の 1 チャネル内のフレームあたりのサンプル。正の整数として指定します。[サンプル時間] と [フレームあたりのサンプル数] の関係の詳細については、サンプル タイミングを参照してください。

依存関係

このパラメーターを有効にするには、[Output variable-size signals] をオフにします。

最大のシーケンス出力サイズの指定方法を選択します。

[Dialog parameter]— [Maximum output size] パラメーター設定を最大許容出力シーケンス長として使用するブロックを構成するには、この値を選択します。[oSiz] 入力端子は出力信号の現在のサイズを指定し、ブロック出力はサンプル時間を入力信号から継承します。[oSiz] の入力値は [Maximum output size] パラメーターの値以下でなければなりません。[Inherit from reference port]— [Ref] 入力端子を有効にし、[Ref] 入力端子の可変サイズ信号からサンプル時間、最大サイズ、および現在の出力サイズを継承するブロックを構成するには、この値を選択します。これらにより最大許容出力シーケンス長が設定されます。

依存関係

このパラメーターを有効にするには、[Output variable-size signals] を選択します。

ブロックの最大出力サイズを指定します。n は正のスカラーです。

例: [10 1] の場合は、出力信号の最大サイズが 10 行 1 列として指定されます。

依存関係

このパラメーターを有効にするには、[可変サイズの信号の出力] を選択し、[最大出力サイズ ソース] を [ダイアログ パラメーター] に設定します。

Rst 入力端子を追加にするには、このパラメーターを選択します。詳細については、リセット動作を参照してください。

[圧縮ビット数] および [ビットパックされた値を符号付きとして解釈] パラメーターを使用可能にするには、このパラメーターを選択します。

このパラメーターが選択されると、ブロックは (M×P) ビットを生成します。M は [フレームあたりのサンプル数] パラメーターで指定されたフレームあたりのサンプル数です。P は [圧縮ビット数] パラメーターで指定されたビットパックされたワードのサイズです。P ビットの各グループが整数にパックされます。その結果、M 個の要素を含む整数値の出力ベクトルが生成されます。出力のデータ型は、[出力データ型] によって指定されます。

メモ

整数表現の場合、P ビットの各グループの最上位ビットは MSB と見なされ、最下位ビットは LSB と見なされます。

選択すると、ビットパックされた値が符号付き整数データ値として解釈され、オフにすると、符号なし整数データ値として解釈されます。選択されたときに、最上位ビット (符号ビット) の 1 は負の値を示します。

依存関係

このパラメーターを有効にするには、[ビットパックされた出力を有効にする] を選択します。

出力データ型。[double]、[boolean]、または [Smallest unsigned integer] として指定します。

[ビットパックされた出力を有効にする] をオフにした場合、出力データ型を

double、booleanまたはSmallest unsigned integerとして指定できます。[Output data type] パラメーターをSmallest unsigned integerに設定した場合、出力のデータ型はモデルの [Configuration Parameters] ダイアログ ボックスの [Hardware Implementation] ペインで使用されている設定に基づいて選択されます。[Hardware Implementation] ペインでASIC/FPGAが選択されている場合、出力データ型ufix(1)が理想的な最小 1 ビット サイズになります。その他の選択肢を選んだ場合は、1 ビットに収まるうちで最小の語長となる符号なし整数とされ、通常は対応する文字のサイズとなります (たとえば、uint8)。[ビットパックされた出力を有効にする] を選択した場合、出力データ型を

doubleまたはSmallest unsigned integerとして指定できます。[出力データ型] パラメーターがSmallest unsigned integerに設定されると、出力データ型は、[ビットパックされた値を符号付きとして解釈] パラメーターおよび [圧縮ビット数] パラメーターと、モデルの [コンフィギュレーション パラメーター] ダイアログ ボックスの [ハードウェア実行] ペインで使用されている設定に基づいて選択されます。ASIC/FPGAが [Hardware Implementation] ペインで選択されている場合、出力データ型は [Interpret bit-packed values as signed] パラメーターに基づいてsfix(n)またはufix(n)などの理想的な最小 n ビット サイズになります。他のすべての選択の場合、最も小さな利用可能なワード長が n ビットに十分収まる符号付きまたは符号なし整数になります。

ブロックの特性

データ型 |

|

多次元信号 |

|

可変サイズの信号 |

|

詳細

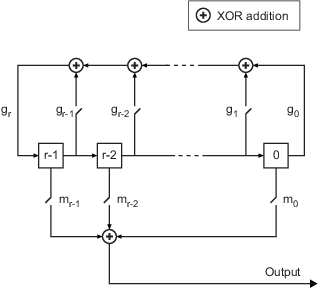

単純なシフト レジスタ発生器 (SSRG) として実装された線形フィードバック シフト レジスタ (LFSR) は、PN シーケンスの生成に使用されます。このタイプのシフト レジスタは、フィボナッチ実装とも呼ばれます。

多項式 g は、シフト レジスタのフィードバック接続を決定します。これは、z の原始バイナリ多項式で、grzr+gr–1zr–1+gr–2zr–2+...+g0 となります。係数 gk=0 ~ r について、係数 gk は、k 番目のレジスタから加算器への接続がある場合に 1 になります。この多項式が原始多項式であるためには、生成多項式の先頭項 gr と定数項 g0 は 1 でなければなりません。各タイム ステップで、発生器内のすべての r レジスタは、シフト レジスタに入ってくる矢印の値に従い、それぞれの値を更新します。加算器は 2 を法とする加算を実行します。LFSR の出力には、m マスク ベクトルにあるすべての接続の合計が反映されます。

g は、[生成多項式] パラメーターによって指定されます。

r の初期値は、[初期状態] パラメーターによって指定されます。

m は PN シーケンスの開始点のシフトを決定します。これは、[出力マスク ベクトル (またはスカラー シフト値)] パラメーターまたは Mask 端子によって指定されます。

次の表は、生成多項式 g(z) = z8 + z2 + 1 に対応するパラメーター値の 2 つのセットを示しています。

| 量 | 例 1 | 例 2 |

|---|---|---|

| g | g1 = [1 0 0 0 0 0 1 0 1] | g2 = [8 2 0] |

| 生成多項式 g の次数 | 8、つまり length(g1)-1 です。 | 8 |

| 初期状態 | [1 0 0 0 0 0 1 0] | [1 0 0 0 0 0 1 0] |

例については、Model PN Sequence Generation with Linear Feedback Shift Registerを参照してください。

この実装では、生成多項式 (g)、初期状態、およびマスク出力が降順で定義されたシフト レジスタを左から右に配置します。具体的には、grzr+gr–1zr–1+gr–2zr–2+...+g0 となります。

文献の結果をモデル化して一致させようとする場合、ソースが同じ規則を使用しているのか、この規則の鏡像を使用して昇順で定義されているのかを識別しなければなりません。

例については、Simulink での入力データの加法スクランブルを参照してください。

PN シーケンスの開始点をシフトするには、[Output mask vector (or scalar shift value)] パラメーターを次のように指定します。

シフトの長さを表す整数。

[Output mask vector (or scalar shift value)] の既定の設定 0 はシフトなしに対応します。単純なシフト レジスタ発生器 の LFSR シフト レジスタの図に示したように、唯一の接続が m0 というラベルの付いた矢印に沿っている場合、シフトはありません。

次の表は、[Output mask vector (or scalar shift value)] を 0 に設定した場合に発生するシフトと正の整数 d に設定した場合に発生するシフトを示しています。

T = 0 T = 1 T = 2 ... T = d T = d+1 Shift = 0 x0 x1 x2 ... xd xd+1 Shift = d xd xd+1 xd+2 ... x2d x2d+1 生成多項式の次数と同じ長さのバイナリ ベクトル。単純なシフト レジスタ発生器の LFSR シフト レジスタの図は、マスク ベクトル m として指定された [Output mask vector (or scalar shift value)] を示しています。このバイナリ ベクトルは N 個の要素をもっていなければなりません。ここで N は生成多項式の次数です。マスク ベクトルを計算するには、関数

shift2maskを使用します。このバイナリ ベクトルは、最大次数 r–1 の z の多項式 mr–1zr–1 + mr–2zr–2 + ... + m1z + m0 に対応します。シフト d に対応するマスク ベクトルは、g(z) を法とする m(z) = zd を表すベクトルです。ここで、g(z) は生成多項式です。

たとえば、生成多項式の次数が 4 である場合、d= 2 に対応するマスク ベクトルは多項式 m(z) = z2 を表す

[0 1 0 0]です。

発生器シーケンスをリセットするにはまず、[Reset on nonzero input] パラメーターを選択して [Rst] 入力端子を有効にする必要があります。リセットがない場合に PN Sequence Generator ブロックが [1 0 0 1 1 0 1 1] を出力すると想定します。次の表は、指定されたパラメーター値に対する PN Sequence Generator ブロック出力に与える影響を示しています。

| リセット信号 | リセット信号の設定 | PN Sequence Generator ブロック | リセット信号と出力信号 |

|---|---|---|---|

| リセットがない |

|

|

|

| スカラーのリセット信号 |

|

|

|

| ベクトルのリセット信号 |

|

|

リセットがない場合、ブロックはシーケンスをリセットせずに出力します。スカラーとベクトルのリセット信号の場合、ブロックはリセット信号 [0 0 0 1 0 0 0 0] を [Rst] 端子への入力とします。リセット信号の 4 番目のビットが 1 で、[サンプル時間] が 1 であるため、ブロックはシーケンス出力を 4 番目のビットでリセットします。

可変サイズの出力の場合、ブロックはスカラーのリセット信号入力のみをサポートします。

次数 r をもつ生成多項式の最大長のシーケンスを生成するには、[Generator polynomial] を次の表の値に設定します。最大のシーケンス長は 2r – 1 です。

| r | 生成多項式 | r | 生成多項式 | r | 生成多項式 | r | 生成多項式 |

|---|---|---|---|---|---|---|---|

| 2 | [2 1 0] | 15 | [15 14 0] | 28 | [28 25 0] | 41 | [41 3 0] |

| 3 | [3 2 0] | 16 | [16 15 13 4 0] | 29 | [29 27 0] | 42 | [42 23 22 1 0] |

| 4 | [4 3 0] | 17 | [17 14 0] | 30 | [30 29 28 7 0] | 43 | [43 6 4 3 0] |

| 5 | [5 3 0] | 18 | [18 11 0] | 31 | [31 28 0] | 44 | [44 6 5 2 0] |

| 6 | [6 5 0] | 19 | [19 18 17 14 0] | 32 | [32 31 30 10 0 | 45 | [45 4 3 1 0] |

| 7 | [7 6 0] | 20 | [20 17 0] | 33 | [33 20 0] | 46 | [46 21 10 1 0] |

| 8 | [8 6 5 4 0] | 21 | [21 19 0] | 34 | [34 15 14 1 0] | 47 | [47 14 0] |

| 9 | [9 5 0] | 22 | [22 21 0] | 35 | [35 2 0] | 48 | [48 28 27 1 0] |

| 10 | [10 7 0] | 23 | [23 18 0] | 36 | [36 11 0] | 49 | [49 9 0] |

| 11 | [11 9 0] | 24 | [24 23 22 17 0] | 37 | [37 12 10 2 0] | 50 | [50 4 3 2 0] |

| 12 | [12 11 8 6 0] | 25 | [25 22 0] | 38 | [38 6 5 1 0] | 51 | [51 6 3 1 0] |

| 13 | [13 12 10 9 0] | 26 | [26 25 24 20 0] | 39 | [39 8 0] | 52 | [52 3 0] |

| 14 | [14 13 8 4 0] | 27 | [27 26 25 22 0] | 40 | [40 5 4 3 0] | 53 | [53 6 2 1 0] |

これらの多項式が表すシフトレジスタ構成の詳細については、Digital Communications by John Proakis を参照してください[1]。

出力更新間の時間は、[フレームあたりのサンプル数] と [サンプル時間] パラメーター値の積に等しくなります。たとえば、[サンプル時間] と [フレームあたりのサンプル数] のそれぞれが 1 に等しい場合、ブロックは毎秒 1 サンプルを出力します。[フレームあたりのサンプル数] を 10 に増やすと、ブロックは 10 秒ごとに 10 行 1 列のベクトルを出力します。このタイミングにより、同等の出力レートが [フレームあたりのサンプル数] パラメーターに依存しないことが確実になります。

参照

[1] Proakis, John G. Digital Communications. 5th ed. New York: McGraw Hill, 2007.

[2] Lee, J. S., and L. E. Miller. CDMA Systems Engineering Handbook. Boston and London. Artech House, 1998.

[3] Golomb, S.W. Shift Register Sequences. Laguna Hills. Aegean Park Press, 1967.

拡張機能

C/C++ コード生成

Simulink® Coder™ を使用して C および C++ コードを生成します。

HDL Coder™ は、HDL の実装および合成ロジックに影響を与える、追加の構成オプションを提供します。

このブロックは 1 つの既定の HDL アーキテクチャをもっています。

| ConstrainedOutputPipeline | 設計内で既存の遅延を移動することによって出力に配置するレジスタの数。分散型パイプラインは、これらのレジスタを再分散しません。既定の設定は |

| InputPipeline | 生成コードに挿入する入力パイプライン ステージの数。分散型パイプラインと制約付き出力パイプラインは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成コードに挿入する出力パイプライン ステージの数。分散型パイプラインと制約付き出力パイプラインは、これらのレジスタを移動できます。既定の設定は |

ブロック上の [Output mask source] として

[入力端子]を選択できます。この場合、Mask入力信号は、データ型ufix1のベクトルでなければなりません。[Reset on nonzero input] を選択した場合、

Rst端子への入力のデータ型はBooleanでなければなりません。double型の出力は、HDL コード生成でサポートされません。その他のすべての出力型 (ビットパックされた出力を含む) はサポートされます。Resettable Synchronous Subsystem (HDL Coder) 内で、このブロックの HDL を生成することはできません。

[トリガー信号をクロックとして使用] オプションを選択した場合、Triggered Subsystem 内でこのブロックの HDL を生成できません。HDL コード生成のための Triggered Subsystem の使用 (HDL Coder)を参照してください。

バージョン履歴

R2006a より前に導入R2020a 以降、Simulink では R2015b より前で利用可能だったバージョンの PN Sequence Generator ブロックは使用できなくなりました。

既存のモデルはソース ブロックは連続する時間サンプルのフレームをフレーム属性を使用せずに出力するで通知されたバージョンの PN Sequence Generator ブロックを読み込むように自動的に更新されます。ブロック転送の詳細については、転送テーブルを使用したライブラリ ブロックの互換性の維持 (Simulink)を参照してください。

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)