このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGA Data Capture Component Generator

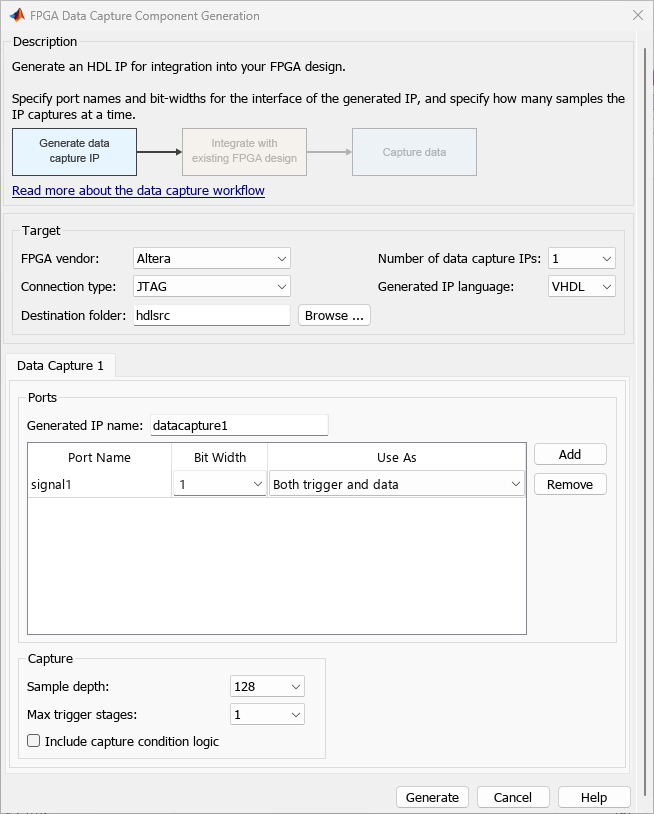

FPGAデータキャプチャコンポーネントの構成と生成

説明

FPGA Data Capture Component Generator ツールは、FPGA 上で実行されている設計からデータをキャプチャするためのコンポーネントを構成および生成します。生成されたコンポーネントは、FPGA から信号データのウィンドウをキャプチャし、そのデータを MATLAB® または Simulink® に返します。

このツールを使用するには、既存の HDL 設計と FPGA プロジェクトが必要です。信号をキャプチャするために、HDL Verifier™ は、HDL プロジェクトに統合し、設計の残りの部分とともに FPGA に展開する必要がある IP コアを生成します。

このツールの Generate ボタンは、次のコンポーネントを生成します。

FPGA 設計に統合するための HDL IP コア。キャプチャしてトリガーとして使用する信号を接続し、クロックとクロック イネーブルを接続します。

生成されたファイルのリストと次の手順の指示を含む生成レポート。

キャプチャ パラメータを設定し、MATLAB ワークスペースにデータをキャプチャするためのツール。FPGA Data Capture を参照してください。

hdlverifier.FPGADataReaderSystem object™ のカスタマイズされたバージョンであり、データの設定とキャプチャを行うための代替のプログラム的な方法を提供します。カスタマイズされた FPGA Data Reader ブロックを含む Simulink モデル。DSP System Toolbox™ ライセンスをお持ちの場合、このモデルはキャプチャした信号を Logic Analyzer 波形ビューアにストリーミングします。それ以外の場合、Scope ブロックは信号を表示します。

generatedIPName_gensettings.matgeneratedIPNamegenerateFPGADataCaptureIP関数の入力引数として指定します。

ワークフローの概要については、データキャプチャワークフロー を参照してください。

JTAG 接続を介した Xilinx® FPGA ボードでは、複数の FPGA データ キャプチャ IP を使用して、異なるクロック ドメインからデータをキャプチャし、FPGA 設計をデバッグできます。複数の FPGA データ キャプチャの詳細については、非同期データのキャプチャ を参照してください。

FPGA Data Capture Component Generator を開く

MATLAB コマンド プロンプトで、このコマンドを入力します。

generateFPGADataCaptureIP

最新の設計のパラメータを再ロードするには、restore 引数を使用します。

generateFPGADataCaptureIP('restore',true);すでに生成して MAT ファイルに保存した設計のパラメータを再ロードするには、matFile 引数を使用します。

generateFPGADataCaptureIP('datacapture1_gensettings.mat');datacapture1例

パラメーター

バージョン履歴

R2017a で導入