このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

非同期データのキャプチャ

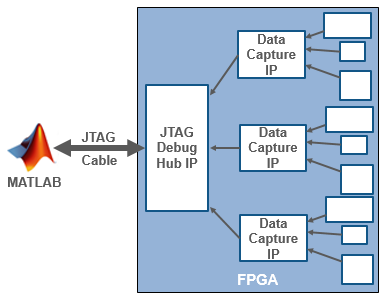

複数の FPGA データ キャプチャ IP を使用して、異なるクロック ドメインからデータをキャプチャし、FPGA 設計をデバッグします。データ キャプチャ IP は、FPGA から複数の信号データ ウィンドウをキャプチャし、JTAG インターフェイスを介してデータを MATLAB® に返します。

メモ

JTAG インターフェイスを介して Xilinx® デバイスをターゲットとする場合にのみ、複数のデータ キャプチャ IP を有効にできます。

FPGA Data Capture Component Generator ツールを使用して、複数のデータ キャプチャ IP を生成します。addFPGADataCaptureToVivado 関数を使用して、生成された IP を JTAG デバッグ ハブ IP とともに Vivado® ユーザー リポジトリに追加します。JTAG デバッグ ハブ IP は、ホスト マシン上の MATLAB および FPGA デザイン内の各データ キャプチャ IP と通信します。次に、非同期データをキャプチャするには、これらの IP を手動で Vivado プロジェクトに統合し、デザインの残りの部分とともに FPGA に展開します。

データキャプチャIPの設定と生成

FPGA Data Capture Component Generator ツールを使用して、データ キャプチャ IP を構成および生成します。ツール内:

Number of data capture IPs を 1 より大きい値に設定します。

Generated IP name パラメータを使用して、各データ キャプチャ IP に一意の名前を指定します。

各データ キャプチャ IP のポート名とサイズを指定します。これらのポートは、キャプチャする信号と、各キャプチャのトリガーとして使用する信号に接続します。

返すサンプル数、トリガー ステージの最大数、各データ キャプチャ IP のキャプチャ条件ロジックを含めるかどうかを指定します。

[生成] をクリックします。

ツールは、指定された宛先フォルダーに次のデータ キャプチャ コンポーネントを生成します。

データキャプチャIPに特有

FPGA 設計に統合するためのパッケージ化された IP コア。各 IP コアには以下が含まれます。

キャプチャする信号やトリガー条件の一部として使用する信号ごとのポート。

各信号に対して要求したサンプル数をキャプチャするためのメモリ。

JTAG デバッグ ハブ IP と通信するためのインターフェイス ロジック (BSCAN 従属インターフェイス)。

実行時に構成できるトリガーおよびキャプチャ条件ロジック。

FPGA からのデータ フローを制御するためのキャプチャ準備完了信号。

JTAG デバッグ ハブ IP からデータ キャプチャ IP を制御するための FDC_active 信号。

生成されたファイルのリストと次の手順の指示を含む生成レポート。

キャプチャ パラメータを設定し、MATLAB ワークスペースにデータをキャプチャするためのツール。

データ キャプチャ System object™ のカスタマイズされたバージョン。データの構成とキャプチャを行うための代替のプログラム的な方法を提供します。

generatedIPName_gensettings.matgeneratedIPName

すべてのデータキャプチャIPに共通

すべてのデータ キャプチャ IP のキャプチャ パラメータを設定し、複数のデータ信号を MATLAB ワークスペースにキャプチャするためのツール。

生成されたすべてのデータ キャプチャ IP のビルド パラメータを保持する MAT ファイル

multipleDatacaptureIPs_gensettings.mat。次の反復で同じデザインを再ロードするには、この MAT ファイルをgenerateFPGADataCaptureIP関数の入力引数として指定します。

生成された IP を Vivado プロジェクトに追加する

addFPGADataCaptureToVivado 関数を使用して、生成されたパッケージ化された IP コアと JTAG デバッグ ハブ IP を Vivado ユーザー リポジトリに追加します。

Vivado プロジェクトを作成します。

指定されたフォルダー内の HDL IP を指定された Vivado プロジェクトに追加します。

addFPGADataCaptureToVivado("vivadoProjectPath",DataCaptureIPFolder="destinationFolder");ここで、

vivadoProjectPathdestinationFolderたとえば、次のコマンドは、

hdlsrcフォルダー内のデータ キャプチャ IP と JTAG デバッグ ハブ IP をC:\test_design_zc706\hdl_prj\vivado_ip_prj\vivado_prj.xprVivado プロジェクトに追加します。addFPGADataCaptureToVivado("C:\test_design_zc706\hdl_prj\vivado_ip_prj\vivado_prj.xpr", ... DataCaptureIPFolder="hdlsrc");

生成されたIPをVivadoデザインに統合する

FPGA データをキャプチャするには、データ キャプチャ IP を Vivado デザインに統合します。ホスト コンピューターは JTAG デバッグ ハブ IP と通信するため、すべてのデータ キャプチャ IP をハブ IP に接続する必要があります。IP を統合するには、生成レポートの指示に従います。

Vivado プロジェクトを開きます。

データ キャプチャ IP と JTAG デバッグ ハブ IP を Vivado ブロック デザインに追加します。

キャプチャとトリガーを要求した信号にデータ キャプチャ IP を接続します。

各データ キャプチャ IP の BSCAN 従属 (BSCAN_S) インターフェイスを JTAG デバッグ ハブ IP の BSCAN マネージャー (BSCAN_M) インターフェイスに接続します。

JTAG デバッグ ハブ IP の複数の BSCAN マネージャー インターフェイスを有効にするには、ハブ IP で DataCapture IP の数 を必要な値に設定します。

Versal® のみ — Vivado Tcl コンソールでこのコマンドを実行して、JTAG デバッグ ハブ IP を Xilinx Versal プラットフォーム CIPS IP の BSCAN_USER2 インターフェイスに接続します。

BSCAN_USER2 インターフェイスを有効にするには、CIPS IP で PL BSCAN1 インターフェイスを有効にします。source ./insertVersalFPGADataCaptureIP.tcl

各データ キャプチャ IP のデータ キャプチャ ID が一意であり、対応するデータ キャプチャ System object の

DataCaptureIDと一致していることを確認します。データ キャプチャ ID を更新するには、データ キャプチャ IP で、データ キャプチャ ID を必要な値に設定します。

データ キャプチャ IP の

clk、clk_enable、および入力データ ポートを接続して、ブロック設計を完了します。

プロジェクトをコンパイルし、JTAG ケーブルを介して新しいイメージで FPGA をプログラムします。

非同期データのキャプチャ

JTAG デバッグ ハブ IP は、FPGA ボードとホスト コンピューター間の JTAG ケーブルを介して通信します。JTAG ケーブルが接続されていることを確認してください。非同期データをキャプチャする前に、FPGA Data Capture ツールで、キャプチャするデータのデータ型、キャプチャするウィンドウの数、データをキャプチャするタイミングを指定するトリガー条件、各データ キャプチャ IP に対してキャプチャするデータを指定するキャプチャ条件を設定できます。

トリガー - デザインが FPGA 上で実行されている場合、最初に JTAG デバッグ ハブ IP は指定したトリガー条件を待機します。1 つ以上の信号に一致する特定の値によってトリガー条件を定義します。トリガーが検出されると、ロジックは指定された信号をバッファにキャプチャし、JTAG インターフェイスを介してデータをホスト マシンに返します。

キャプチャ条件 - バッファ サイズを最大限に活用し、有効なデータのみをキャプチャするために、キャプチャ条件を定義することもできます。トリガー条件を定義するのと同じ方法でキャプチャ条件を定義します。トリガーが検出され、キャプチャ条件が満たされると、ロジックは指定された信号の有効な値のみをキャプチャします。

これらのオプションを構成してデータをキャプチャするには、次の操作を実行します。

MATLAB でこのコマンドを実行して、FPGA Data Capture ツールを開きます。

launchMultipleDataCaptureApp

各データ キャプチャ IP のトリガー、キャプチャ条件、およびデータ タイプ パラメータを設定します。次に、MATLAB ワークスペースにデータをキャプチャします。

各データ キャプチャ IP に対して生成されたデータ キャプチャ System object を使用します。

各データ キャプチャ System object と対話できる

dataCaptureHubオブジェクトを作成します。hub = dataCaptureHub;

addDataCaptureIP関数を使用して、すべてのデータ キャプチャ System object をハブ オブジェクトに追加します。hub.addDataCaptureIP("dataCaptureSystemObjectPath");ここで、

dataCaptureSystemObjectPathたとえば、次のコマンドは、

datacapture1データ キャプチャ IP の System object をhubオブジェクトに追加します。hub.addDataCaptureIP("datacapture1\datacapture1.m");

各データ キャプチャ IP の System object のオブジェクト関数とプロパティを使用して、データ タイプ、トリガー条件、キャプチャ条件を設定し、ハブ オブジェクトを呼び出してデータをキャプチャします。

データをキャプチャして MATLAB ワークスペースにインポートすると、データを分析、検証、表示できます。