このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

generateFPGADataCaptureIP

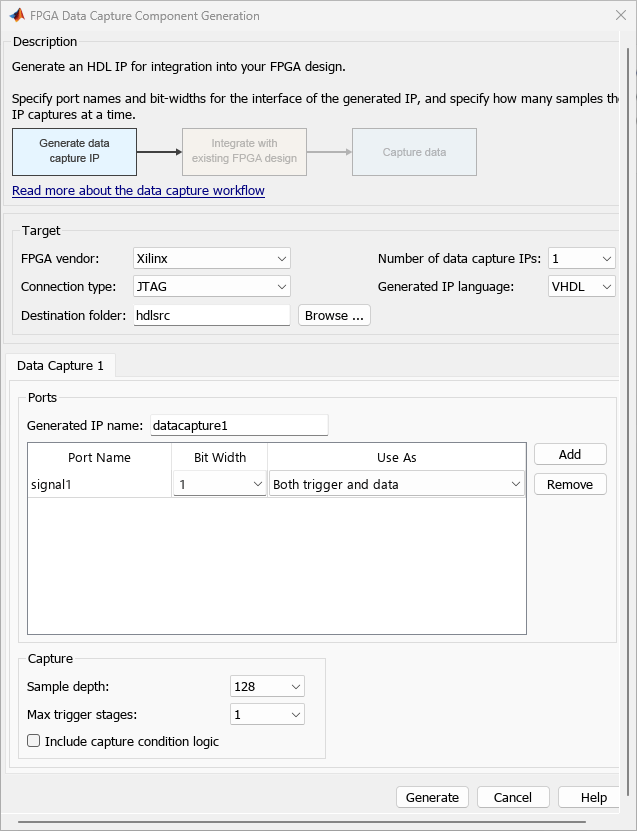

オープンFPGAデータキャプチャコンポーネントジェネレータ

構文

説明

generateFPGADataCaptureIP は FPGA Data Capture Component Generator ツールを開きます。

generateFPGADataCaptureIP(' は FPGA Data Capture Component Generator ツールを開き、最新の設計のパラメータを再読み込みします。restore',true)

generateFPGADataCaptureIP( は FPGA Data Capture Component Generator ツールを開き、matFile)matFile ですでに生成して保存した設計のパラメータを再読み込みします。