このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGA データ キャプチャを使用して Intel FPGA ボードからオーディオ信号をキャプチャする

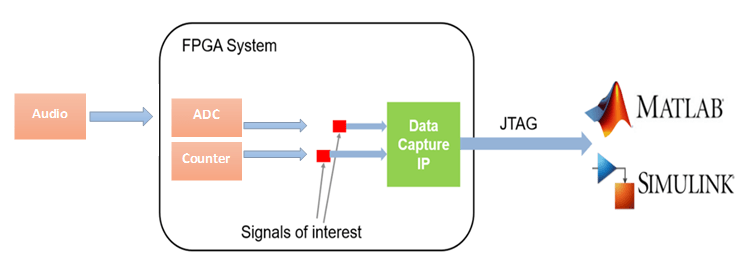

この例では、既存の HDL コードで FPGA データ キャプチャを使用して FPGA 内部信号を読み取る方法を示します。オーディオ信号をサンプリングするためのオンチップのアナログ-デジタル コンバーター (ADC) を実装する既存の FPGA 設計から始めます。ADC IP は、制御用の Avalon® メモリマップ (MM) スレーブ インターフェイスと、データ出力用の Avalon ストリーミング インターフェイスを公開します。この FPGA 設計には、ADC を起動するための Avalon MM マスターがすでに含まれています。FPGA データ キャプチャ機能を使用して、Avalon ストリーミング インターフェイスから ADC 出力データを MATLAB® ワークスペースに収集します。

要件と前提条件

Intel Quartus® Prime ソフトウェア(サポートされているバージョンは サポートされているEDAツールとハードウェア に記載されています)

Arrow® DECA MAX® 10 FPGA開発ボード

FPGA開発ボードのセットアップ

1. 電源スイッチがオフになっていることを確認してください。

2. FPGA 開発ボードとホスト コンピューターの間に JTAG ダウンロード ケーブルを接続します。

3. (オプション) 3.5 mm オーディオ ケーブルを使用して、FPGA ボードのライン入力ポートを携帯電話などのオーディオ ソースに接続します。この手順をスキップすると、キャプチャされたデータはランダムなノイズになります。

サンプルリソースを準備する

Intel Quartus をセットアップします。この例では、Intel Quartus 実行可能ファイルがファイル C:\altera\18.0\quartus\bin\quartus.exe にあることを前提としています。実行可能ファイルの場所が異なる場合は、代わりにパスを使用してください。

hdlsetuptoolpath('ToolName','Altera Quartus II', ...

'ToolPath','C:\altera\18.0\quartus\bin\quartus.exe');FPGAデータキャプチャコンポーネントを生成する

MATLAB でこのコマンドを実行して、FPGA Data Capture Component Generator ツールを起動します。

generateFPGADataCaptureIP

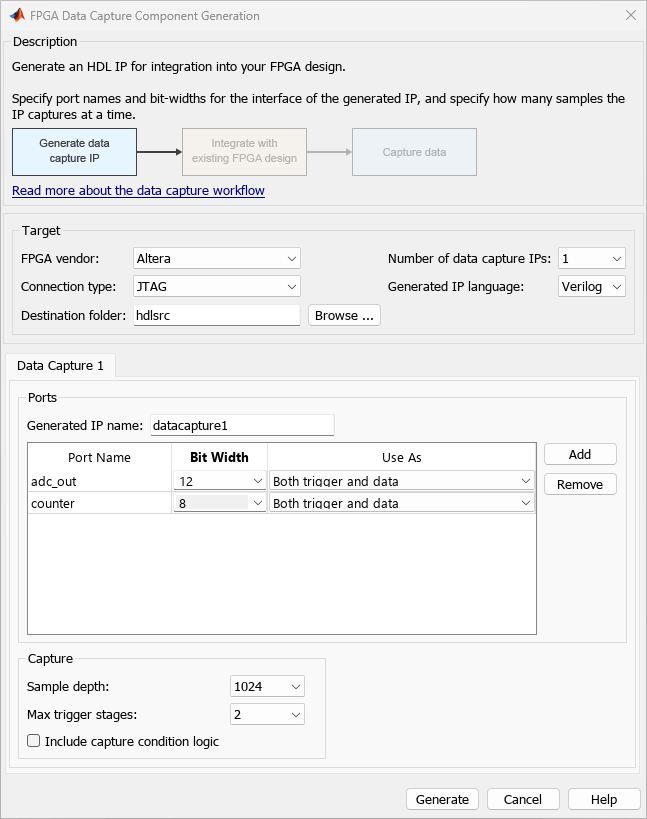

この例では、オーディオ システムの既存の HDL 設計からの 2 つの信号を監視します。12 ビットの adc_out と 8 ビットの counter。adc_out 信号は、オーディオ ライン入力信号のデジタル サンプルです。次の信号 counter は 8 ビットのフリーランニング カウンターです。これら 2 つの信号で動作するようにデータ キャプチャ コンポーネントを構成するには、次の手順に従います。

1. FPGA ベンダー を Altera に設定します。

2. 生成された IP 言語 を Verilog に設定します。

3. 追加 ボタンを 1 回クリックして、ポート テーブルに 1 行追加します。

4. 最初の信号の名前を adc_out に変更し、2 番目の信号の名前を counter に変更します。

5. 2 つの信号のビット幅をそれぞれ 12 と 8 に変更します。

6. サンプル深度を1024に設定します。この値は、トリガーが検出されるたびにデータ キャプチャ ツールが MATLAB に返す各信号のサンプル数です。

7. 最大トリガー ステージ を 2 に設定します。この値は、複数のトリガー条件を提供するためにデータ キャプチャ中に追加できるトリガー ステージの最大数です。

この図はこれらのツール設定を示しています。

FPGA データ キャプチャ コンポーネントを生成するには、生成 をクリックします。生成の結果はレポートに表示されます。

FPGAデータキャプチャHDL IPの統合

生成された HDL IP コアをサンプル FPGA デザインに含める必要があります。生成されたレポートからモジュール インスタンス コードをコピーできます。この例では、生成された HDL IP を ADC 出力と 8 ビットのフリーランニング カウンターに接続します。

この例に付属する adc_top.v ファイルを開きます。このコードのコメントを解除します。

datacapture1 u0 (

.clk(adc_clk),

.clk_enable(adc_valid),

.ready_to_capture(),

.adc_out(adc_out),

.counter(counter[7:0]));adc_top.v を保存し、変更した FPGA デザインをコンパイルし、次の Tcl スクリプトを使用して FPGA プログラミング ファイルを作成します。

system('quartus_sh -t adc_deca_max10.tcl &')この例に含まれる Tcl スクリプトは、次の手順を実行します。

1. 新しい Quartus プロジェクトを作成します。

2. サンプル HDL ファイルと生成された FPGA データ キャプチャ HDL ファイルをプロジェクトに追加します。

3. デザインをコンパイルします。

4. FPGA をプログラムします。

次のステップに進む前に、Quartus プロセスが正常に終了するまで待機します。このプロセスには約 5 ~ 10 分かかります。

データのキャプチャ

FPGA データ キャプチャ コンポーネントが生成されるディレクトリに移動します。

cd hdlsrc

FPGA Data Capture ツールを起動します。このツールは、データ キャプチャ信号用にカスタマイズされています。

launchDataCaptureApp

データ キャプチャを開始するには、[データのキャプチャ] をクリックします。データ キャプチャ オブジェクトは、FPGA からキャプチャされたデータの 1 つのバッファーを要求します。デフォルト設定では、トリガー条件を待たずにすぐにキャプチャします。

キャプチャされたデータは、MATLAB ワークスペース内の構造体 dataCaptureOut に保存されます。DSP System Toolbox™ ソフトウェアをお持ちの場合は、キャプチャされたデータは ロジック アナライザー ツールで信号波形としても表示されます。

トリガーを使用したデータキャプチャの範囲の限定

特定のイベントの前後で FPGA からデータをキャプチャするには、FPGA データ キャプチャ ツールでトリガー条件を設定できます。たとえば、カウンターが特定の値に達した後にのみオーディオ データをキャプチャします。

トリガーステージの数を1に設定します。トリガー ステージ 1 セクションで、信号 を counter に設定します。+ ボタンをクリックして、このトリガー信号を有効にします。対応するトリガー条件値 (値) を 10 に設定します。トリガー モードは自動的に トリガー時 に変更されます。この変更により、FPGA はデータをキャプチャして返す前にトリガー条件を待機するように指示されます。この図はこれらのツール設定を示しています。

もう一度 データのキャプチャ をクリックします。今回は、データ キャプチャ IP は、カウンターが 10 になったことを検出したときにキャプチャされた 1024 個のサンプルを返します。

他のビットに関係なく、トリガー値の特定のビットのデータを FPGA からキャプチャするには、ビットマスクされた値を使用してトリガー条件を設定できます。

たとえば、カウンターの 7 番目のビットが 1 のときのみオーディオ データをキャプチャするには、この図に示すように、トリガー条件値 (値) を 0bX1XXXXXX に設定します。

もう一度 データのキャプチャ をクリックします。

データキャプチャIPは、[64, 127]から[192, 255]の範囲のカウンター値のオーディオデータをキャプチャするようにトリガーします。

複数のイベント発生をキャプチャする

FPGA から繰り返し発生するイベントをキャプチャするには、FPGA データ キャプチャ ツールで キャプチャ ウィンドウの数 を構成します。

たとえば、8 つの異なる時間スロットでオーディオ データをキャプチャするには、キャプチャ ウィンドウの数 を 8 に設定します。この図は更新されたツール設定を示しています。

データのキャプチャをクリックします。データ キャプチャ IP は、それぞれ 128 サンプルの 8 つのウィンドウを返します。合計サンプル深度は 1024 になります。

Window depth = Sample depth/Number of capture windows;

ロジック アナライザー ツールでは、この結果がトリガーの 8 回の発生として表示され、オーディオ データはそれぞれ 128 サンプル記録されます。

信号 Capture Window と Trigger Position は、それぞれ対応するウィンドウ番号とトリガー位置を示します。

複数のトリガーステージでデータをキャプチャする

このシナリオでは、複数のトリガー ステージで一連のトリガー条件を指定してデータをキャプチャする方法について説明します。複数のトリガー条件でデータをキャプチャするには、FPGA データ キャプチャ ツールで トリガー ステージ数 を 1 より大きい値に設定する必要があります。

たとえば、カウンター値が 5 クロック サイクルで 0 から 5 に達したときにオーディオ データをキャプチャするには、次の手順に従います。

1. トリガーステージの数を2に設定します。

2. トリガー ステージ 1 セクションで、信号 を counter に設定します。+ ボタンをクリックして、このトリガー信号を有効にします。対応するトリガー条件値 (値) を 0 に設定します。

3. トリガー ステージ 2 セクションで、信号を counter に設定します。+ ボタンをクリックして、このトリガー信号を有効にします。対応するトリガー条件値 (値) を 5 に設定します。トリガー タイムアウト を選択し、5 に設定します。

図は更新されたツール設定を示しています。

データのキャプチャをクリックします。データ キャプチャ IP は、トリガー ステージ 1 で検出されたトリガー条件に続いて、5 クロック サイクル以内にトリガー ステージ 2 でトリガー条件を検出すると、1024 個のサンプルをキャプチャします。

参考

FPGA Data Capture Component Generator | FPGA Data Capture