このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGA Data Capture

ライブ FPGA からデータを MATLAB ワークスペースにインタラクティブにキャプチャします

説明

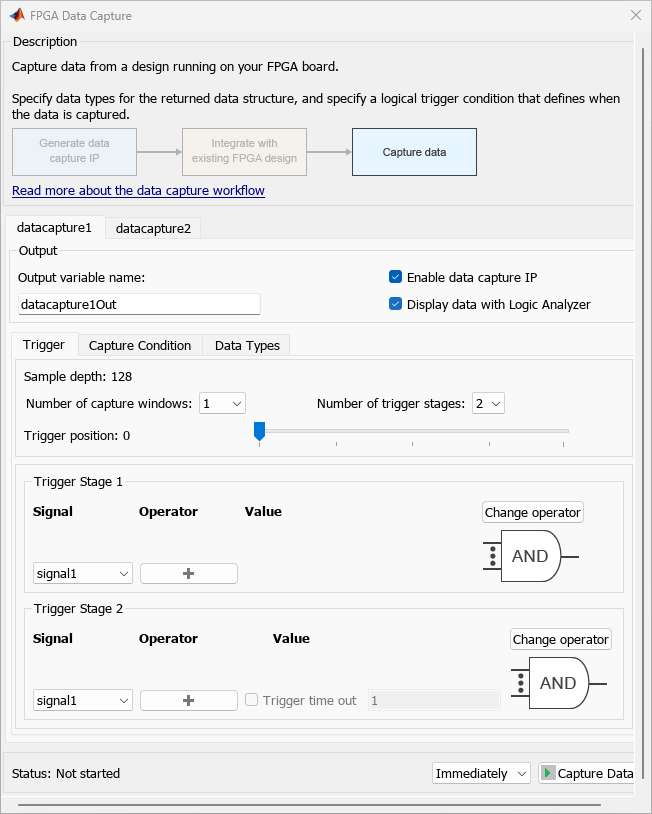

FPGA Data Capture ツールは、FPGA 上で実行されている設計からデータをキャプチャし、それを MATLAB® ワークスペースに返します。返される値のデータ型を構成し、キャプチャ ウィンドウの数とトリガー ステージの数を指定し、データをキャプチャするタイミングを制御するトリガー条件を設定し、キャプチャするデータを制御するキャプチャ条件を設定できます。

このツールを使用する前に、FPGA Data Capture Component Generator ツールを使用してカスタマイズされたデータ キャプチャ コンポーネントを生成する必要があります。生成された IP コアをプロジェクトに統合し、FPGA にデプロイする必要もあります。このツールは、JTAG または Ethernet ケーブルを介して FPGA と通信します。ボードとホスト コンピューターの間に必要なケーブルが接続されていることを確認します。

このツールは、生成された hdlverifier.FPGADataReader System object™ のラッパーです。FPGA Data Capture ツールは、ワークスペース内の変数 fpgadc_obj を定義します。この変数がすでに存在する場合、ツールは既存のオブジェクトを使用して開き、そのオブジェクトへの変更を保存します。

ワークフローの概要については、データキャプチャワークフロー を参照してください。

JTAG 接続を介した Xilinx® FPGA ボードでは、複数の FPGA データ キャプチャ IP を使用して、異なるクロック ドメインからデータをキャプチャし、FPGA 設計をデバッグできます。複数の FPGA データ キャプチャの詳細については、非同期データのキャプチャ を参照してください。

FPGA Data Capture を開く

MATLAB コマンド プロンプト: 「

launchDataCaptureApp」と入力します。この関数は、単一のデータ キャプチャ IP 用の FPGA Data Capture ツールを開きます。launchDataCaptureApp関数は、destinationFolderdestinationFolder\generatedIPNamedestinationFoldergeneratedIPNameMATLAB コマンド プロンプト: 「

launchMultipleDataCaptureApp」と入力します。この関数は、複数のデータ キャプチャ IP 用の FPGA Data Capture ツールを開きます。launchMultipleDataCaptureApp関数は、destinationFolderdestinationFolder

例

パラメーター

バージョン履歴

R2017a で導入