このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGA Data Reader

ライブFPGAからSimulinkモデルにデータをキャプチャする

ライブラリ:

Generated

説明

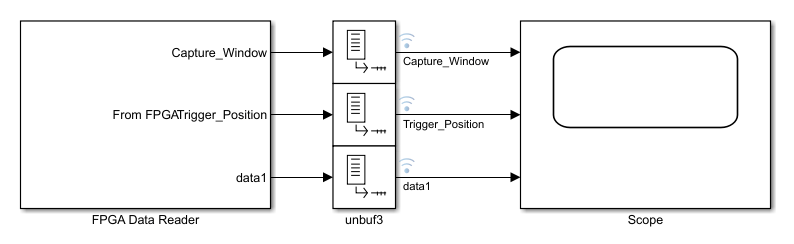

FPGA Data Reader ブロックは、FPGA 上で生成された IP コアと通信し、キャプチャしたデータを Simulink® に返します。

このブロックを実行する前に、カスタマイズされたデータ キャプチャ コンポーネントを生成する必要があります。生成された HDL IP コアをプロジェクトに統合し、FPGA にデプロイします。ブロックは JTAG または Ethernet ケーブルを介して FPGA と通信します。ボードとホスト コンピューターの間に必要なケーブルが接続されていることを確認します。

ワークフローの概要については、データキャプチャワークフロー を参照してください。

デフォルトでは、FPGA Data Capture Component Generator ツールはこのブロックとスコープを含むデータ キャプチャ モデルを生成します。DSP System Toolbox™ ライセンスをお持ちの場合、キャプチャされたデータは Logic Analyzer ツールにストリーミングされます。それ以外の場合、Scope ブロックにはキャプチャされたデータが表示されます。分析、検証、表示のためにモデルに他のブロックを追加できます。

端子

FPGA Data Reader ブロックの出力ポートは、FPGA Data Capture Component Generator でキャプチャするように要求した信号に対応します。ブロック パラメータから開かれた Signal and Trigger Editor 内のこれらのポートのデータ型を設定します。

出力

この出力ポートは現在のキャプチャ ウィンドウを示します。この出力ポートの値は、1 から Sample depth パラメータの値までの整数です。

この出力ポートは、キャプチャ バッファ内のトリガー検出クロック サイクルの位置を示します。

パラメーター

メイン

ブロックは、時間ステップごとに 1 フレームのデータを返します。フレームは、各信号のキャプチャ バッファー全体です。各フレームには、生成時に指定された Sample depth 値が含まれます。デフォルトのサンプル時間では、各フレームを単一のサンプルにバッファリング解除し、サンプル時間は 1 になります。

トリガー

このパラメーターは読み取り専用です。生成時に指定した値が反映されます。

キャプチャする繰り返し回数を指定します。この値は Sample depth までの 2 の累乗でなければなりません。window depth は Sample depth / Number of capture windows として定義されます。十分なバッファリングを可能にするために、Sample depth を設定するときは Number of capture windows を考慮してください。

トリガーステージの数を指定します。この値は 1 から M までの整数である必要があります。M は、FPGA Data Capture Component Generator ツールの 最大トリガー ステージ パラメータによって設定されます。Max trigger stages パラメータを指定するときは、データをキャプチャするためのトリガー条件を構成する予定のトリガー ステージの最大数を考慮してください。

デフォルトでは、トリガーが検出されたクロック サイクルは、キャプチャ バッファーの最初のサンプルになります。キャプチャ バッファ内のトリガー検出サイクルの相対位置を変更できます。デフォルト以外のトリガー位置は、トリガーが発生する前にいくつかのサンプルがキャプチャされることを意味します。このパラメータは、0 から window depth –1 までの任意の数値に設定できます。トリガー位置が window depth –1 に等しい場合、最後のサンプルはトリガーが発生したサイクルに対応します。Number of capture windows が 1 より大きい場合、同じトリガー位置がすべてのウィンドウに適用されます。トリガーを参照してください。

このパラメーターは読み取り専用です。生成時に指定した信号名は、下部のドロップダウン メニューに表示されます。トリガー条件に信号を追加するには、+ ボタンをクリックします。

信号を比較するには、==、!=、<、>、<=、または >= のいずれかの演算子を選択します。X または x (don't care 値) を含む信号を比較するには、== または != 演算子を指定します。

トリガー条件は、1 つ以上の信号の値の比較で構成できます。このパラメータは、各信号に一致する値を指定します。

マルチビット信号の場合は、信号に関連付けられたデータ型の範囲内で 10 進数、2 進数、または 16 進数の値を指定します。16 進数または 2 進数の値を指定する場合、X または x (don't care 値) の組み合わせで値を指定して、ビット マスクを有効にすることができます。値を比較する際、トリガー条件は X または x の場所の値を破棄し、出力を提供します。

読みやすくするためにビットのグループを区切るには、ビット間に _ を使用します。たとえば、32 ビットのバイナリ値は 0b1010_XXXX_1011_XXXX_1110_XXXX_1111XXXX として表すことができ、32 ビットの 16 進値は 0xAB_CDEXFX として表すことができます。

boolean 信号の場合は、レベルまたはエッジ条件を選択します。トリガーを参照してください。

このパラメータはロジック ゲート アイコンで示されます。Change operator ボタンをクリックすると、AND と OR が切り替わります。

トリガー条件は、1 つ以上の信号の値の比較で構成できます。これらの値の比較を 1 種類の論理演算子のみで組み合わせます。A、B、C の 3 つの信号がトリガー条件を構成するとします。次のオプションがあります。

A == 10 AND B == 'Falling edge' AND C == 0

A == 10 OR B == 'Falling edge' OR C == 0

この多くのデータ キャプチャ IP コア クロック サイクル内で、このパラメータを有効にするトリガー ステージでトリガー条件が発生する必要があります。要件に応じて、1 から 65,536 までの任意の整数値を指定できます。トリガー ステージでトリガー タイムアウトを有効にするには、このパラメータを選択します。Trigger Stage 1 ではトリガー タイムアウトは許可されません。

トリガー条件が有効になっているが、HDL IP コアがその条件を検出しない場合、データ キャプチャ要求はこの秒数後にタイムアウトします。Simulink にはデータが返されません。

捕獲条件

データ キャプチャ IP コアでキャプチャ条件ロジックを有効にするには、このパラメータを選択します。キャプチャ条件ロジックを有効にして、キャプチャ条件を使用して FPGA からキャプチャするデータを制御します。データ キャプチャ IP コアは、各クロック サイクルでキャプチャ条件を評価し、キャプチャ条件を満たすデータのみをキャプチャします。取得条件の詳細については、捕獲条件を参照してください。

依存関係

このパラメータを有効にするには、FPGA Data Capture Component Generator ツールで Include capture condition logic を選択します。

このパラメーターは読み取り専用です。生成時にトリガーとして指定した信号名は、下部のドロップダウン メニューに表示されます。+ ボタンをクリックして、キャプチャ条件に信号を追加します。

依存関係

このパラメータを有効にするには、Enable capture condition logic を選択します。

信号を比較するには、==、!=、<、>、<=、または >= のいずれかの演算子を選択します。X または x (don't care 値) を含む信号を比較するには、== または != 演算子を指定します。

依存関係

このパラメータを有効にするには、Enable capture condition logic を選択します。

キャプチャ条件は、1 つ以上の信号の値の比較で構成できます。このパラメータは、各信号に一致する値を指定します。

マルチビット信号の場合は、信号に関連付けられたデータ型の範囲内で 10 進数、2 進数、または 16 進数の値を指定します。16 進数または 2 進数の値を指定する場合、X または x (don't care 値) の組み合わせで値を指定して、ビット マスクを有効にすることができます。値を比較する際、キャプチャ条件は X または x の場所の値を破棄し、出力を提供します。

読みやすくするためにビットのグループを区切るには、ビット間に _ を使用します。たとえば、32 ビットのバイナリ値は 0b1010_XXXX_1011_XXXX_1110_XXXX_1111XXXX として表すことができ、32 ビットの 16 進値は 0xAB_CDEXFX として表すことができます。

boolean 信号の場合は、レベルまたはエッジ条件を選択します。捕獲条件を参照してください。

依存関係

このパラメータを有効にするには、Enable capture condition logic を選択します。

このパラメータはロジック ゲート アイコンで示されます。Change operator ボタンをクリックすると、AND と OR が切り替わります。

キャプチャ条件は、1 つ以上の信号の値の比較で構成できます。これらの値の比較を 1 種類の論理演算子のみで組み合わせます。組み合わせ演算子を混在させることはできません。捕獲条件を参照してください。

依存関係

このパラメータを有効にするには、Enable capture condition logic を選択します。

データ型

このパラメーターは読み取り専用です。これは、Capture_Window 出力ポートの名前、Trigger_Position 出力ポートの名前、および生成時に指定した信号名を反映します。

このパラメーターは読み取り専用です。生成時に指定した値が反映されます。

Data Type メニューには、キャプチャされた信号のビット幅に一致するデータ タイプの提案が表示されます。このサイズは、生成された IP のポートに対して指定した幅です。このフィールドに入力してカスタム データ型を指定できます。信号が 8、16、または 32 ビットの場合、デフォルトは uint です。信号が 1 ビットの場合、デフォルトは boolean です。信号の幅が異なる場合、デフォルトは numerictype(0,bitWidth,0) になります。

ブロックは、信号ビット幅に応じて、次のデータ型をサポートします: boolean、uint8、int8、uint16、int16、half、uint32、int32、single、uint64、int64、double、および numerictype。

開発ボードに複数の FPGA または複数の JTAG 接続がある場合、データ キャプチャ ソフトウェアは JTAG チェーン内の FPGA の位置を検出できません。データ キャプチャ IP コアを含む FPGA を見つけるには、これらの詳細パラメータを指定します。

詳細設定

データキャプチャに使用される JTAG ケーブルの名前。文字ベクトルとして指定されます。ボードが同じタイプの 2 つの JTAG ケーブルに接続されている場合は、このパラメータを使用します。

複数の JTAG ケーブルがホスト コンピューターに接続されている場合は、このパラメーターを指定します。指定されていない場合、FPGA Data Reader ブロックは次の順序で JTAG ケーブル タイプを自動検出します。

FPGA Data Reader ブロックは最初に Digilent® ケーブルを検索します。

Digilent JTAG ケーブルが見つからない場合は、FTDI ケーブルを検索します。

同じタイプのケーブルが 2 本見つかった場合、オブジェクトはエラーを返します。解決するにはこのパラメータを設定します。

異なるタイプのケーブルが 2 本見つかった場合は、Digilent ケーブルが優先されます。FTDI ケーブルを使用するには、このパラメータを

FTDIに設定します。

依存関係

このパラメータを有効にするには、FPGA Data Capture Component Generator ツールで、FPGA vendor を Xilinx に、Connection type を JTAG に設定します。

JTAG スキャン チェーン内の FPGA の位置。正の整数として指定されます。

依存関係

このパラメータを有効にするには、FPGA Data Capture Component Generator ツールで、FPGA vendor を Xilinx に、Connection type を JTAG に設定します。

FPGA 前の命令レジスタの長さの数。負でない整数として指定します。

依存関係

このパラメータを有効にするには、FPGA Data Capture Component Generator ツールで、FPGA vendor を Xilinx に、Connection type を JTAG に設定します。

FPGA 後の命令レジスタの長さの数。負でない整数として指定されます。

依存関係

このパラメータを有効にするには、FPGA Data Capture Component Generator ツールで、FPGA vendor を Xilinx に、Connection type を JTAG に設定します。

JTAG クロック周波数を MHz 単位で指定します。Xilinx FPGA の場合、JTAG クロック周波数は 33 MHz または 66 MHz です。JTAG 周波数は、ケーブルの種類と FPGA ボードでサポートされる最大クロック周波数によって異なります。

依存関係

このパラメータを有効にするには、FPGA Data Capture Component Generator ツールで、FPGA vendor を Xilinx に、Connection type を JTAG に設定します。

FPGA または SoC ボード上のイーサネット ポートのインターネット プロトコル (IP) アドレスをドット区切りの 4 つの値として指定します。デバイスの IP アドレスは、3 つのドットで区切られた 0 ~ 255 の範囲の整数で構成される 4 つの数字のセットである必要があります。

依存関係

このパラメータを有効にするには、FPGA Data Capture Component Generator ツールで、FPGA vendor を Xilinx に設定し、Connection type を PL Ethernet または PS Ethernet に設定します。

FPGA ボードのユーザー データグラム プロトコル (UDP) ポート番号を 255 ~ 65,535 の整数として指定します。

依存関係

このパラメータを有効にするには、FPGA Data Capture Component Generator ツールで、FPGA vendor を Xilinx に、Connection type を PL Ethernet に設定します。

データ キャプチャ HDL IP コアのベース アドレスを数値として指定します。

依存関係

このパラメータを有効にするには、FPGA Data Capture Component Generator ツールで、FPGA vendor を Xilinx に、Connection type を PS Ethernet に設定します。

バージョン履歴

R2017a で導入

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)