このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGA Data Capture

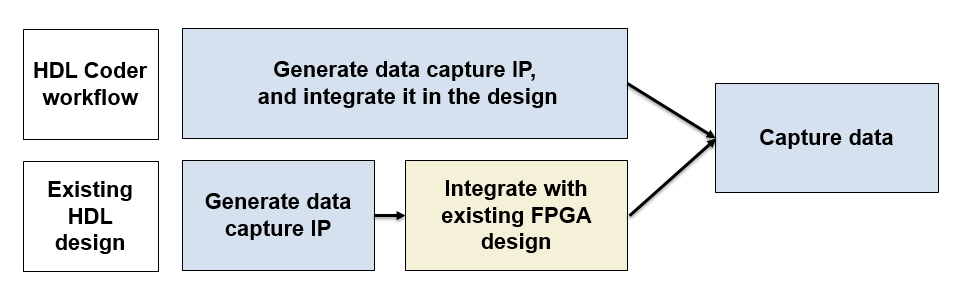

FPGA での設計の実行中に、FPGA データ取得を使って設計からの信号を観察します。この機能は、FPGA から信号データのウィンドウを取得し、データを MATLAB® または Simulink® に返します。信号をキャプチャするために、HDL Verifier™ は、HDL プロジェクトに統合し、デザインの残りの部分とともに FPGA に展開する必要がある IP コアを生成します。HDL Verifier は、FPGA と通信してデータを MATLAB または Simulink に返すツール、System object™、および Simulink モデルも生成します。

FPGA データを取得するには、次の手順に従います。

カスタマイズされたコンポーネントと IP コアを生成します。生成された IP のポート名とサイズを指定します。これらのポートは、キャプチャする信号と、キャプチャの発生を制御するトリガーとして使用する信号に接続します。

生成された IP を FPGA デザインに統合し、デザインを FPGA ボードに展開します。

生成されたツール、System object、または Simulink モデルを使用して、分析、検証、または表示用のデータをキャプチャします。キャプチャがいつ発生するかを制御するトリガー条件と、キャプチャするデータを制御するキャプチャ条件を構成できます。

データキャプチャワークフローを参照してください。

ツール

| FPGA Data Capture Component Generator | FPGAデータキャプチャコンポーネントの構成と生成 |

| FPGA Data Capture | ライブ FPGA からデータを MATLAB ワークスペースにインタラクティブにキャプチャします |

関数

hdlverifier.FPGADataReader | ライブ FPGA から MATLAB ワークスペースにデータをキャプチャする |

generateFPGADataCaptureIP | オープンFPGAデータキャプチャコンポーネントジェネレータ |

ブロック

| FPGA Data Reader | ライブFPGAからSimulinkモデルにデータをキャプチャする |

トピック

- データキャプチャワークフロー

FPGA 上で実行されている設計から信号データをキャプチャするための高レベルの手順。

- トリガー

トリガー条件を使用して、FPGA 上の特定のイベントに関するデータをキャプチャします。

- 捕獲条件

キャプチャ条件を使用して、FPGA からキャプチャするデータを制御します。

- データキャプチャの設計上の考慮事項

FPGA データ キャプチャの信号、タイミング、およびインターフェイスの制限。