このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

複数の FPGA データ キャプチャ IP を使用して FPGA から非同期データをキャプチャする

この例では、既存の HDL 設計で複数の FPGA データ キャプチャ IP を使用して、JTAG 接続を介して非同期 FPGA 内部信号をキャプチャする方法を示します。

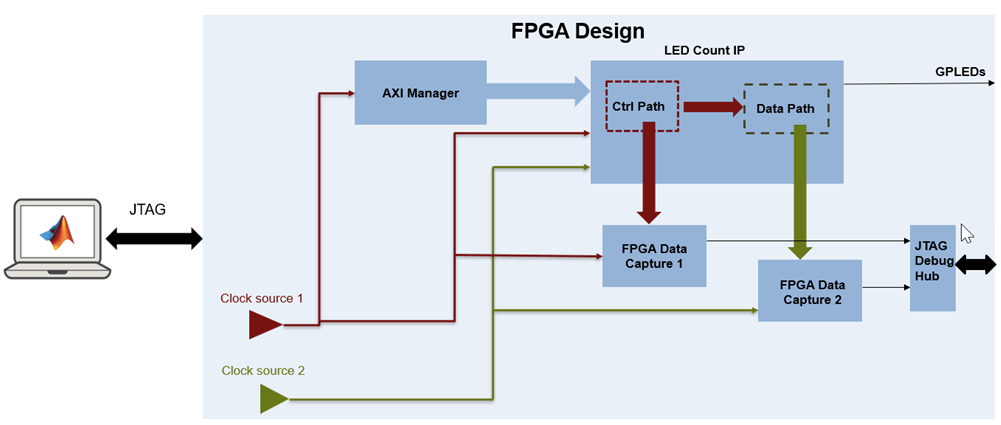

この例では、FPGA ボード上の LED を点滅させる LED カウント IP コアを含む既存の HDL デザインを使用します。AXI Manager IP は、点滅の頻度と方向を変更するために LED カウント IP コアを構成します。HDL 設計では、1 つのクロック ソースが AXI_Lite クロックを駆動し、別のクロックが IP コア クロックを駆動します。この例では、1 つのデータ キャプチャ IP を使用して AXI_Lite 信号をキャプチャし、もう 1 つのデータ キャプチャ IP を使用して LED カウント IP コアの内部信号をキャプチャします。JTAG デバッグ ハブ IP は、データ キャプチャ IP をホストに接続します。

この例は ZedBoard™ 上で実行されます。デザインを任意の Xilinx® Zynq® ボードにエクスポートできます。

要件と前提条件

Xilinx Vivado® Design Suite(サポートされているバージョンはに記載されています)

ZedBoard

JTAGケーブル。

サンプルリソースを準備する

Xilinx Vivado ツール パスを設定します。この例では、Xilinx Vivado 実行可能ファイルが C:\Xilinx\Vivado\2020.2\bin\vivado.bat ファイルにあることを前提としています。Xilinx Vivado 実行可能ファイルのパスを使用するようにこのコマンドを変更します。

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath', ... 'C:\Xilinx\Vivado\2020.2\bin\vivado.bat');

FPGA開発ボードのセットアップ

1. 電源スイッチがオフになっていることを確認してください。

2. AC 電源コードを電源プラグに接続し、電源アダプタ ケーブルを FPGA 開発ボードに差し込みます。

3. JTAG ダウンロード ケーブルを使用して、FPGA 開発ボードをホスト コンピューターに接続します。

4. FPGAボードの電源スイッチをオンにします。

FPGAデータキャプチャコンポーネントを生成する

この例では、led_count_ip IP の制御パスとデータ パスからの信号を監視します。各パスは 2 つの異なるクロック ソースによって駆動されます。制御パスは 50 MHz クロックで駆動され、データ パスは 200 MHz クロックで駆動されます。

制御パスでは、IP コアの構成を監視するには、AXI4_Lite_AWADDR、AXI4_Lite_AWValid、AXI4_WData、および AXI4_Lite_WValid の内部信号を観察する必要があります。これを容易にするために、例では、32 ビットの tp_AXI4_Lite_AWADDR 信号を AXI4_Lite_AWADDR に、1 ビットの tp_AXI4_Lite_AWValid 信号を AXI4_Lite_AWValid に、32 ビットの tp_AXI4_WData 信号を AXI4_Lite_WData に、1 ビットの tp_AXI4_Lite_WValid 信号を AXI4_Lite_WValid に出力ポートとしてタップします。

データ パスでは、IP コアの動作を監視するには、GPLEDs、Blink_direction、および Blink_freq の信号を観察する必要があります。これを容易にするために、例では、8 ビットの tp_GPLEDs 信号を GPLEDs に、1 ビットの tp_Blink_direction 信号を Blink_direction に、4 ビットの tp_Blink_freq 信号を Blink_freq に出力ポートにタップします。8 ビットの tp_GPLEDs 信号は IP コアの出力を示し、1 ビットの tp_Blink_direction 信号は LED の点滅方向を示し、4 ビットの tp_Blink_freq 信号は LED の点滅周波数を示します。

JTAG 接続を介してこれらの信号を操作するには、次の手順に従ってデータ キャプチャ コンポーネントを構成します。

1. MATLAB® でこのコマンドを実行して、FPGA Data Capture Component Generator ツールを起動します。

generateFPGADataCaptureIP

2. FPGA ベンダー を Xilinx に設定します。

3. 生成された IP 言語 を Verilog に設定します。

4. 接続タイプをJTAGに設定します。

5. データ キャプチャ IP の数 を 2 に設定します。データ キャプチャ IP を構成するための 2 つのタブが作成されます。

6. 最初のデータ キャプチャ IP の名前を ctrl_path_dc に変更し、2 番目のデータ キャプチャ IP の名前を data_path_dc に変更します。

7. データ キャプチャ 1 タブで、追加 ボタンをクリックして、ポート テーブルに 4 つの行を追加します。

8.信号の名前を tp_AXI4_Lite_AWADDR、tp_AXI4_Lite_AWValid、tp_AXI4_WData、tp_AXI4_Lite_WValid に変更します。ビット幅をそれぞれ 32、1、32、1 に変更します。

9. サンプル深度を128に設定します。

10. データ キャプチャ 2 タブで、追加 ボタンをクリックして、ポート テーブルに 3 つの行を追加します。

11. 信号の名前を LED_Out、Blink_direction、Blink_freq に変更します。ビット幅をそれぞれ 8、1、4 に変更します。

12.サンプル深度を8192に設定します。

13.FPGA データ キャプチャ コンポーネントを生成するには、生成 をクリックします。生成の結果はレポートに表示されます。

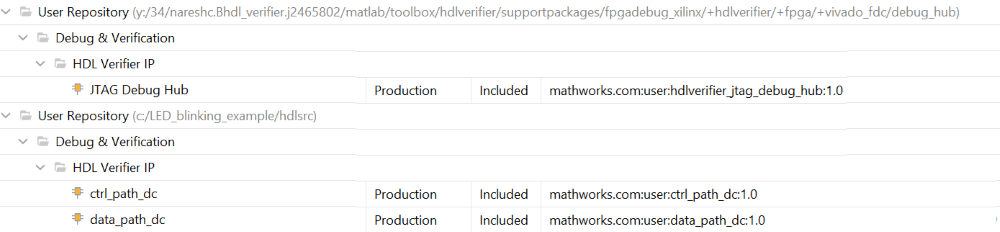

ツールは、データ キャプチャ IP ごとに hdlsrc フォルダーの下に 2 つのサブフォルダーを生成します。各サブフォルダーには、パッケージ化された IP コアとそれに対応する System object が含まれています。

FPGAデータキャプチャHDL IPの統合

1. MATLAB でこのコマンドを実行して IP コアを解凍します。

unzip('led_count_ip_v1_0.zip');

2. MATLAB でこのコマンドを実行して、この例の Vivado プロジェクトを作成します。

system('vivado -mode batch -source leadCreateProject.tcl &')

3. MATLAB でこのコマンドを実行して、Vivado プロジェクトのユーザー リポジトリに JTAG AXI Manager IP を追加します。

setupAXIManagerForVivado('project_1.xpr');

4. MATLAB でこのコマンドを実行して、データ キャプチャ IP と JTAG デバッグ ハブ IP を Vivado プロジェクトのユーザー リポジトリに追加します。

addFPGADataCaptureToVivado('project_1.xpr','DatacaptureIPFolder','hdlsrc');

5. Vivado プロジェクトを開き、AXI Manager、ctrl_path_dc、data_path_dc、および JTAG デバッグ ハブ IP をブロック デザインに追加し、以下に示すように接続します。

led_count_ip_0 のアドレスを 0x4A0D0000 に設定します。

あるいは、Vivado でこの Tcl コマンドを実行して手順 5 を完了することもできます。

source ./ModifyLedCountPrj.tcl

6. 各 IP の datacaptureID が一意であり、対応する System object DataCaptureID と一致していることを確認してください。

たとえば、ctrl_path_dc IP の場合、System object は hdlsrc/ctrl_path_dc/ctrl_path_dc.m にあり、DataCaptureID は 1 です。

デザインをコンパイルし、ビットストリームを生成します。

次のステップに進む前に、Vivado がビットストリームを正常に生成するまで待機します。このプロセスには約 5 ~ 10 分かかります。

データのキャプチャ

データをキャプチャするには、次の手順に従ってください。

1. MATLAB でこのコマンドを実行して、ビットストリームを対象のハードウェアにロードします。

filProgramFPGA('XilinxVivado','hdl_prj\vivado_ip_prj\vivado_prj.runs\impl_1\system_top_wrapper.bit',2)

2. MATLAB に AXI マネージャー オブジェクトを作成し、led_count_ip IP コアを構成します。

obj = aximanager('Xilinx');

3. 点滅の頻度を 0 から 15 に変更します。たとえば、MATLAB でこのコマンドを実行して、点滅周波数を High に設定します。

obj.writememory('0x400D0100',15);

4. MATLAB で FPGA データ キャプチャ コンポーネントが生成されるディレクトリに移動します。

cd hdlsrc

FPGA Data Capture ツールを起動します。このツールは、データ キャプチャ信号に合わせてカスタマイズされています。

launchMultipleDataCaptureApp;

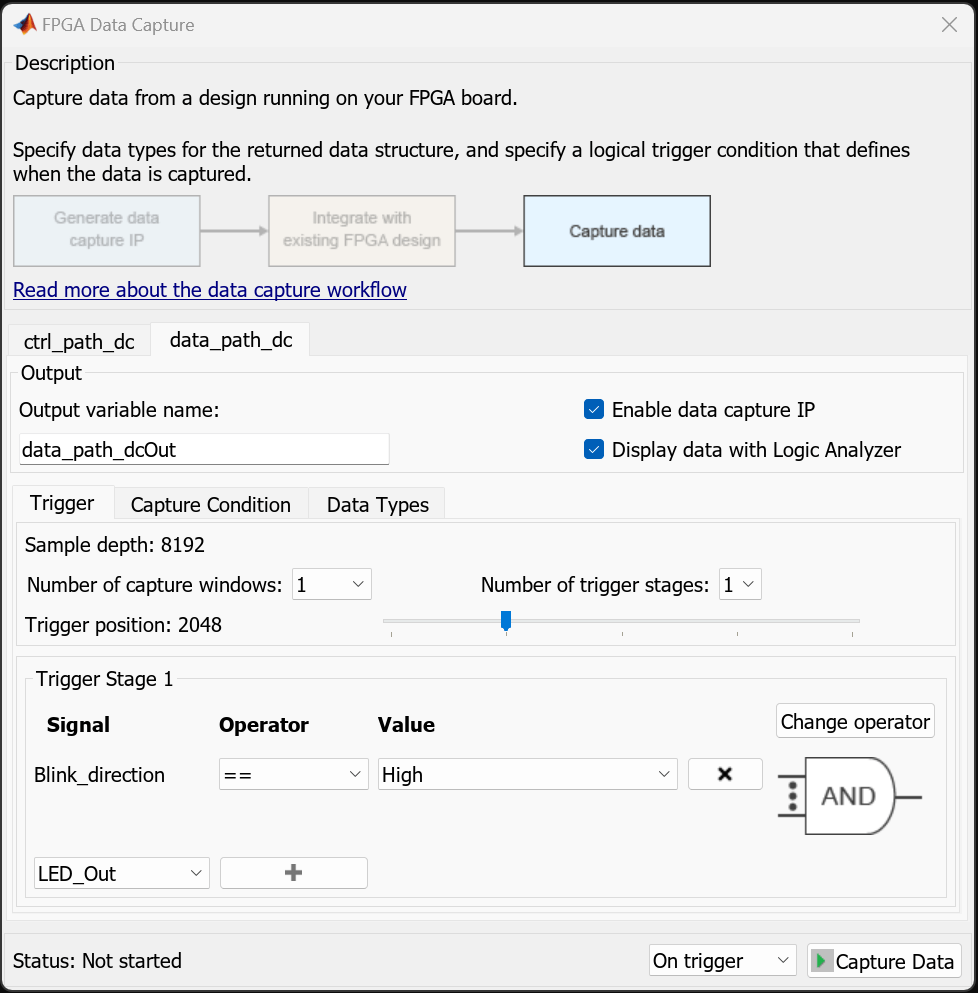

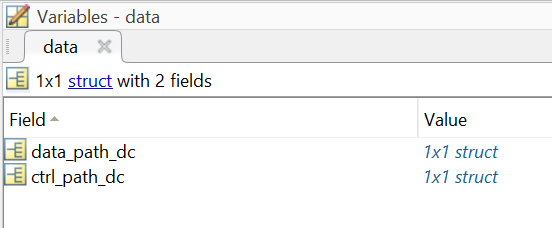

上記のコマンドは、MATLAB ワークスペース fpgadchub_obj にデータ キャプチャ ハブ オブジェクトを作成し、2 つのタブ ctrl_path_dc と data_path_dc を持つ FPGA データ キャプチャ ツールを起動して、各データ キャプチャ IP のトリガー設定を構成します。

5. MATLAB でこのコマンドを実行して、データ キャプチャ IP を非ブロッキング モードで実行します。

fpgadchub_obj.CaptureMode = 'nonblocking';

ノンブロッキング キャプチャ モードでは、FPGA データ キャプチャと AXI マネージャーを同時に使用できます。

6. データ キャプチャが不要な場合は、データ キャプチャ IP の各タブで、データ キャプチャ IP を有効にする のチェックを外します。

7. ctrl_path_dc タブのトリガー設定を以下のように構成します。

8.data_path_dc タブのトリガー設定を以下のように構成します。

9. Capture Data ボタンをクリックして、データ キャプチャ IP を開始します。IP は、指定されたトリガー条件が満たされるまで待機して、データ キャプチャ プロセスを開始します。

10. MATLAB でこのコマンドを実行して点滅方向を変更します。

obj.writememory('0x400D0104',1);

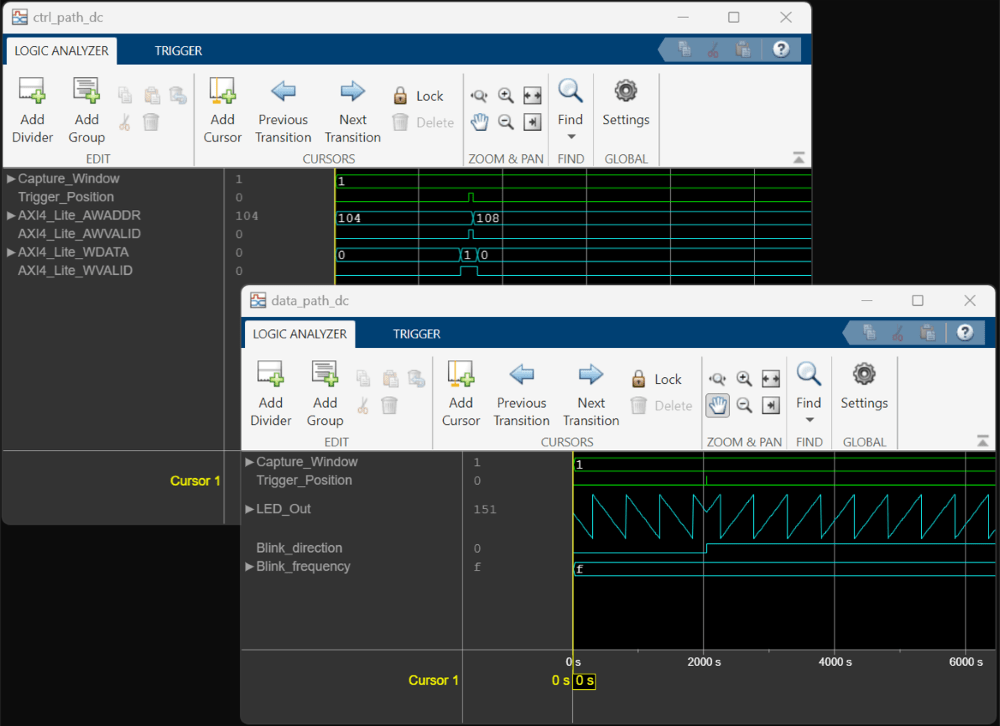

これで、データ キャプチャ IP はトリガー条件を検出し、ctrl_path_dcOut および data_path_dcOut 構造としてデータを MATLAB ワークスペースにキャプチャします。

キャプチャされたデータは、指定されたトリガー条件が検出されると、2 つの ロジック アナライザー ウィンドウに信号波形として表示されます。

コマンドライン インターフェイスを使用してデータをキャプチャするには、MATLAB の capture_ledblinking.m スクリプトを実行します。

まとめ

この例では、複数のデータ キャプチャ IP コアを生成し、それらを FPGA デザインに統合して、LED カウンター IP から MATLAB への非同期信号データをキャプチャします。この例は、HDL Verifier の FPGA データ キャプチャ機能を利用して FPGA 設計から非同期データをキャプチャするためのリファレンスとして使用できます。

参考

FPGA Data Capture | dataCaptureHub | addFPGADataCaptureToVivado