HDL Coder 入門

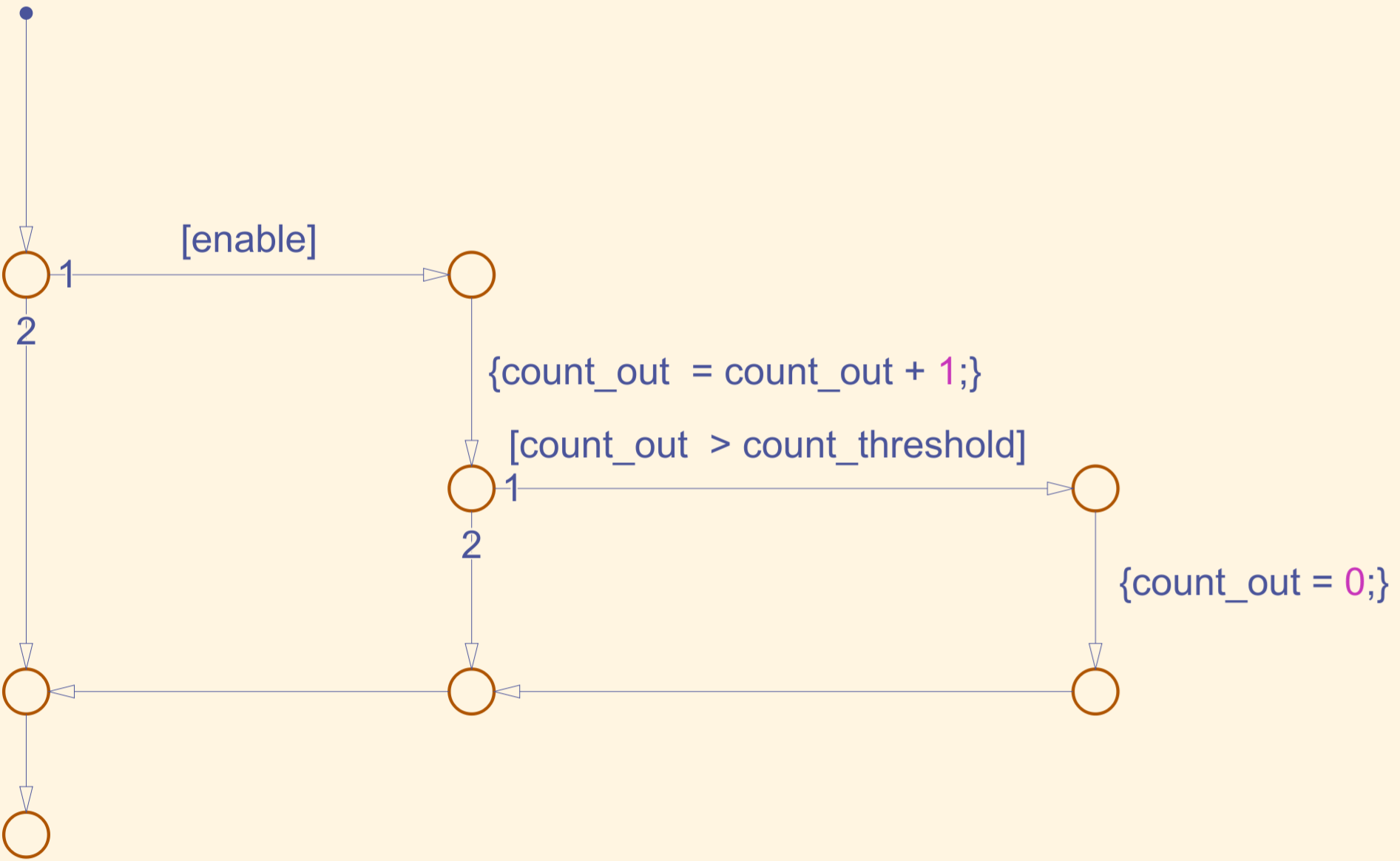

HDL Coder™ は MATLAB® 関数、Simulink® モデルおよび Stateflow® チャートから移植と合成が可能な Verilog® コード、SystemVerilog コード、および VHDL® コードを生成することで、FPGA、SoC、および ASIC 用の高位設計を可能にします。生成された HDL コードは FPGA プログラミング、ASIC のプロトタイピング、および量産設計で使用できます。

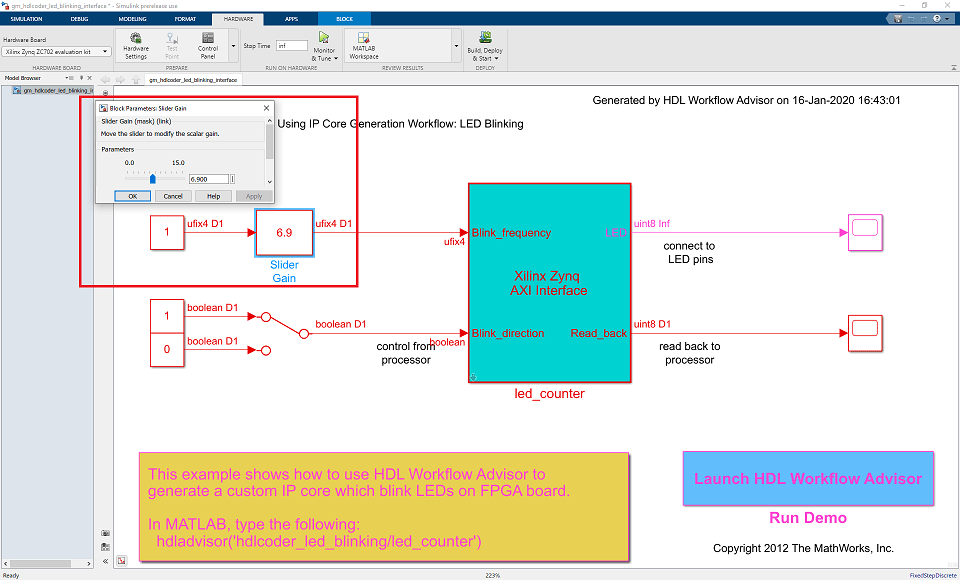

HDL Coder には、生成されたコードの Xilinx® ボード、Intel® ボード、および Microchip ボードでのプロトタイピングを自動化し、ASIC ワークフローおよび FPGA ワークフローの IP コアを生成するワークフロー アドバイザーが含まれています。合成前に、速度と面積の最適化を行い、クリティカル パスを強調表示し、リソースの使用率の推定を生成できます。HDL Coder では Simulink モデルと生成された Verilog コード、SystemVerilog コード、および VHDL コード間のトレーサビリティが提供されており、DO-254 やその他の標準に沿った整合性の高いアプリケーションのためのコード検証が可能です。

チュートリアル

- HDL 互換 Simulink モデルの作成

モデルの作成、および HDL コード生成の互換性のチェック。 - Simulink モデルからの HDL コードの生成

Simulink モデルから VHDL コード、Verilog コード、および SystemVerilog コードを生成する。 - Simulink モデルから生成された HDL コードの検証

HDL テスト ベンチを生成し、VHDL または Verilog コードを検証する。 - Simulink モデルからの HDL コード生成と FPGA 合成

コードを生成し、ターゲット FPGA でハードウェアで Simulink 設計を合成します。 - Create HDL- or HLS-Compatible MATLAB Algorithms

Create an HDL- or HLS-compatible MATLAB algorithm and MATLAB test bench and verify algorithm functionality. - Generate HDL Code from MATLAB Algorithms

Use the HDL Workflow Advisor to generate HDL code from MATLAB algorithms. - Synthesize Generated HDL Code from MATLAB Algorithms

Use a third-party synthesis tool to synthesize generated HDL code for target hardware.

Simulink から HDL

MATLAB から HDL

HDL コード生成について

- Choose to Generate HDL Code in Simulink or MATLAB

Choose between a Simulink or MATLAB design environment for your HDL Coder project.

- HDL コード生成のワークフローの基礎

MATLAB および Simulink アルゴリズムからの HDL コード生成と FPGA 合成のワークフローに従います。

- Create Designs Under Test and Test Benches in Simulink and MATLAB

Partition your design into a design under test and test bench in Simulink or MATLAB.

- Choose Fixed- or Floating-Point Data Types When Generating HDL Code

To balance precision and hardware resources, choose to use fixed-point, floating-point, or a mixed use of both data types in your design.

- HDL ワークフロー アドバイザーのワークフロー

HDL ワークフロー アドバイザーと選択できるさまざまなワークフロー、ターゲットにするプラットフォームについて確認する。

- HDL Coder での速度および面積の最適化

さまざまな速度および面積の最適化と、設計の最適化方法を確認。

注目の例

ビデオ

HDL Coder の概要

HDL Coder を使用して FPGA および ASIC の設計用に VHDL コードと Verilog コードを生成

Simulink を使用して FPGA または ASIC に MATLAB アルゴリズムを展開

Simulink、Fixed-Point Designer™、および HDL Coder を通じて MATLAB DSP アルゴリズムを取得し、FPGA または ASIC をターゲットにする方法を学習します。