クロッキングとマルチレート設計

クロック生成、マルチレート モデルの HDL コード生成のガイドライン

単一または複数のクロックおよびクロック制御要素 (クロックのリセットやタイミング コントローラーなど) を使用してマルチレート モデル用の HDL コードを生成します。

トピック

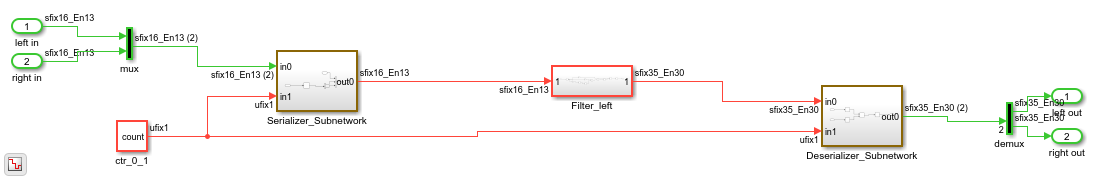

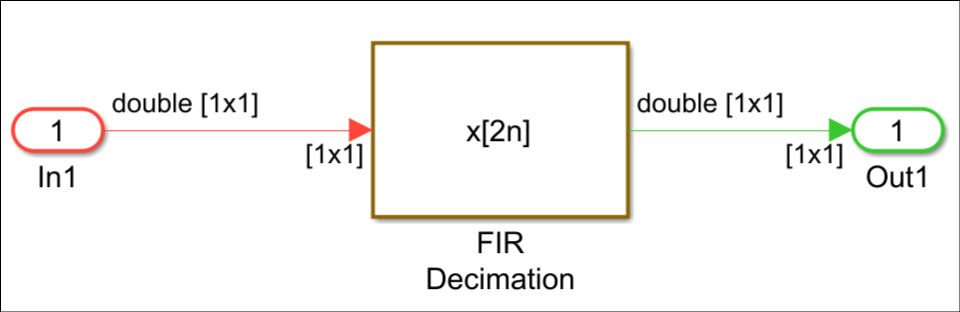

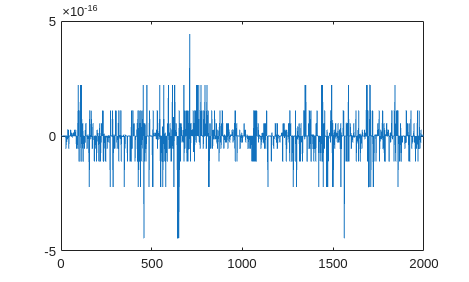

- マルチレート モデルからのコード生成

単一クロック、シングル タスク マルチレート モデルの HDL コード生成の概要。

- HDL Coder でのクロック バンドル信号の生成

HDL Coder™ が HDL コードでクロック信号、リセット信号、クロック イネーブル信号を生成する方法。

- グローバル オーバーサンプリング クロックの生成

グローバル オーバーサンプリング クロックを生成して DUT を大規模な設計に統合する。

- マルチレート モデルの HDL コード生成に関する要件

HDL コード生成のためのマルチレート モデルとブロックの設定に関するガイドライン

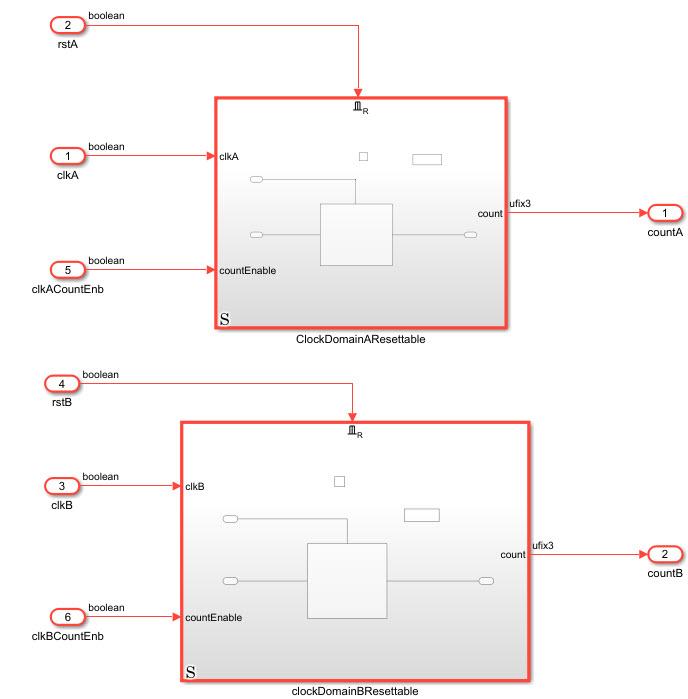

- マルチレート モデルのタイミング コントローラー

マルチレート モデルのタイミング コントローラーとクロック イネーブルについて学習する。

- タイミング コントローラーに対するリセットの生成

タイミング コントローラーのリセット生成方法。

- HDL コード生成のための Triggered Subsystem の使用

Triggered Subsystem と [Trigger As Clock] プロパティの使用方法、HDL コードの生成方法。

- Use Triggered Subsystem for Asynchronous Clock Domain

Design a model for an asynchronous clock domains using triggered subsystems.

- Generate Clock Enable Signals

Generation of clock enable signals in your DUT for single rate and multirate models.

- Customize Clock Bundle Names in Generated Code

Learn how to customize clock bundle names in the generated code.