Carrier Synchronizer

搬送波周波数オフセットの補正

ライブラリ:

Communications Toolbox /

Synchronization

説明

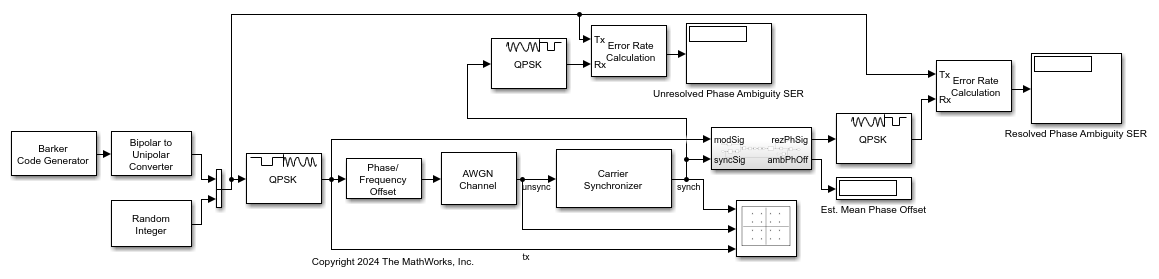

Carrier Synchronizer ブロックは、単一搬送波変調スキームを使用する信号の搬送波周波数と位相オフセットを補正します。キャリア同期装置のアルゴリズムは、BPSK、QPSK、OQPSK、8-PSK、PAM、および矩形 QAM 変調スキームと互換性があります。

メモ

同期アルゴリズムによって、変調タイプに依存する位相のあいまいさが生じる可能性があります。詳細については、潜在的な位相のあいまいさを参照してください。

次のアイコンはオプションの端子をもたないブロックを示します。![]()

例

端子

入力

出力

パラメーター

ブロックの特性

データ型 |

|

多次元信号 |

|

可変サイズの信号 |

|

詳細

アルゴリズム

このアルゴリズムは、[1] で説明されている PLL ベースのアルゴリズムを使用する閉ループ補償器を実装します。同期装置の出力 yn は、n 番目のサンプルの複素数入力信号 xn の周波数がシフトされたものです。同期装置の出力は となり、λn はダイレクト デジタル シンセサイザー (DDS) の出力です。DDS とは離散時間式の電圧制御発振器であり、離散時間位相同期回路における中核コンポーネントです。DDS は積分フィルターとして機能します。

周波数オフセットを補正するには、まずアルゴリズムが位相誤差 en を特定します。位相誤差の値は変調スキームによって異なります。

| 変調 | 位相誤差 |

|---|---|

| QAM または QPSK | この方程式の詳細については、[1] を参照してください。 |

| BPSK または PAM | この方程式の詳細については、[1] を参照してください。 |

| 8-PSK | この方程式の詳細については、[2] を参照してください。 |

| OQPSK | |

システムの安定性を確保するため、位相誤差は、以下で決定される双二次ループ フィルターを通過します。

ここで、ψn はサンプル n でのループ フィルターの出力で、gI は積分器のゲインです。積分器のゲインは次の方程式で決定されます。

ここで、

Bn は正規化されたループ帯域幅

ζ は減衰係数

K0 は位相回復ゲインであり、シンボルあたりのサンプル数に等しくなる。

Kp は位相誤差検出器ゲインであり、変調タイプによって決まる。

| 変調 | Kp |

|---|---|

| BPSK、PAM、QAM、QPSK、または OQPSK | 2 |

| 8-PSK | 1 |

ループ フィルターの出力はその後 DDS に渡されます。DDS は、前進オイラー法の積分規則に基づく式で表される、別の双二次ループ フィルターです。

ここで、gP は、次の式で表される比例ゲインです。

info オブジェクト関数は、正規化されたプルイン レンジ、最大周波数同期遅延および最大位相同期遅延の推定値を返します。正規化されたプルイン レンジ (Δf)pull-in はラジアン単位で表され、次のように推定されます。

(Δf )pull-in の式は、 が 1 に近づくにつれて精度が低下します。

最大周波数同期遅延 TFL と最大位相同期遅延 TPL はサンプル単位で表され、次のように推定されます。

参照

[1] Rice, Michael. Digital Communications: A Discrete-Time Approach. Upper Saddle River, NJ: Prentice Hall, 2008. pp. 359–393.

[2] Huang Zhijie, Yi Zhiqiang, Zhang Ming and Wang Kuang, "8PSK demodulation for new generation DVB-S2," 2004 International Conference on Communications, Circuits and Systems (IEEE Cat. No.04EX914), Chengdu, 2004, pp. 1447-1450 Vol.2, doi: 10.1109/ICCCAS.2004.1346447.

拡張機能

バージョン履歴

R2015a で導入