解析に関する問題の解決

制限事項に対処し、ベストプラクティスを使用して解析を改善する

Simulink® Design Verifier™ 解析結果は、特定の MATLAB Function ブロックや Stateflow® 機能など、Simulink ソフトウェアの機能をサポートしていないなどの問題で不完全になる場合があります。データ型を制限し、Simulink Design Verifier の技法を活用して、モデルの無関係の部分の特定、内部関係の発見、中間結果の再利用など複雑度を低減することで、このような問題を回避することができます。

モデルが大きく複雑なほど、モデルの解析に時間がかかったり、不完全になったりする可能性があります。大きいモデルや複雑なモデルに対する最善の結果を得るには、ボトムアップ アプローチを使用して、より小さなコンポーネントを先に解析します。これにより、反復が高速になり、解析時の到達不可能なコンポーネントなどの問題を切り離すことができます。モデルがタイマーやカウンターを使用する場合は、状態爆発や応答遅延などの問題が発生する可能性があるため、このような複雑さに対処するために回避策を使用します。解析をサポートしていないブロックを Simulink Design Verifier 関数に置き換え、必要に応じてテスト ベクトル生成をカスタマイズします。解析が特定のオブジェクティブに対して定まっていない場合は、トラブルシューティング技法を適用して、原因の特定と解決を行います。

関数

トピック

解析の制約

- 解析でサポートされていない Simulink ブロック

Simulink Design Verifier でサポートされる/されない Simulink ブロックを確認する。 - Simulink ソフトウェア機能に対する Simulink Design Verifier の制限事項

Simulink Design Verifier がサポートしない Simulink ソフトウェアの機能を確認する。 - Model ブロックに対する解析の制限事項と考慮事項

Model ブロックに対する Simulink Design Verifier の制限事項を確認する。 - Simulink Design Verifier の Stateflow 機能の制限事項

Simulink Design Verifier および Fixed-Point Designer™ ソフトウェアがサポートしない Stateflow ソフトウェアの機能をリストする。 - MATLAB のコード生成に対する Simulink Design Verifier の制限事項

MATLAB® のコード生成に対する Simulink Design Verifier ソフトウェアのサポートに関する制限事項を確認する。 - S-Function と C/C++ コードに対する Simulink Design Verifier の制限事項と考慮事項

Simulink Design Verifier での S-Function と生成コードの制限事項と考慮事項をリストする。

不完全な結果の解決

- モデル データ管理による解析の単純化

モデルを簡略化して Simulink Design Verifier の解析を簡略化する。 - 大規模モデルの解析の実行

大規模モデルを解析するための手法を説明します。

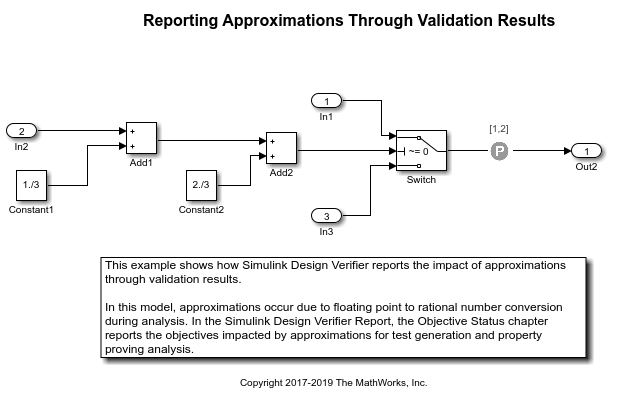

- 結果の近似について

Simulink Design Verifier による解析時の近似の特定および報告。 - ブロック置換を使用した解析の実行

ブロック置換を使用すると、代替ブロックの独自のライブラリとカスタムのブロック置換ルールを定義できる。 - Analyze and Resolve Undecided Objective Statuses

Address undecided objectives obtained after Simulink Design Verifier analysis.

- Address Undecided due to Runtime Error in Simulink Design Verifier Analysis

Resolve run-time errors in a model. - Review and Address Long Counterexample Objective Status

Review long counterexample objective status due to integer overflow error.