このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

解析用サブシステムの抽出

サブシステム抽出の概要

解析の速度低下を招く、または到達不可能なオブジェクティブをもつ大規模モデルがある場合、Simulink® Design Verifier™ を使用して、Atomic サブシステムまたは Stateflow® Atomic サブチャートを解析することができます。モデル解析のボトムアップ アプローチで説明されているように、この手法を使用して、大規模モデルを解析するボトムアップ アプローチを実装できます。

サブシステムまたは Atomic サブチャートを解析する場合、このソフトウェアは

サブシステムまたはサブチャートを新しいモデルに抽出します。

必要に応じて、新しく作成したモデルにブロックを追加し、その親モデルのサブシステムまたはサブチャートの実行コンテキストを複製します。

抽出されたモデルを解析し、結果を生成します。

メモ

Simulink Design Verifier ソフトウェアは、Atomic サブシステムおよび Atomic サブチャートのみを解析できます。

サブシステムの解析の詳細は、サブシステムのテスト ケースの生成を参照してください。

Atomic サブチャートの解析の詳細は、Stateflow Atomic サブチャートの解析を参照してください。

関数 sldvextract

関数 sldvextract を使用して、コンポーネント検証用にサブシステムおよび Atomic サブチャートを抽出することができます。サブシステムまたは Atomic サブチャートを抽出することで、コンポーネントを残りのシステムから分離し、そのコンポーネントのアルゴリズムをテスト、検証することができます。詳細については、コンポーネント検証とはおよびFunctions for Component Verificationを参照してください。

抽出されたモデルの構造

サブシステムまたは Atomic サブチャートを解析すると、Simulink Design Verifier はサブシステムまたは Atomic サブチャート、および元のそのサブシステムに接続されていた端子に対応するすべての入力端子および出力端子を含む新しいモデルを作成します。

新しいモデルの端子に対して、元のモデルをコンパイルすることによって特定できる次のプロパティが割り当てられます。

データ型

サンプルレート

信号の次元

信号の範囲の最小値と最大値

新しいモデルには subsystem_name という名前が付けられます。ここで、subsystem_name はサブシステムの名前です。

次の節では、Simulink Design Verifier がサブシステムをどのように抽出および解析するかの例を示します。

グローバル データ ストレージから読み取られたサブシステムの解析

データ ストアは、入力または出力信号を直接データ ストアに接続することなしにデータの書き込みまたは読み取りができるリポジトリです。

データ ストアの作成には、Data Store MemoryブロックまたはSimulink.Signalオブジェクトを使用します。Data Store Memory ブロックまたは Simulink.Signal オブジェクトはデータ ストアを表し、そのプロパティを指定します。データ ストアの名前は、それぞれが一意でなければなりません。

サブシステムの外側でアクセスされるデータ ストアからデータを読み取るサブシステムを解析する場合、解析では

Data Store Memory ブロックを新しいモデルに追加します。

データ ストアに書き込む入力端子を追加します。入力はデータ ストアに書き込むため、Simulink Design Verifier の解析の目的でデータは (指定されたデータ型の範囲内で) 任意の値をとることができます。

データ ストアで最小値および最大値を指定する場合、それらの値は新しい入力端子に代入されます。

次の例では、モデル例 sl_subsys_fcncall8 のサブシステムを解析します。

1.モデル例 sl_subsys_fcncall8 を開きます。

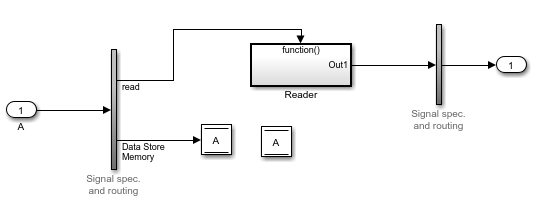

open_system('sl_subsys_fcncall8');このモデルでは、データ ストア A を定義します。Atomic サブシステム Reader は Data Store Read ブロックを使用してここからデータを読み取ります。

2.Reader サブシステムを右クリックして、[Design Verifier]、[サブシステムに対するテストを生成] を選択します。

Simulink Design Verifier のログ ウィンドウでは、サブシステムが Reader という名前の新しいモデルに抽出され、解析されたことが示され、生成する結果の選択肢が表示されます。

3.ソフトウェアで <current_folder>\sldv_output\Reader. に作成された新しい Reader モデルを開きます。

新しい Inport ブロック A はデータ ストアに書き込み、新しいモデルのサブシステム Reader でそれが使用されます。

Function-Call Subsystem の解析

Function-Call Subsystem は、その実行が信号値でなく C MEX S-Function の内部ロジックで決定される Triggered Subsystem です。Function-Call Subsystem は常にアトミックです。

メモ: 詳細については、Implement Function-Call Subsystems with S-Functionsを参照してください。

Function-Call Subsystem が含まれるモデルを解析する場合、Simulink Design Verifier は、トリガーを再現する Inport ブロックおよびサブシステムのコピーを含む新しいモデルを作成します。その上で新しいモデルが解析されます。

次の例では、sl_subsys_fcncall2 モデルの Function-Call Subsystem を解析します。

1.モデル例 sl_subsys_fcncall2 を開きます。

open_system('sl_subsys_fcncall2');2.このモデルには、Function-Call Subsystem f をトリガーする Chart という名前の Stateflow™ チャートが含まれます。

f サブシステムを右クリックして、[Design Verifier]、[サブシステムに対するテストを生成] を選択します。

サブシステムは f0 という名前の新しいモデルに抽出され、その抽出されたモデルが解析されて結果が生成されます。

3.ソフトウェアで <current_folder>\sldv_output\f0 に作成された f0 モデルを開きます。

Inport ブロックと新しいサブシステム ブロックは、新しい f0 モデルで Function-Call Subsystem f のトリガーを再現します。

グローバルな Simulink 関数の解析

Simulink® 関数は、一連の入力が指定されたときに一連の出力を計算する計算単位です。

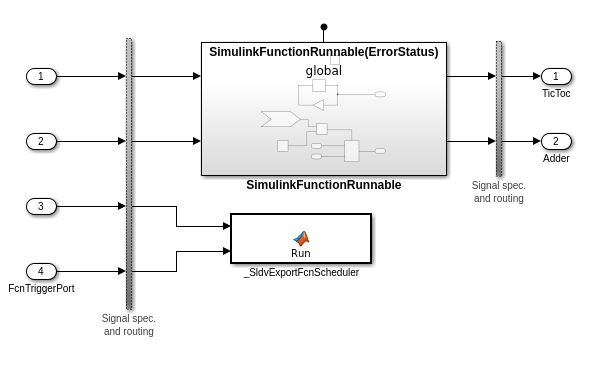

Simulink 関数サブシステムを解析すると、Simulink Design Verifier™ では、MATLAB Function ブロック _SldvExportFcnScheduler およびサブシステムのコピーを含む新しいモデルが作成されます。この MATLAB Function ブロックは、Simulink 関数を非周期的に呼び出し、Simulink 関数の入力引数を表す入力端子によって駆動されます。FcnTriggerPort と呼ばれる追加の Inport ブロックの値は、タイム ステップ内で特定の関数を呼び出すかどうかを示します。

次の例では、sldvexGlobalSimFcn モデルのグローバルな Simulink 関数を解析します。

1.sldvexGlobalSimFcn モデルを開きます。

open_system('sldvexGlobalSimFcn');2.サブシステムを右クリックして、[Design Verifier]、[サブシステムに対するテストを生成] を選択します。

サブシステムは新しいモデルに抽出され、その抽出されたモデルが解析されて結果が生成されます。

3.<current_folder>\sldv_output\ に作成された新しい SimulinkFunctionRunnable0 モデルを開きます。

Inport ブロック FcnTriggerPort は、新しい SimulinkFunctionRunnable0 モデルで Simulink 関数 SimulinkFunctionRunnable を呼び出します。