sldvextract

サブシステムまたはサブチャートの内容を解析用の新しいモデルに抽出する

構文

説明

newModel = sldvextract(subchart)subchart の内容を抽出し、Simulink Design Verifier ソフトウェア向けの解析用モデルを作成します。subchart には Atomic サブチャートの絶対パスを指定します。そのモデル名が存在する場合、sldvextract はサブチャート名をモデル名に使用し、モデル名に数字を追加します。

メモ

エクスポートされたグラフィカル関数がサブチャートの外部にあり、Atomic サブチャートがこの関数を呼び出す場合、sldvextract はモデルを作成しますが、新しいモデルはコンパイルされません。

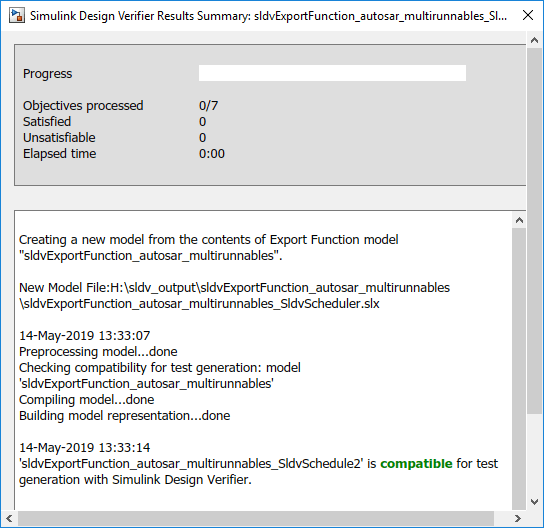

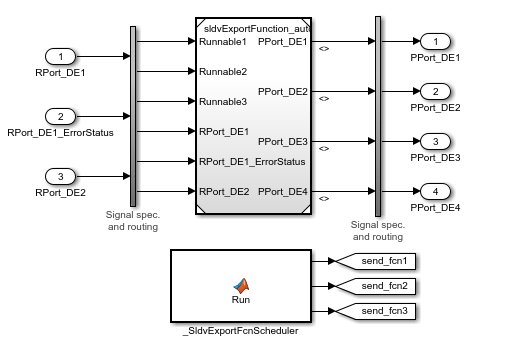

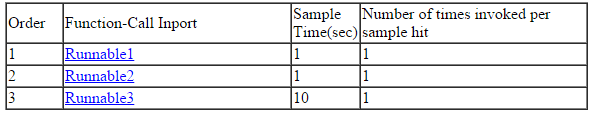

newModel = sldvextract(exportfcnmodel)exportfcnmodel を呼び出すスケジューラ モデルを作成します。sldvextract は newModel を使用して新しいモデルの名前を返します。newModel は、exportfcnmodel のモデル名と接尾辞 SldvScheduler で構成されます。そのモデル名が既に存在する場合、sldvextract は exportfcnmodel の名前をモデル名に使用し、モデル名に数字を追加します。

newModel = sldvextract(modelmissingslfunctiondef)modelmissingslfunctiondef のスタブ モデルを抽出します。newModel を使用して新しいモデルの名前を返します。そのモデル名が既に存在する場合、sldvextract は接尾辞 SldvStub が付いた入力モデル名を抽出されたモデルの名前に使用し、モデル名に数字を追加します。

newModel = sldvextract(modelmissingslfunctiondef, showModel)showModel を true に設定した場合に、抽出されたモデルを開きます。showModel が false に設定された場合、抽出されたモデルは読み込まれるだけです。

例

入力引数

出力引数

制限

Simulink Design Verifier では、次の場合は抽出がサポートされません。

サブシステムに再初期化端子がある。詳細については、Reinitialize States of Blocks in Subsystemを参照してください。

モデル ブロックに Initialize、Reset、Reinitialize、または Terminate のイベント端子がある。詳細については、Model ブロックのモデル イベントのシミュレーションを参照してください。

バージョン履歴

R2007a で導入