速度と面積の最適化

リソースの共有、ストリーミング、パイプライン、RAM マッピングによる改善

ターゲット ハードウェアに対し、速度と面積の最適化を使用して、タイミングおよび面積の要件を満たす HDL コードを MATLAB® 関数から生成します。面積の最適化は、設計のリソース使用率を削減します。速度の最適化は、クリティカル パスを最適化することで設計がより高い周波数で実行されるように、ターゲット FPGA での設計のタイミングを改善します。HDL Coder™ に関する最適化の各タイプの詳細については、HDL Coder での速度および面積の最適化を参照してください。

関数

coder.hdl.loopspec | Unroll or stream loops in generated HDL and High-Level Synthesis (HLS) code |

coder.hdl.pipeline | MATLAB 式の出力にパイプライン レジスタを挿入 |

coder.hdl.ramconfig | Specify RAM mapping configuration for persistent array variables (R2023b 以降) |

hdl.npufun | Apply neighborhood processing and element-wise operations to incoming image or matrix for frame-to-sample conversion (R2022b 以降) |

hdl.iteratorfun | Apply iterative operation to an incoming image or matrix for frame-to-sample conversion (R2022b 以降) |

トピック

最適化の基礎

- HDL Coder での速度および面積の最適化

さまざまな速度および面積の最適化と、設計の最適化方法を確認。 - クロック イネーブルの速度の指定

クロック イネーブルを設計のベース速度または入力データ速度で実行するように設定します。 - クロック イネーブルの最小化

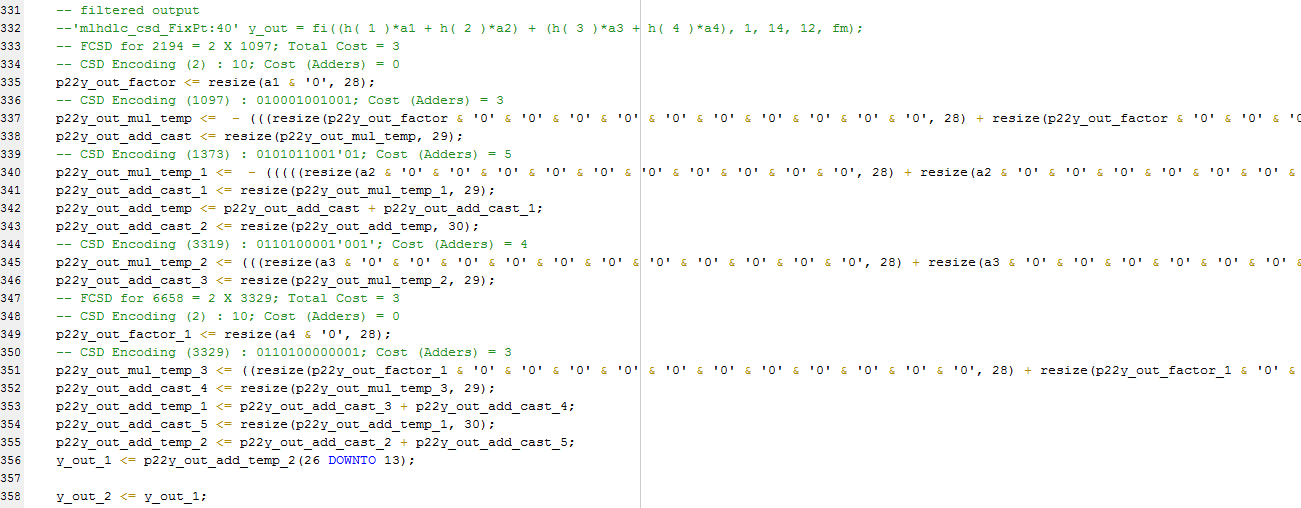

クロック イネーブルのないレジスタのコードを生成。 - 定数乗算器の最適化

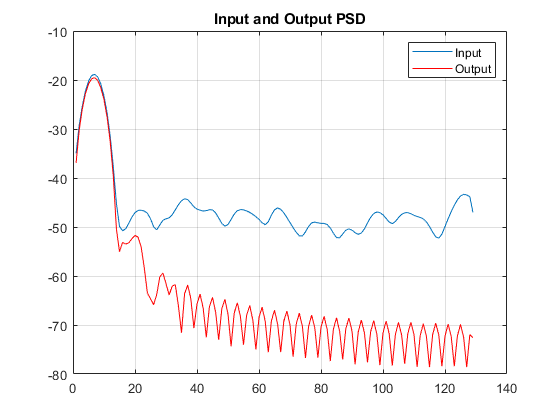

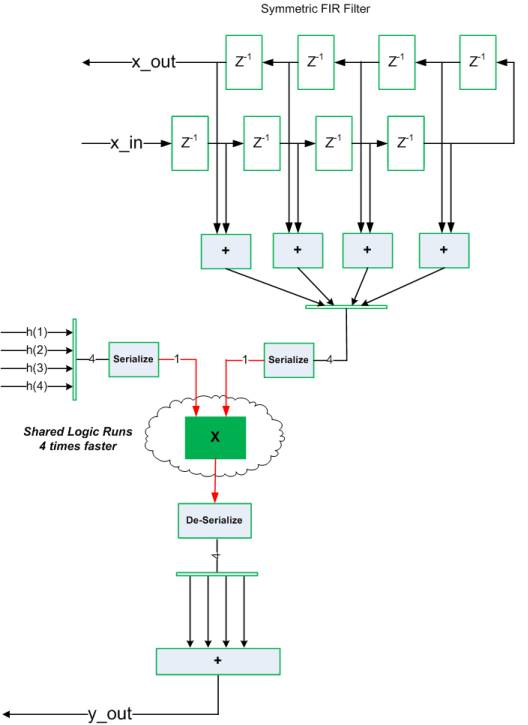

定数乗算器の最適化とは何か、およびこの最適化を指定する方法。

面積の最適化

- Apply RAM Mapping to Optimize Area

Map elements to RAM to optimize area on your target hardware. - Manage How HDL Coder Maps RAM

Learn how HDL Coder settings affect RAM mapping. - 永続配列と dsp.Delay オブジェクトの RAM へのマッピング

永続配列とdsp.Delayオブジェクトをハードウェアの RAM にマッピングして、ターゲット デバイス上の使用面積を削減します。 - ROM への行列のマッピング

行列定数を ROM にマッピングするには、次の条件があります。 - Map Matrices to Block RAMs to Reduce Area

This example shows how to use the RAM mapping optimization in HDL Coder™ to map persistent matrix variables to block RAMs in hardware. - Loop Streaming to Reduce Area

This example shows how to use the design-level loop streaming optimization in HDL Coder™ to optimize area.

速度の最適化

- MATLAB コードのパイプライン化

パイプラインは、レジスタをハードウェアの戦略的な場所に挿入してクリティカル パスを分割することで、最大クロック速度の向上に役立ちます。 - MATLAB 式のパイプライン

MATLAB 式の出力へのレジスタの挿入 - MATLAB ループの最適化

面積または速度のためのループの最適化 - 分散型パイプライン方式

分散型パイプライン方式の定義、利点およびコスト - クロックレート パイプライン

パイプライン レジスタを低速のデータ レートではなく、高速のクロック レートで挿入する

I/O の最適化

- Use Neighborhood, Reduction, and Iterator Patterns with a Frame-Based Model or Function for HDL Code Generation

Generate HDL code from a frame-based design that models neighborhood, reduction, and iterator patterns.