このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

dsp.DCBlocker

入力信号の DC 成分 (オフセット) のブロック

説明

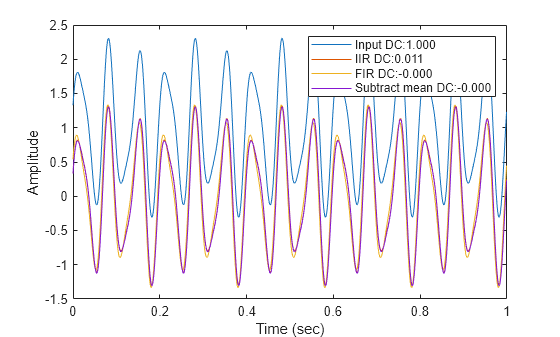

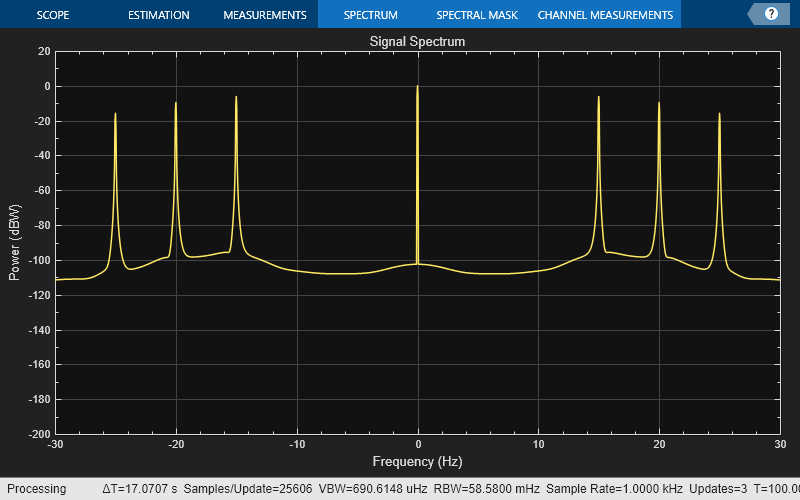

dsp.DCBlocker System object™ は、入力信号の各チャネル (列) から DC オフセットを削除します。時間の経過に沿って操作が実行され、DC オフセットが継続的に推定および削除されます。

入力信号の DC 成分をブロックするには、次の手順に従います。

dsp.DCBlockerオブジェクトを作成し、そのプロパティを設定します。関数と同様に、引数を指定してオブジェクトを呼び出します。

System object の機能の詳細については、System object とはを参照してください。

オブジェクトは、特定の条件下で C/C++ コード生成と SIMD コード生成をサポートします。詳細については、コード生成を参照してください。

作成

プロパティ

オブジェクト関数

オブジェクト関数を使用するには、System object を最初の入力引数として指定します。たとえば、obj という名前の System object のシステム リソースを解放するには、次の構文を使用します。

release(obj)

例

アルゴリズム

参照

[1] Nezami, M. “Performance Assessment of Baseband Algorithms for Direct Conversion Tactical Software Defined Receivers: I/Q Imbalance Correction, Image Rejection, DC Removal, and Channelization.” MILCOM, 2002.