モデル判定カバレッジのテスト ケースの生成

モデル例の作成

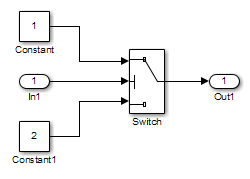

この例のモデルを作成します。

Simulink® モデルを作成します。

次のブロックを空のモデル ウィンドウにコピーします。

モデル内の Constant ブロックの 1 つをダブルクリックして、その [定数値] パラメーターを

2に指定します。モデルが次の図のようになるように、ブロックを接続します。

[アプリ] タブで、[アプリ] セクションの右側にある矢印をクリックします。

[モデルの検証、妥当性確認、テスト] で、[Design Verifier] をクリックします。

[Design Verifier] タブの [準備] セクションのモード設定のドロップダウン メニューから、[設定] をクリックします。

[コンフィギュレーション パラメーター] ダイアログ ボックスで、[ソルバー] ペインを選択します。[ソルバーの選択] で、次のようにします。

[タイプ] オプションを

[固定ステップ]に設定します。[ソルバー] オプションを

[離散 (連続状態なし)]に設定します。

Simulink Design Verifier は、固定ステップ ソルバーを使用するモデルのみを解析します。

[OK] をクリックして変更を保存し、[コンフィギュレーション パラメーター] ダイアログ ボックスを閉じます。

モデルを

ex_generate_test_cases_exampleという名前で保存します。

モデル例の互換性のチェック

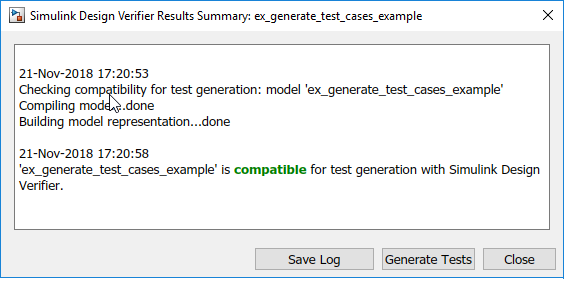

Simulink Design Verifier がモデルを解析する際、解析の開始前に必ず互換性チェックが実行されます。モデルに互換性がない場合、解析できません。

解析の開始前に、モデルが Simulink Design Verifier ソフトウェアと互換であることを確認することもできます。

ex_generate_test_cases_exampleモデルを開きます。[Design Verifier] タブで、[互換性チェック] をクリックします。

ソフトウェアはログ ウィンドウを表示し、モデルが解析において互換であるかどうかを示します。

ここで作成したモデルは互換性があります。

テスト生成オプションの構成

ex_generate_test_cases_example モデルの 100% の判定カバレッジを達成するテスト ケースを生成するように Simulink Design Verifier を構成します。

ex_generate_test_cases_exampleモデルを開きます。[Design Verifier] タブの [モード] セクションで、[テスト生成] を選択します。

[テスト生成の設定] をクリックします。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [テスト生成] ペインで [モデル カバレッジ オブジェクティブ] パラメーターを

[判定]に設定します。この例では、解析により判定カバレッジのみが記録されるテスト ケースが生成されます。

[テスト スイートの最適化] パラメーターは既定では

[自動]に設定されています。より少数で長いテスト ケースを生成する場合は、[テスト スイートの最適化] パラメーターで[LongTestcases]を選択します。[OK] をクリックして変更を保存し、[コンフィギュレーション パラメーター] ダイアログ ボックスを閉じます。

ex_generate_test_cases_exampleモデルを保存します。

モデル例の解析

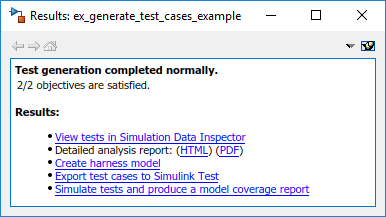

[Design Verifier] タブで、[テストの生成] をクリックします。Simulink Design Verifier がモデルを解析し、テスト ケースが生成されます。

解析中、[結果の概要] ウィンドウには解析の進行状況が表示されます。ここには、処理されたテスト オブジェクティブ数やどのオブジェクティブが達成されたかなどの情報が表示されます。

解析結果のレビュー

解析が完了すると、[結果の概要] ウィンドウには、結果を確認するためのこれらのオプションが表示されます。

以下の節では、解析結果をレビューする方法を説明します。

モデルの解析結果のレビュー

モデル例の解析結果を強調表示します。

ex_generate_test_cases_example解析の [結果の概要] ウィンドウで、[解析結果をモデル上で強調表示] をクリックします。

Switch ブロックは緑で強調表示されます。これは、Switch ブロックにそのテスト オブジェクティブを達成させるテスト ケースがあることを示します。

Simulink Design Verifier の [結果] ウィンドウが開きます。モデルのオブジェクトをクリックすると、ウィンドウが変化してそのオブジェクトの詳細な解析結果が表示されます。既定では、Simulink Design Verifier の [結果] ウィンドウは常に最前面に表示されます。ウィンドウが他のウィンドウの背面に移動できるようにするには、

をクリックして [常に手前に表示] をオフにします。

をクリックして [常に手前に表示] をオフにします。

強調表示された Switch ブロックをクリックします。

Simulink Design Verifier の [結果] ウィンドウには、両方のテスト オブジェクティブにテスト ケースが生成されたことが示されます。

trigger > thresholdtrigger < threshold

モデルの強調表示された解析結果の詳細は、モデルにおける結果の強調表示を参照してください。

詳細な解析レポートのレビュー

詳細な HTML 解析レポートを作成します。

Simulink Design Verifier の [結果の概要] ウィンドウの [詳細な解析レポート] で、[HTML] をクリックします。

HTML レポートがブラウザー ウィンドウで開きます。

レポートには次の目次が含まれます。ハイパーリンクをクリックしてレポートの節に移動します。

目次の

Summaryをクリックしてレポートの概要の章を表示します。概要の章には、モデルおよびオブジェクティブのステータス (達成されたかどうか) に関する情報がリストされています。

[目次] で

Analysis Informationをクリックして解析情報の章を表示します。解析情報の章には、次の情報があります。

解析したモデル。

解析に指定したオプション。

解析中に実行された近似。

[目次] で

Test Objectives Statusをクリックしてレポートのテスト オブジェクティブ ステータスの章を表示します。この表には、解析により

ex_generate_test_cases_exampleモデル内の Switch ブロックに関連付けられた両方のテスト オブジェクティブが達成されていることが示されます。これらに対して 2 つのテスト ケースが生成されています。表の [テスト ケース] 列の

2をクリックして Test Case 2 節を表示します。この節には、モデルのオブジェクティブを達成するため解析で生成されたテスト ケースの詳細があります。このテスト ケースは、Switch ブロックが 3 番目の入力を出力端子に渡すときにテスト オブジェクティブ 1 を達成します。具体的には、Switch ブロック制御信号の値 –1 により、ブロックが 3 番目の入力をブロック出力として渡すことが判定されます。

HTML レポートの詳細は、解析レポートの結果の確認を参照してください。

ハーネス モデルのレビュー

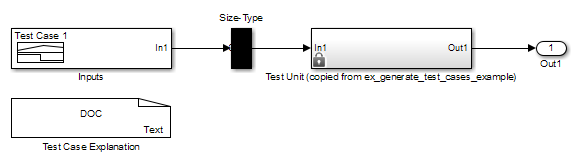

モデル内のテスト オブジェクティブを達成させるテスト ケースを含むハーネス モデルを作成するには、Simulink Design Verifier の [結果の概要] ウィンドウで [ハーネス モデルの作成] をクリックします。

ex_generate_test_cases_example_harness という名前のハーネス モデルが作成されます。

Inputs という名前の Signal Editor ブロックにはテスト ケースが含まれています。Inputs ブロックをダブルクリックしてテスト ケースを表示します。テストのシミュレーションおよびモデル カバレッジ レポートの生成で説明されているように、Signal Editor ブロックから、テスト ケースを使用してモデルのシミュレーションを行い、モデル カバレッジ レポートを生成できます。

ハーネス モデルの詳細については、テスト シミュレーションのためのハーネス モデルの使用を参照してください。

解析で多数のテスト ケースが生成される場合. 大規模モデルがある場合、解析で多数のテスト ケースを含むハーネス モデルが生成される場合があります。

より少数のテスト ケースを生成するには、次のようにします。

[テスト スイートの最適化] パラメーターを

[LongTestcases]に設定します。解析を再実行します。

[LongTestcases] 最適化により、解析ではより少数のテスト ケースが生成され、それぞれがより長く、複数のテスト オブジェクティブを達成するようになります。

テストのシミュレーションおよびモデル カバレッジ レポートの生成

ハーネス モデルで生成されたテスト ケースを使用し、ハーネス モデルのシミュレーションを実行するには、次を行います。

ハーネス モデルで

Inputsブロックをダブルクリックして [ブロック パラメーター] ダイアログ ボックスを開き、[信号エディターを開く] ボタンをクリックして [信号エディター] ダイアログ ボックスを開きます。

モデルのハーネスのウィンドウで [すべて実行] をクリックします。

両方のテスト ケースを使用してハーネス モデルのシミュレーションが実行され、モデル カバレッジ情報が収集されてカバレッジ レポートが表示されます。カバレッジ レポートには、テスト ケースが

ex_generate_test_cases_exampleモデルに対し 100% 判定カバレッジを記録していることを示します。

ハーネス モデルを作成せずにモデルのシミュレーションを実行することもできます。Simulink Design Verifier のログ ウィンドウで、[テストをシミュレートしてモデル カバレッジ レポートを生成] をクリックします。

モデル カバレッジの詳細については、最上位モデル カバレッジ レポート (Simulink Coverage)を参照してください。

sldvData ファイルの表示

Simulink Design Verifier データ ファイルは、sldvData という名前の構造体が含まれる MAT ファイルです。この構造体には、解析時に収集および生成されたすべてのデータが格納されます。このデータ ファイルを使用して、解析の実行やカスタム レポートの生成が行えます。

データ ファイルを表示するには、ログ ウィンドウのデータ ファイル名をクリックします。この例では、ex_generate_test_cases_example_sldvdata.mat です。データ ファイル名をクリックすると、sldvData オブジェクトのコピーが MATLAB® ワークスペースに作成され、そのデータのレビューや操作が可能になります。

Simulink Design Verifier データ ファイルの詳細については、データ ファイルの解析結果の表示と解釈を参照してください。

[結果の概要] ウィンドウでの解析結果のレビュー

モデルが開いたままであれば、[結果の概要] ウィンドウで最新の Simulink Design Verifier の解析結果を表示できます。

[Design Verifier] タブの [結果の確認] セクションで、[以前の結果の読み込み] または [結果の確認] をクリックして結果を表示します。

任意の Simulink Design Verifier 解析に対して、[結果の概要] ウィンドウから次のタスクを実行できます。

| タスク | 参照先 |

|---|---|

モデルにおける、解析結果の強調表示。 | モデルにおける結果の強調表示 |

詳細な解析レポートの生成。 | 解析レポートの結果の確認 |

ハーネス モデルの作成。または既に存在する場合はモデルの開始。 解析時にテスト ケースが生成されなかった場合、このオプションは使用できません。 | テスト シミュレーションのためのハーネス モデルの使用 |

データ ファイルの表示。 | データ ファイルの解析結果の表示と解釈 |

ログ ファイルの表示。 | モデルの解析と結果の解釈 |

モデルを閉じると、解析結果は表示できなくなります。

テスト生成のカスタマイズ

Test Condition ブロックを使用して、解析時にモデルの信号を特定の値に制約できます。

MATLAB のコマンド プロンプトで

sldvlibと入力し、Simulink Design Verifier ライブラリを表示します。Objectives and Constraints サブライブラリを開きます。

Simulink Design Verifier ライブラリからモデル ウィンドウに Test Condition ブロックをドラッグしてモデルにコピーします。

モデル ウィンドウで、Test Condition ブロックを Inport と Switch ブロックの間に挿入します。

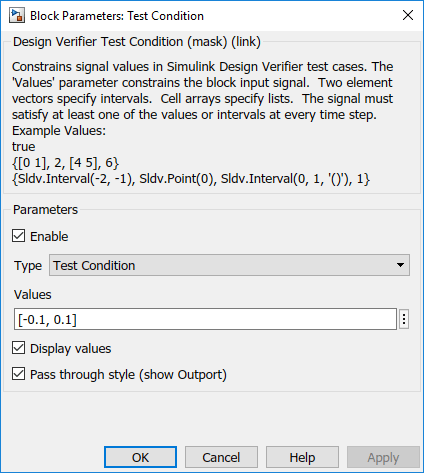

Test Condition ブロックをダブルクリックして、その属性にアクセスします。

[ブロック パラメーター] ダイアログ ボックスが開きます。

[値] ボックスに「

[-0.1, 0.1]」と入力します。このモデルのテスト ケースを生成する際に、解析により Switch ブロックの制御端子に入る信号値が、指定された範囲に制約されます。

[OK] をクリックして変更を保存し、[ブロック パラメーター] ダイアログ ボックスを閉じます。

ex_generate_test_cases_with_tc_blockとしてモデルを保存し、それを開いたままにします。

モデル例の再解析

Test Condition ブロックを含む ex_generate_test_cases_with_tc_block モデルを解析します。Test Condition ブロックがどのようにテスト生成に影響するかを確認するには、Analyze Example Modelで得られた結果とこの解析結果を比較します。

[Design Verifier] タブで、[テストの生成] をクリックします。

Simulink Design Verifier ソフトウェアがログ ウィンドウを表示し、モデルの解析を開始してテスト ケースを生成します。解析の完了後、[結果の概要] ウィンドウに結果をレビューするためのオプションが表示されます。

[結果の概要] ウィンドウで、[HTML レポート] をクリックします。

[目次] で [概要] をクリックしてレポートのレビューを開始します。

概要の章には、Simulink Design Verifier がモデル内で 2 つのテスト オブジェクティブを達成させたことが示されています。

[目次] で [解析情報] をクリックします。この章の一番下の Constraints 節までスクロールします。

この節には、Switch ブロックの制御信号の値を区間 [–0.1, 0.1] に制約するために追加した Test Condition ブロックがリストされています。

[目次] で [テスト オブジェクティブのステータス] をクリックします。

この表には、生成された 2 つのテスト ケースを通じて Simulink Design Verifier が Switch ブロックの両方のテスト オブジェクティブを達成していることが示されます。

表の [テスト ケース] 列の [1] をクリックします。

この節には、モデル内でオブジェクティブを達成するために生成されたテスト ケースに関する詳細が示されます。このテスト ケースは、Switch ブロックが 3 番目の入力を出力端子に渡すときにテスト オブジェクティブ 1 を達成します。Test Condition ブロックでは入力信号の領域が間隔 [–0.1, 0.1] に制限されていますが、Switch ブロックの制御信号に対する値 –0.1 はこのオブジェクティブを達成させることが判別されます。

テスト ケースが 100% の判定カバレッジを達成することを確認するため、ハーネス モデルを開きます。

Inputs ブロックをダブルクリックして [信号エディター] ダイアログ ボックスを開きます。

ハーネス モデルのツールストリップで [すべて実行 (カバレッジ)] をクリックします。

Simulink ソフトウェアが両方のテスト ケースを使用してハーネス モデルのシミュレーションを行い、モデル カバレッジ情報を収集してカバレッジ レポートを表示します。このレポートの概要節には、Simulink Design Verifier がモデル例の完全な判定カバレッジを達成するテスト ケースを生成したことが示されています。

矛盾モデルの解析

解析によりエラー「The model is contradictory in its current configuration」が生成される場合、モデル内に矛盾が検出されているため、モデルを解析できません。

無効なパラメーターをもつ Test Objective ブロックがモデルにある場合、矛盾が生じることがあります。たとえば、信号が定数 10 である場合に信号は 0 ~ 5 でなければならないと規定されているオブジェクティブなどが矛盾になります。

矛盾が検出されると、それ以前の結果はすべて無効にされ、達成されないオブジェクティブがあることがレポートされます。