Test Condition

テスト ケースでの信号値の制限

ライブラリ:

Simulink Design Verifier /

Objectives and Constraints

説明

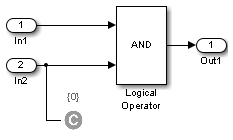

Test Condition ブロックは、テスト生成モードで動作しているモデル内の信号のテスト条件を定義します (Workflow for Test Generationを参照)。[値] パラメーターを使用して、信号値に関する制限を指定します。このブロックは、指定された [値] パラメーターを入力信号に適用し、テスト ケースの生成を試みます。

このブロックを使用すると次のことが可能です。

条件を有効または無効にします。

Simulink® エディターで、ブロックの [値] パラメーターを表示するかどうかを指定します。

ブロックの出力端子を表示するかどうかを指定します。

Simulink および Simulink Coder™ を使用してコードを生成すると、Test Condition ブロックは無視されます。Test Condition ブロックは、モデルのシミュレーション中に信号を変更せず、信号のみを使用してテスト条件を生成します。

例

制限

非バーチャル バスを入力としてもつ Test Condition ブロックは、Simulink Design Verifier™ 解析と互換性がありません。

端子

入力

出力

依存関係

この端子を有効にするには、[パス スルー スタイル (出力端子を表示)] を選択します。

パラメーター

拡張機能

バージョン履歴

R2007a で導入