このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

FPGAデータキャプチャを使用してOFDMの送受信を検証する

この例では、OFDM Transmit and Receive Using Analog Devices AD9361/AD9364 (SoC Blockset) で生成したワイヤレス HDL IP を検証する方法を示します。この例では、実際のハードウェア上で FPGA データ キャプチャを使用して IP コアの内部信号を監視および分析する方法も示します。

デバッグ分析のために JTAG 経由でハードウェア信号をキャプチャするには、FPGA データ キャプチャ ツールを使用します。FPGA データ キャプチャは、適切なトリガーおよびキャプチャ条件を使用して、対象の信号をキャプチャするための多くの機能を提供します。次の手順を実行して、zynqRadioHWSWOFDMAD9361AD9364SL モデル内の whdlOFDMRx Model サブシステムの動作を検証します。

キャプチャ コントロールを使用して、有効なデータ コンステレーション ポイントをキャプチャします。

トリガー条件と複数のウィンドウを使用して、CRC に失敗したフレームのヘッダー コンステレーション ポイントをキャプチャします。

トリガー条件とトリガー位置を使用して、ピーク検索の同期シーケンス (SS) 相関データをキャプチャし、タイミング オフセットを検証します。

要件

この例を実行するには、Xilinx Zynq ZC706 評価キットと FMCOMMS2/3/4 無線送信機ハードウェアが必要です。

ハードウェア セットアップ

Set Up AMD FPGA and SoC Devices (SoC Blockset) の手順に従って、ホスト コンピューターと ZC706 ボードを FMCOMMS2/3/4 無線ハードウェアで構成します。

JTAG ケーブルを使用してボードをホスト コンピューターに接続します。

Simulink モデル設定

zynqRadioHWSWOFDMAD9361AD9364SL.slx モデルを開きます。

データキャプチャを通じて分析する信号をテストポイントとしてマークします。信号をテスト ポイントとしてマークするには、信号を右クリックし、[プロパティ] をクリックします。シグナル プロパティ ダイアログ ボックスの ログ記録とアクセシビリティ タブで、次の図に示すように テスト ポイント チェック ボックスをオンにします。

または、hOFDMTxRxAddTestPoints ヘルパー関数を使用して必要なテスト ポイントをマークし、モデルを zynqRadioHWSWOFDMAD9361AD9364SLVerify として保存します。この関数は、サポート ファイルとして例に添付されています。

hOFDMTxRxAddTestPoints

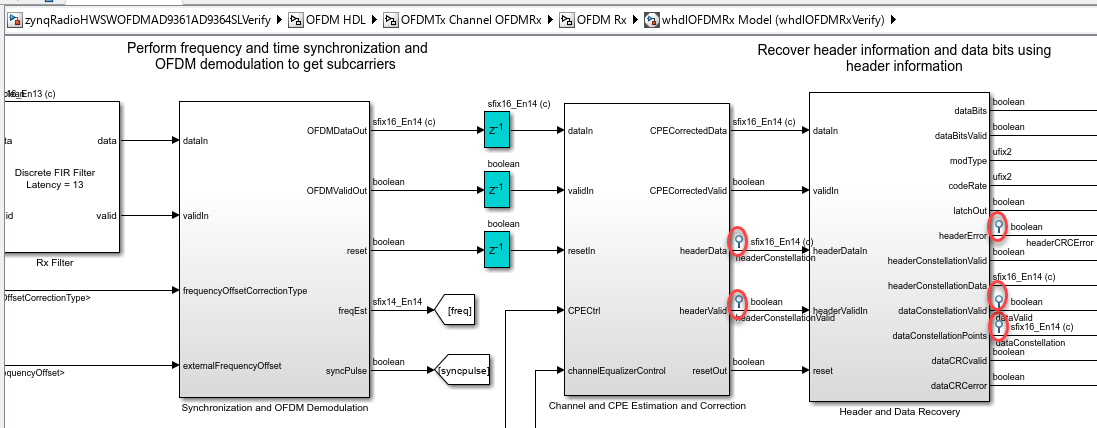

この図は、ヘッダーとデータ コンステレーション ポイントをキャプチャするために whdlOFDMRx Model サブシステムにマークされたテスト ポイントを示しています。

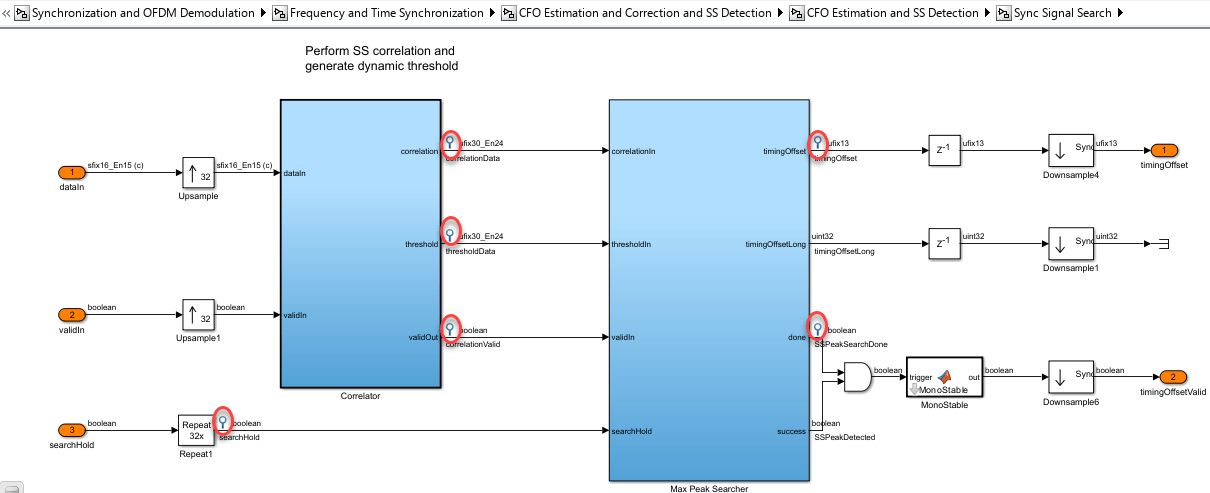

この図は、SS 相関およびタイミング オフセット信号をキャプチャするために Sync Signal Search サブシステムにマークされたテスト ポイントを示しています。

データキャプチャとビットストリームのロードを含む HDL IP コアの生成

OFDM HDLサブシステムを右クリックし、HDL コード > HDL ワークフロー アドバイザー を選択して、ターゲティング ワークフローを開始します。手順 1.1 で、[ターゲット ワークフロー] を

IP Core Generation、[ターゲット プラットフォーム] をZC706 and FMCOMMS2/3/4に設定します。手順 1.2 で、[リファレンス設計] を

Receive and Transmit pathに設定します。この例では、リファレンス デザイン パラメータのデフォルト値を使用できます。ステップ 1.3 で、テスト ポイントの HDL DUT 出力ポート生成を有効にする を選択して、すべてのテスト ポイントでインターフェイス テーブルを更新します。次に、ターゲット プラットフォーム インターフェイス テーブル で、テスト ポイント信号を

FPGA Data Captureにマップします。IO ポートのマッピングの詳細については、OFDM Transmit and Receive Using Analog Devices AD9361/AD9364 (SoC Blockset) を参照してください。

OFDM Transmit and Receive Using Analog Devices AD9361/AD9364 (SoC Blockset) の例の IP コアの生成セクションに従って、手順 1.4 から手順 3.1 を実行します。

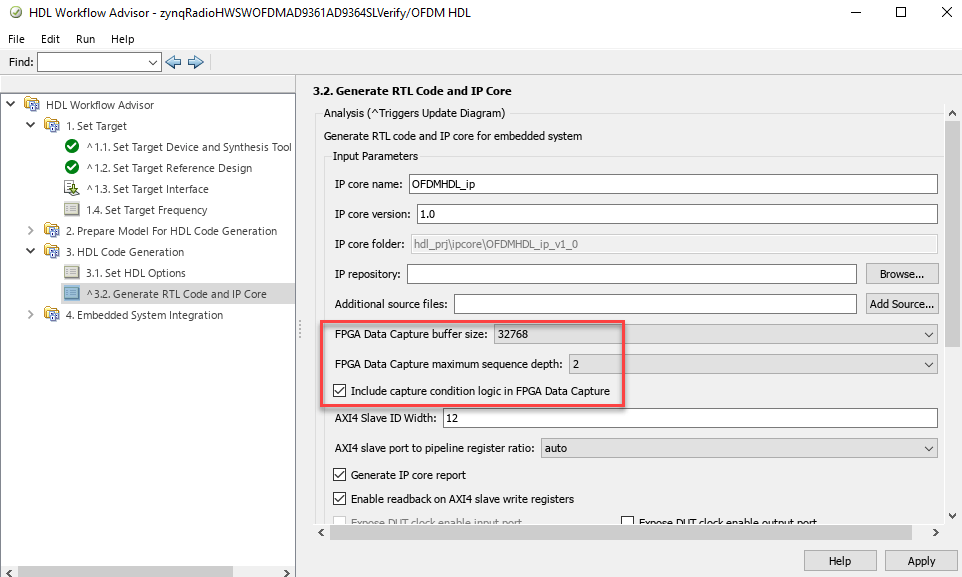

ステップ 3.2 で、FPGA データ キャプチャ バッファ サイズ を

32768に設定し、FPGA データ キャプチャ最大シーケンス深度 を2に設定します。この図に示すように、生成された FPGA データ キャプチャ コンポーネントにキャプチャ制御ロジックを挿入するには、FPGA データ キャプチャにキャプチャ条件ロジックを含める を選択します。

ステップ 4.1 を実行し、OFDM Transmit and Receive Using Analog Devices AD9361/AD9364 (SoC Blockset) の例の「ソフトウェア インターフェイス モデルとブロック ライブラリの生成」セクションの手順に従って、ソフトウェア インターフェイス モデルを生成します。

ビットストリームを生成してボードにダウンロードするには、OFDM Transmit and Receive Using Analog Devices AD9361/AD9364 (SoC Blockset) の例の「ビットストリームの生成とロード」セクションに従ってください。

または、hOFDMTxRxRunHDLWATasks ヘルパー関数を実行して、ステップ 1.1 からステップ 4.3 までのタスクを実行します。この関数は、サポート ファイルとして例に添付されています。

hOFDMTxRxRunHDLWATasks

IPコアからデータをキャプチャして分析する

生成された IP コアのテスト ポイントをキャプチャし、FPGA データ キャプチャにマップします。FPGA データ キャプチャがトリガーを待機している間にソフトウェア インターフェイス モデルを実行するには、非ブロッキング モードで FPGA データ キャプチャ ツールを起動します。

cd(fullfile('hdl_prj','hdlsrc', ... 'zynqRadioHWSWOFDMAD9361AD9364SLVerify','fpga_data_capture')); fdc = FPGADataCapture; fdc.CaptureMode = 'nonBlocking'; fdc.launchApp;

OFDM ソフトウェア インターフェイス モデルを開きます。Simulink モデルから構成を制御するには、モデルを Monitor & Tune モードで実行します。

open_system('zynqRadioHWSWOFDMAD9361AD9364SL_interface');

データ コンステレーション ポイントをキャプチャ

Channel and CPE Estimation and Correction サブシステムからの周波数領域、チャネルイコライズ、共通位相誤差 (CPE) 補正済みのデータ サブキャリアを使用して、データ コンステレーション ダイアグラムをプロットします。有効なデータ コンステレーション ポイントのみをキャプチャするには、次の図に示すように、FPGA データ キャプチャ ツールの キャプチャ条件 タブで キャプチャ条件ロジックを有効にする を選択し、値 High を持つ信号として tp_dataValid_1 を追加します。データのキャプチャをクリックします。

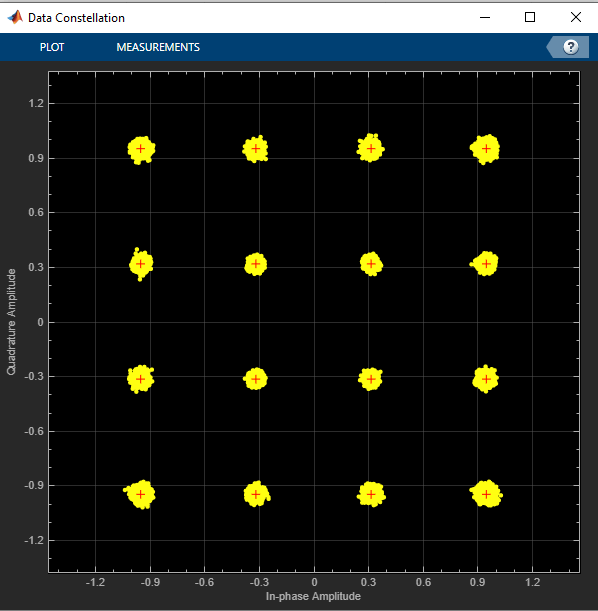

データのキャプチャが完了したら、ボードがキャプチャしたデータを使用して星座図をプロットします。

ソフトウェア インターフェイス モデルの enableInternaLoopback が false の場合、無線ハードウェアはそれぞれ Tx アンテナと Rx アンテナを介して OFDM 信号を送受信します。チャネル障害により、信号が無線で伝送される際にリアルタイムで信号が変化します。このシナリオでは、コンステレーション プロットを使用して受信信号の品質を分析します。また、ソフトウェア インターフェイス モデルで modType を変更し、データ コンステレーション ダイアグラムが期待どおりに表示されることを確認することもできます。

hOFDMTxRxPlotDataConstellationFDC

失敗した CRC のヘッダー コンステレーション ポイントをキャプチャする

チャネルの信号対雑音比 (SNR) が低い場合、チャネル イコライゼーションと CPE 修正後の有効なヘッダー データに CRC エラーが発生することがよくあります。ソフトウェア インターフェイス モデルを使用してこれらの条件をエミュレートできます。

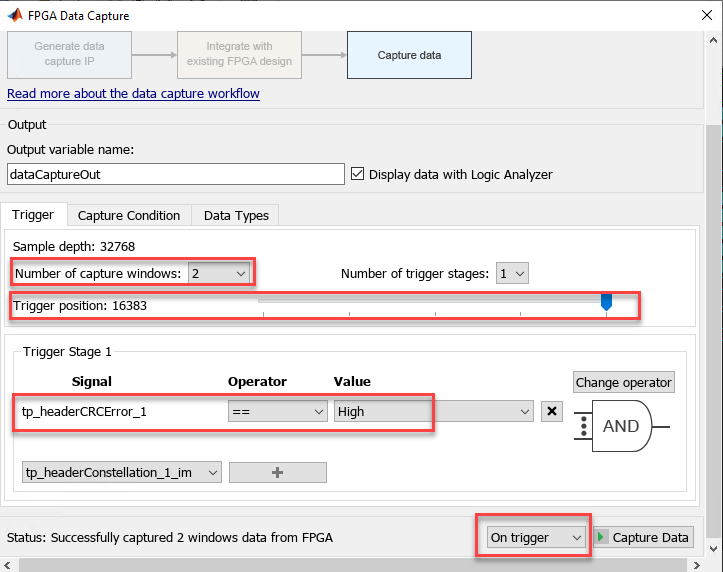

ソフトウェア インターフェイス モデルでは、enableInternalLoopback を true に、snrdB を 3 に設定します。これらのトリガー設定を使用して、CRC が失敗したときに 2 つのヘッダー フレームの I/Q データをキャプチャします。

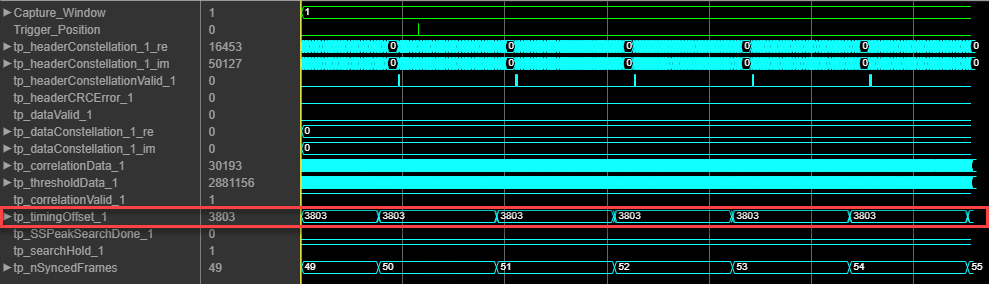

データのキャプチャをクリックします。DSP System Toolbox™ ライセンスをお持ちの場合、ロジック アナライザー アプリはキャプチャしたデータを複数の信号波形としてプロットします。キャプチャされたデータ内の信号 tp_nSyncedFrames は、CRC に失敗したフレームの番号を示します。

Sync Signal Search サブシステムの機能の検証

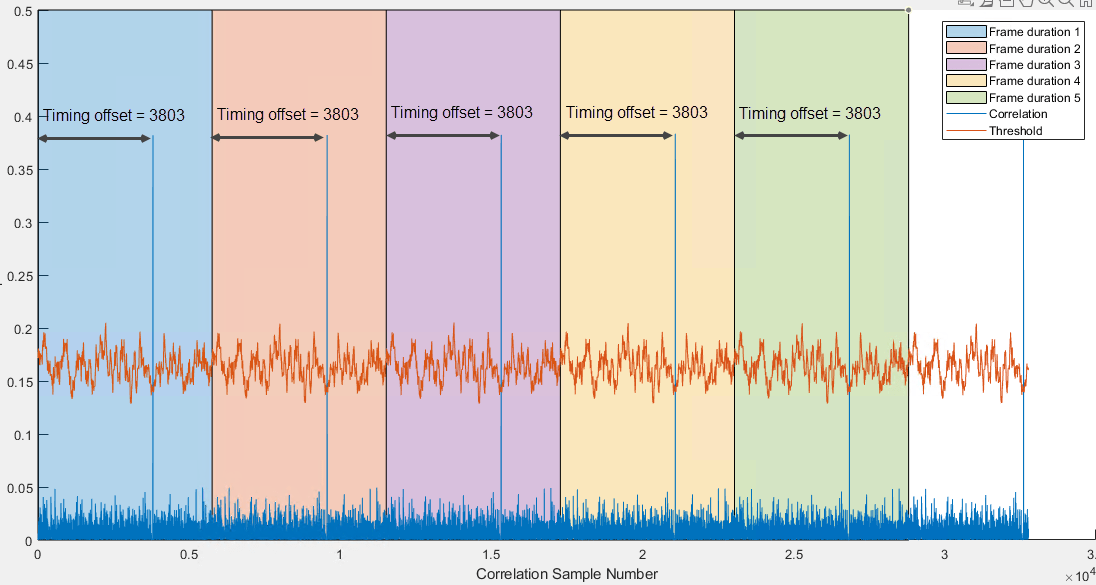

Sync Signal Search サブシステムは SS 相関を実装します。サブシステムは、受信信号と SS 信号を時間領域で継続的に相互相関させることにより SS 検出を実行します。さらに、サブシステムは各時間ステップで相関器の範囲内の信号のエネルギーを計算し、値をスケーリングしてしきい値を生成します。Max Peak Searcher サブシステムは、各 OFDM フレーム期間の最大相関ピークを検索します。Sync Signal Search サブシステムでは、SearchHold 信号は、搬送周波数オフセットを推定するまで最大ピーク検索を無効にします。SSPeakSearchDone 信号は、各 OFDM フレーム期間のピーク検索が完了するとハイになります。FFT 長さが 128 の場合、フレーム期間は 5760 サンプルになります。フレーム期間の開始からの最大ピークの位置によってタイミング オフセットが決まります。各 OFDM フレーム期間で有効な相関サンプルをキャプチャして、相関データを視覚化し、タイミング オフセットを記録できます。

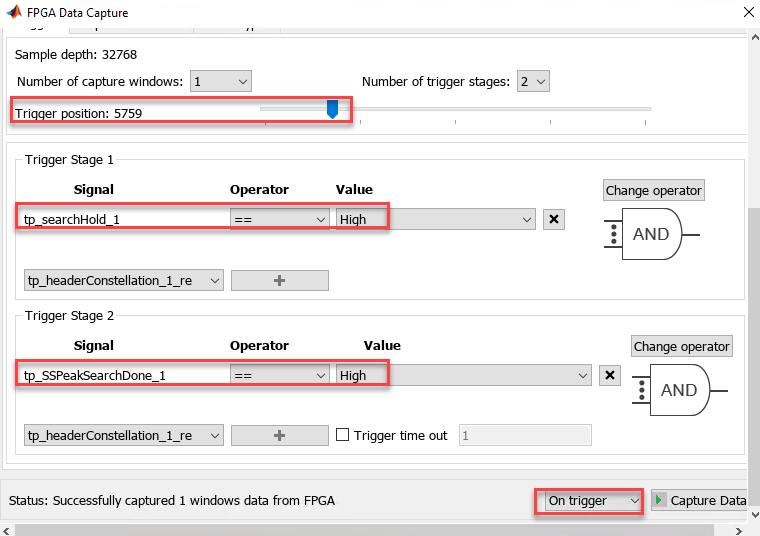

トリガー タブで、トリガー ステージ 1 に値 High を持つ信号として tp_searchHold_1 を追加します。各フレーム期間の相関データをキャプチャするには、トリガー ステージ 2 に値 High を持つ信号として tp_SSPeakSearchDone_1 を追加し、トリガー位置 を 5759 に設定します。これらの設定により、信号がこれらのトリガーを満たす前に、ツールが 5760 個の有効な相関サンプルをキャプチャすることが保証されます。サンプル 5761 から 11520 は、次の OFDM フレーム期間の相関に対応します。

各フレーム期間で有効な相関データをキャプチャするには、[キャプチャ条件] タブで [キャプチャ条件ロジックを有効にする] を選択します。この図に示すように、値 High を持つ信号として tp_correlationValid_1 を追加します。

データのキャプチャをクリックします。ロジック アナライザー は、キャプチャしたデータを複数の信号波形として表示します。

hOFDMTxRxPlotSSCorrelation ヘルパー関数を実行して、キャプチャされた相関値としきい値をプロットしてピークを視覚化します。フレーム期間の開始に対する各フレームのピークのインデックスによってタイミング オフセットが与えられます。

hOFDMTxRxPlotSSCorrelation

まとめ

この例では、IP コアの内部信号を FPGA データ キャプチャにマップし、設計を FPGA にデプロイした後に信号を視覚化する方法を示します。対象の信号をキャプチャするには、FPGA データ キャプチャ ツールのトリガーおよびキャプチャ制御構成を使用します。このアプローチを使用して、独自の HDL IP コアを分析およびデバッグできます。

参考

FPGA Data Capture | hdlverifier.FPGADataReader