このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Logic and Bit Operations ライブラリでのブロックの使用方法

これらのガイドラインでは、[Logic and Bit Operations] ライブラリのブロックから HDL 対応コードを生成する設計をモデル化する方法を示します。ライブラリには論理演算とビット演算、ビット リダクション、連結を実行するブロックが含まれます。各ガイドラインに準拠要件のレベルを示す重大度レベルが割り当てられています。詳細については、HDL モデリング ガイドラインの重大度レベルを参照してください。

論理ビット シフト演算および算術ビット シフト演算

ガイドライン ID

2.2.1

重大度

情報

説明

Simulink® ブロックを使用してビット シフト演算を実行できます。ブロックは、論理ビット シフトと算術ビット シフトを実行できます。左への論理ビット シフトと算術ビット シフトでは同じ結果が得られますが、次の表に示すように、右への論理シフトと算術シフトでは異なった演算が行われます。

| ブロック/関数名 | パラメーター/演算 | 等価の Verilog または SystemVerilog コード | 等価の VHDL コード | コメント |

|---|---|---|---|---|

| Bit Shift | Shift Left Logical | <<< | sll (sll と SHIFT_LEFT は VHDL で同じです。 | このモードはブロックの既定のモードです。左シフト演算は符号ビットを保持しません。入力が符号付きデータ型を使用し、正の値である場合、左シフト演算は 0 を LSB (最下位ビット) 側の空のビットにシフトします。 |

Shift Right Logical | >> | srl | このモードは符号ビットを保持しません。入力が符号付きデータ型を使用し、正の値である場合、右シフト演算は 0 を MSB (最上位ビット) 側の空のビットにシフトします。 | |

Shift Right Arithmetic | >>> | SHIFT_RIGHT | 入力が符号付きデータ型の場合、符号ビットが保持され、その他のビットは右にシフトします。 | |

Shift Arithmetic ブロックの関数 bitshift | 正の値/算術右シフト | >>> | SHIFT_RIGHT | 入力が符号付きデータ型の場合、符号ビットが保持され、その他のビットは右にシフトします。 |

| 負の値/算術左シフト | <<< | sll | このモードは符号ビットを保持しません。入力が符号付きデータ型を使用し、正の値である場合、左シフト演算は 0 を LSB 側の空のビットにシフトします。このモードはアンダーフローとオーバーフローをチェックしません。 | |

bitsll 関数 | なし/論理左シフト | <<< | sll | このモードは符号ビットを保持しません。生成された HDL コードは Bit Shift ブロックの [Shift Left Logical] モードで生成される場合と同じになります。 |

bitsrl 関数 | なし/論理右シフト | >> | srl | このモードは符号ビットを保持しません。生成された HDL コードは Bit Shift ブロックの [Shift Right Logical] モードで生成される場合と同じになります。 |

bitsra 関数 | なし/算術右シフト | >>> | SHIFT_RIGHT | 入力が符号付きデータ型の場合、符号ビットが保持され、その他のビットは右にシフトします。生成された HDL コードは Bit Shift ブロックの [Shift Right Arithmetic] モードで生成される場合と同じになります。 |

論理シフトと算術シフトの違いは、符号ビットが保持されるかどうかです。符号付きデータ型の場合、このビットは MSB です。論理右シフトでは、符号ビットは右にシフトされ、MSB 側にゼロが入ります。算術右シフトでは、MSB (符号ビット) はシフト演算時に保持されます。たとえば、このコードは関数間の差異を示しています。

A = fi([], 1, 4, 0, 'bin','1011'); B = bitsrl(A, 2)

B =

2

DataTypeMode: Fixed-point: binary point scaling

Signedness: Signed

WordLength: 4

FractionLength: 0B.bin

ans =

'0010'C = bitsra(A, 2)

C =

-2

DataTypeMode: Fixed-point: binary point scaling

Signedness: Signed

WordLength: 4

FractionLength: 0C.bin

ans =

'1110'

Logical Operator ブロック、Bitwise Operator ブロック、Bit Reduce ブロックの使用方法

ガイドライン ID

2.2.2

重大度

情報

説明

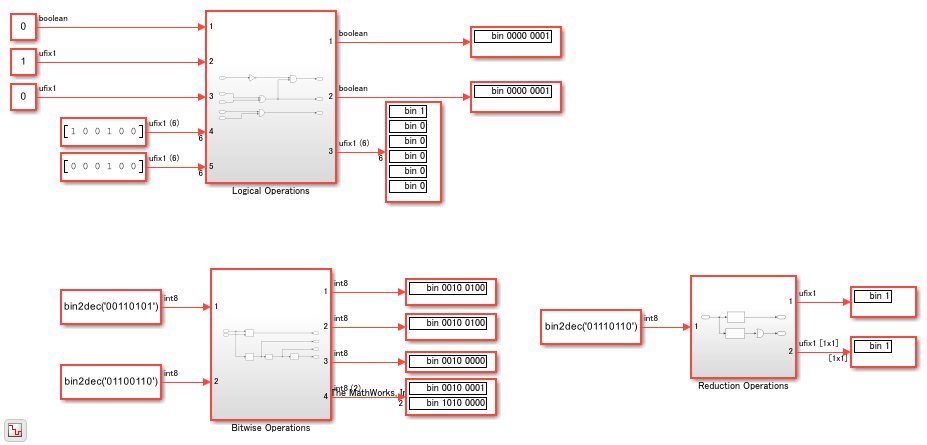

論理演算とビット演算の例については、モデル hdlcoder_logical_bitwise_operations.slx を開いてください。

load_system('hdlcoder_logical_bitwise_operations') sim('hdlcoder_logical_bitwise_operations') open_system('hdlcoder_logical_bitwise_operations')

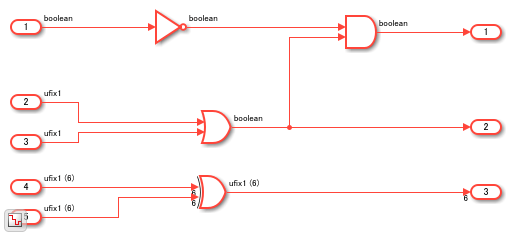

Boolean データ型または ufix1 データ型を使用するシングルビット演算では、Logical Operator ブロックを使用します。ブロックの [ブロック パラメーター] ダイアログ ボックスで演算を論理回路記号として表示するには、[アイコン形状] を Distinctive として指定します。Boolean データ型または ufix1 データ型をもつベクトルをブロックに入力することもできます。

Boolean と ufix1 は異なるデータ型です。両方のデータ型を同じモデル内で使用したり、置き換えて使用したりすることは避けてください。Simulink データ型の考慮事項を参照してください。

ブロックの使用例については、Logical Operations サブシステムを開いてください。

open_system('hdlcoder_logical_bitwise_operations/Logical Operations')

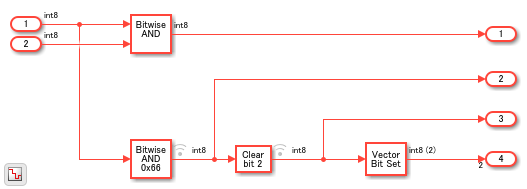

整数または固定小数点データ型を使用する 2 つ以上のビットのビット演算の場合、Bitwise Operator ブロックを使用します。例については、Bitwise Operations サブシステムをダブルクリックしてください。

open_system('hdlcoder_logical_bitwise_operations/Bitwise Operations')

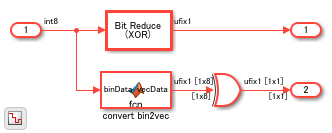

Boolean または ufix1 を使用するベクトルでビットごとのリダクション演算を実行して 1 ビット値を返すには、Bit Reduce ブロックを使用します。例については、Reduction Operations サブシステムをダブルクリックしてください。

open_system('hdlcoder_logical_bitwise_operations/Reduction Operations')

サブシステム内の MATLAB Function ブロックは、8 ビット ベクトルを 8 つの 1 ビット ufix1 要素のベクトルに変換します。

open_system('hdlcoder_logical_bitwise_operations/Reduction Operations/convert bin2vec')

Compare to Constant ブロックと Relational Operator ブロックでの boolean 出力の使用

ガイドライン ID

2.2.3

重大度

強く推奨

説明

Compare To Constant ブロック、Compare To Zero ブロック、Relational Operator ブロックの場合、uint8 または boolean を [出力データ型] として指定できます。これらのブロックが含まれるモデルに効率的な HDL コードを生成する場合、HDL コードは LSB のみを接続しなければならないため、boolean を [出力データ型] として指定します。

Relational Operator ブロックの場合、両方の入力が同じデータ型であることを確認します。入力に異なるデータ型を使用すると、符号ビットなどのビットで意図しない切り捨てが発生し、それによって HDL コードの生成後にシミュレーションの不一致が生じる可能性があります。

モデルで Relational Operator ブロックが同じ入力データ型を使用し、boolean を出力データ型として使用するかどうかを検証するには、Relational Operator ブロックの使用をチェックの HDL モデル チェックを実行します。