FPGA ターゲットの効率的な乗算演算と除算演算のモデル化

以下のガイドラインでは、ターゲット FPGA 上の面積およびタイミングを改善するためにモデルで Divide ブロックと Product ブロックを使用するときの推奨設定を示します。各ガイドラインに準拠要件のレベルを示す重大度レベルが割り当てられています。詳細については、HDL モデリング ガイドラインの重大度レベルを参照してください。

FPGA で DSP ブロックへの効率的なマッピングを行うための乗算器と加算器の設計

ガイドライン ID

2.7.1

重大度

強く推奨

説明

デジタル信号処理 (DSP) アルゴリズムでは、複数の乗算器とアキュムレータを使用します。Xilinx® や Intel® などのベンダーが提供する FPGA デバイスには専用の DSP スライスが含まれています。これらの小型で、高速な DSP スライスには、FPGA デバイスを DSP アプリケーションに最適なものにするいくつかの乗算器とアキュムレータが含まれます。

DSP スライスのアーキテクチャは、各 FPGA ベンダー、および同じベンダーが提供しているデバイスのファミリによって大きく異なります。加算器、乗算器、および遅延を含む Simulink® モデルを DSP スライスにマッピングするには、次の点を考慮して DSP スライス アーキテクチャに適用します。

DSP スライスのフリップフロップ、加算器、および乗算器の調整。

丸めと飽和設定。

加算器と乗算器のビット幅。効率的なマッピングにするには、DSP ユニットのビット幅以下のビット幅をモデルで使用します。

モデルでのビット幅が DSP のビット幅よりも大きくなった場合、設計は DSP に適合しません。この場合は、複数の DSP または追加のロジックが必要です。

モデルの以下のブロックを FPGA の DSP ブロックにマッピングできます。

Add および Sum

Delay

Product

Multiply-Add

Multiply-Accumulate

DSP48E1 スライスのアーキテクチャ

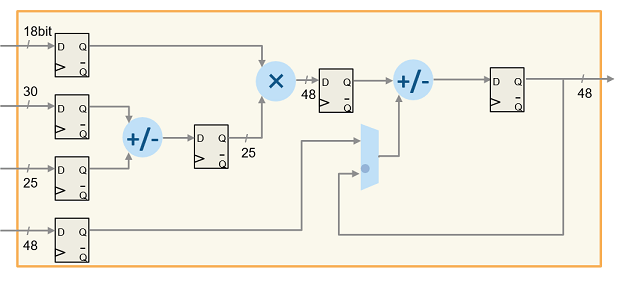

この図は、XilinxDSP アーキテクチャを示しています。Xilinx 7 シリーズの FPGA には、このアーキテクチャを使用する専用の DSP スライスがあります。DSP アーキテクチャは、入力レジスタ、pre-adder、25x18 乗算器、中間レジスタ、post-adder、および出力レジスタで構成されています。

詳細については、Xilinx ドキュメンテーションで「DSP48E1 Slice Overview」を参照してください。

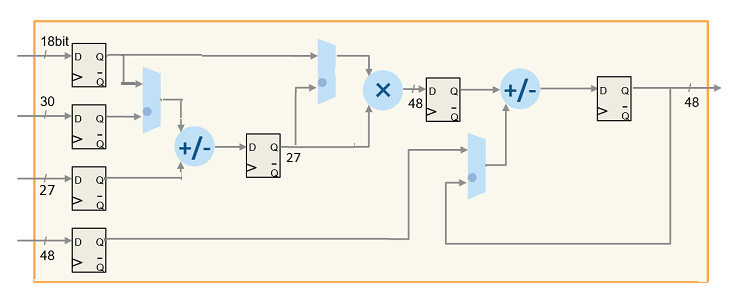

DSP48E2 スライスのアーキテクチャ

この図は、XilinxDSP アーキテクチャを示しています。Xilinx UltraScale® シリーズの FPGA には、このアーキテクチャを使用する専用の DSP スライスがあります。DSP アーキテクチャは、入力レジスタ、前置加算器、27x18 乗算器、中間レジスタ、後置加算器、および出力レジスタで構成されています。

詳細については、Xilinx ドキュメンテーションで "UltraScale Architecture DSP Slice Overview" を参照してください。

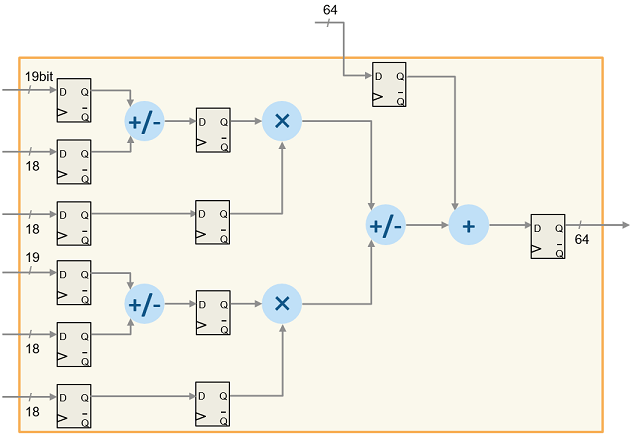

Stratix® V デバイスのアーキテクチャ

この図は、Intel DSP アーキテクチャを示しています。Stratix® V デバイスのこの DSP アーキテクチャは、可変精度の DSP アーキテクチャです。DSP ブロックは、9 ビット、18 ビット、27 ビット、36 ビットのビット幅、および FFT 用の 18x25 複素数乗算をもつことができます。

詳細については、Stratix V デバイスの DSP ブロック アーキテクチャを参照してください。

アルゴリズム設計

この DSP ユニットにマッピングするアルゴリズムを設計する方法を確認するには、モデル hdlcoder_multiplier_adder_dsp.slx を開きます。

open_system('hdlcoder_multiplier_adder_dsp'); set_param('hdlcoder_multiplier_adder_dsp', 'SimulationCommand', 'Update');

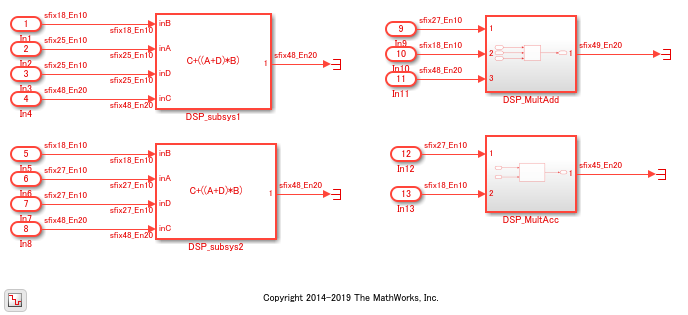

このモデルは、演算 C+((A+D)*B を実装する 2 つのサブシステム DSP_subsys1 と DSP_subsys2 で構成されています。また、サブシステム DSP_MultAdd と DSP_MultAcc で示されているように、Multiply-AddブロックまたはMultiply-Accumulateブロックを使用してこの演算を実装することもできます。

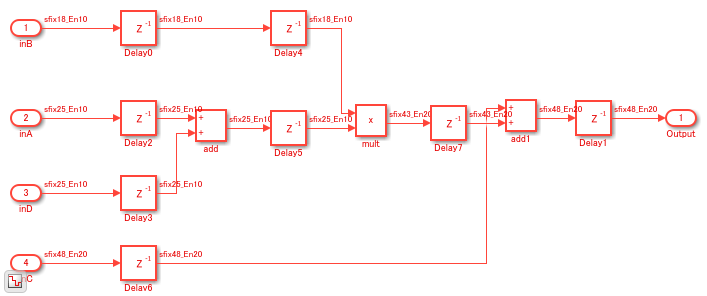

演算 C+((A+D)*B の実装を確認するために、モデル DSP_subsys1 を開きます。

open_system('hdlcoder_multiplier_adder_dsp/DSP_subsys1');

演算 C+((A+D)*B の実装を確認するために、モデル DSP_subsys2 を開きます。

open_system('hdlcoder_multiplier_adder_dsp/DSP_subsys2');

Xilinx 7 シリーズの FPGA での実装

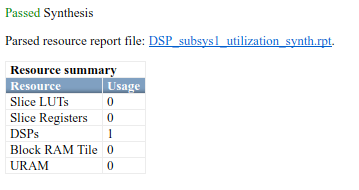

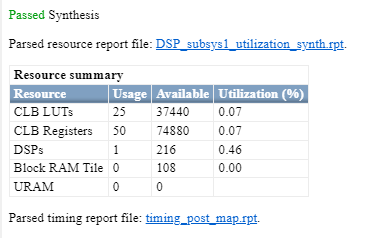

DSP_subsys1 は、Xilinx 7 シリーズの FPGA の DSP に一致するビット幅を使用して演算 C+((A+D)*B を実装します。HDL ワークフロー アドバイザーを開いて、このサブシステムを Xilinx Virtex® 7 FPGA に展開すると、設計全体が単一の DSP スライスにちょうど収まります。

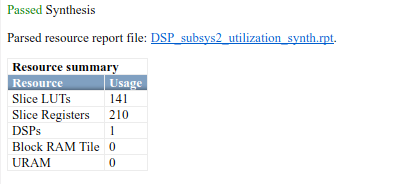

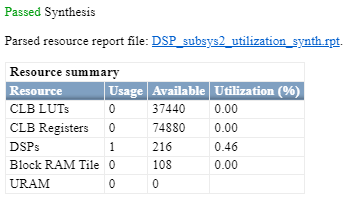

DSP_subsys2 は、Xilinx FPGA の DSP よりも大きいビット幅を使用して同じ演算を実装します。このサブシステムを Xilinx Virtex 7 FPGA に展開すると、設計全体が単一の DSP スライスに収まらず、代わりに追加のスライス ロジックが使用されることがわかります。

Xilinx UltraScale FPGA での実装

DSP_subsys1 は、Xilinx UltraScale FPGA の DSP より小さいビット幅を使用して演算 C+((A+D)*B を実装します。HDL ワークフロー アドバイザーを開いてこのサブシステムを Xilinx Artix UltraScale® FPGA に展開すると、設計全体が単一の DSP スライスに収まらず、代わりに追加のロジックが使用されます。

DSP_subsys2 は、Xilinx UltraScale FPGA の DSP に一致するビット幅を使用して同じ演算を実装します。このサブシステムを Xilinx Artix UltraScale® FPGA に展開すると、設計全体が単一の DSP スライスに収まることがわかります。

Gain ブロックについては [ConstMultiplierOptimization] HDL ブロック プロパティを auto に設定

ガイドライン ID

2.7.2

重大度

強く推奨

説明

設計で Gain ブロックを使用する場合、最も面積効率の高い実装を得るには、ConstMultiplierOptimization HDL ブロック プロパティを [auto] に設定します。コード ジェネレーターで、[CSD] と [FCSD] から回路サイズが最小となる実装が選択され、乗算 (*) 演算子を使用せずに HDL コードが生成されます。

この設定を使用することで、設計をターゲット FPGA で合成する際に、DSP リソースをターゲットから除外して Intel® Quartus® Prime の論理回路の数を少なくすることができます。次の表に、HDL ブロック プロパティの [ConstMultiplierOptimization] の設定に応じて Gain ブロックの生成される HDL コードがどのように異なるかに関する例を示します。

ConstMultiplierOptimization の設定とそれぞれで生成される HDL コード

ConstMultiplierOptimization の設定 | 演算 | 生成される HDL コード |

|---|---|---|

CSD | 入力データを並列にキャストし、結果を加算または減算します。

| 次のコードは生成される VHDL コードを示しています。 -- CSD Encoding(231): 1001'01001'; Cost (Adders) = 3 DOUT_mul_temp <= ((resize(DIN & '0' & '0' & '0' & '0' & '0' & '0' & '0' & '0', 21) - resize(DIN & '0' & '0' & '0' & '0' & '0', 21)) + resize(DIN & '0' & '0' & '0', 21)) - resize(DIN, 21); DOUT <= DOUT_mul_temp(19 DOWNTO 0); 次のコードは生成される Verilog コードを示しています。 // CSD Encoding (231) : 1001'01001'; Cost (Adders) = 3

assign Gain_1 = {DIN[11], {DIN, 8'b00000000}};

assign Gain_2 = {{4{DIN[11]}}, {DIN, 5'b00000}};

assign Gain_3 = {{6{DIN[11]}}, {DIN, 3'b000}};

assign Gain_4 = {{9{DIN[11]}}, DIN};

assign DOUT_mul_temp = ((Gain_1 - Gain_2) + Gain_3) - Gain_4;

assign DOUT = DOUT_mul_temp[19:0];

|

FCSD | 入力データとそのキャスト データをそれぞれのカスケードで加算します。

| 次のコードは生成される VHDL コードを示しています。 -- FCSD for 231 = 33 X 7; Total Cost = 2 -- CSD Encoding (33) : 0100001; Cost (Adders) = 1 Gain_factor <= resize(DIN & '0' & '0' & '0' & '0' & '0', 21) + resize(DIN, 21); -- CSD Encoding (7) : 1001'; Cost (Adders) = 1 DOUT_mul_temp <= resize(Gain_factor & '0' & '0' & '0', 21) - Gain_factor; DOUT <= DOUT_mul_temp(19 DOWNTO 0); 次のコードは生成される Verilog コードを示しています。 // FCSD for 231 = 33 X 7; Total Cost = 2

// CSD Encoding (33) : 0100001; Cost (Adders) = 1

assign Gain_3 = {{4{DIN[11]}}, {DIN, 5'b00000}};

assign Gain_4 = {{9{DIN[11]}}, DIN};

assign Gain_factor = Gain_3 + Gain_4;

// CSD Encoding (7) : 1001'; Cost (Adders) = 1

assign Gain_1 = {Gain_factor, 3'b000};

assign Gain_2 = Gain_1[20:0];

assign DOUT_mul_temp = Gain_2 - Gain_factor;

assign DOUT = DOUT_mul_temp[19:0];

|

auto | CSD と FCSD から使用する加算器が少ない方を選択します。 | 生成される HDL コードは CSD または FCSD の実装と同じです。 |

none | 乗算演算子 (*) を使用します。 | 次のコードは生成される VHDL コードを示しています。 DOUT_mul_temp <= to_signed(2#011100111#, 9) * DIN; DOUT <= DOUT_mul_temp(19 DOWNTO 0); 次のコードは生成される Verilog コードを示しています。 assign DOUT_mul_temp = 231 * DIN; assign DOUT = DOUT_mul_temp[19:0]; |

固定小数点型での Divide ブロックの ShiftAdd アーキテクチャの使用

ガイドライン ID

2.7.3

重大度

推奨

説明

固定小数点データ型を Divide ブロックへの入力として使用する場合は、ブロックの HDL アーキテクチャを ShiftAdd として指定します。このアーキテクチャでは、ブロックは複数のシフト演算と加算演算を使用して結果を計算します。演算はパイプライン化されて、ターゲットの FPGA デバイスでクロック周波数をさらに高くします。

浮動小数点データ型を Divide ブロックへの入力として使用する場合は、[浮動小数点の使用] コンフィギュレーション パラメーターを選択します。

固定小数点定数演算における Gain ブロックの使用

ガイドライン ID

2.7.4

重大度

強く推奨

説明

Product、Divide、または Trigonometric 演算ブロックへの入力として固定小数点データ型が構成されている Constant ブロックを使用している場合、それらの演算子を Gain ブロックまたは Constant ブロックに置き換えることで、設計の回路の面積を削減できます。定数入力をもつブロックに関する以下の設計上の考慮事項を検討してください。

Product ブロックの 1 つの入力が Constant ブロックである場合は、Product ブロックを Gain ブロックに置き換え、定数値を Gain ブロックの [ゲイン] の値として設定します。

Divide ブロックの約数入力が Constant ブロックである場合は、Divide ブロックを Gain ブロックに置き換え、定数値の逆数を Gain ブロックの [ゲイン] の値に設定します。

sin、cos、atan2などの Trigonometric Function ブロックへの入力が Constant ブロックである場合は、そのブロックを Constant ブロックに置き換え、計算値を Constant ブロックに設定します。たとえば、Sin ブロックへの入力がπ/3の場合、Sin ブロックを Constant ブロックに置き換え、定数値をsin(pi/3)に設定します。

変数と定数の演算に必要な回路の面積は異なります。定数の演算を使用することで、設計の回路の面積を削減できます。