ネイティブ浮動小数点を使用したターゲットに依存しない HDL コードの生成

HDL Coder™ のネイティブ浮動小数点テクノロジーによって、ターゲットに依存しない HDL コードを浮動小数点設計から生成できます。汎用 FPGA または ASIC で浮動小数点設計を合成できます。浮動小数点設計では、固定小数点設計に比べて、精度が向上し、ダイナミック レンジが高くなり、開発サイクルが短縮されます。設計に複雑な算術演算および三角関数演算がある場合は、ネイティブ浮動小数点テクノロジーを使用します。

HDL Coder でのターゲットに依存しない HDL コードの生成方法

この図は、HDL Coder でネイティブ浮動小数点テクノロジーを使用してコードを生成する方法を示しています。

Unpack ブロックと Pack ブロックは浮動小数点型を符号、指数、および仮数に変換します。この図において、S は符号、E は指数、M は仮数をそれぞれ表します。この解釈は浮動小数点演算の IEEE-754 標準に基づいています。

Floating-Point Algorithm Implementation ブロックは、S、E、および M について計算を実行します。この変換では、生成された HDL コードはターゲットに依存しません。汎用 FPGA または ASIC に設計を展開できます。

ネイティブ浮動小数点の有効化とコードの生成

ネイティブ浮動小数点を有効にして、Simulink® モデルまたは MATLAB® 関数から HDL コードを生成できます。

Simulink モデルのネイティブ浮動小数点の指定

HDL コード生成用のネイティブ浮動小数点設定は、[コンフィギュレーション パラメーター] ダイアログ ボックスまたはコマンド ラインで指定できます。

[コンフィギュレーション パラメーター] ダイアログ ボックスでネイティブ浮動小数点設定を指定して HDL コードを生成するには、次の手順に従います。

[アプリ] タブで、[HDL Coder] を選択します。[HDL コード] タブが表示されます。

[設定] をクリックします。[HDL コード生成] 、 [浮動小数点] ペインで、[浮動小数点の使用] を選択します。

[レイテンシ手法] を指定して設計を最大または最小のレイテンシあるいはレイテンシなしにマッピングします。レイテンシ手法を参照してください。

設計に非正規数がある場合は、[非正規化数の処理] をオンにします。非正規数は、ゼロに等しい指数フィールドおよび非ゼロ仮数フィールドをもつ数値です。Handle Denormalsを参照してください。

設計に乗算器がある場合、HDL Coder での乗算演算の実装方法を指定するには、[仮数乗算手法] パラメーターを使用します。

浮動小数点リソースを共有するには、[HDL コード生成] 、 [最適化] 、 [リソース共有] タブで、[浮動小数点 IP] を選択していることを確認します。共有されるブロック数は、サブシステムに指定した [SharingFactor] によって異なります。

[適用] をクリックします。[HDL コード] タブで、[HDL コードを生成] をクリックします。

コマンド ラインで HDL コード生成用のネイティブ浮動小数点を適用するには、関数 hdlcoder.createFloatingPointTargetConfig を使用します。この関数を使用して、ネイティブ浮動小数点ライブラリの hdlcoder.FloatingPointTargetConfig オブジェクトを作成できます。

nfpconfig = hdlcoder.createFloatingPointTargetConfig('NATIVEFLOATINGPOINT'); hdlset_param('sfir_single', 'FloatingPointTargetConfiguration', nfpconfig);

オプションで、レイテンシ手法と、HDL Coder により設計で非正規数を処理するかどうかを指定できます。

nfpconfig.LibrarySettings.HandleDenormals = 'on'; nfpconfig.LibrarySettings.LatencyStrategy = 'MAX';

生成されたコードを検証する方法については、ネイティブ浮動小数点から生成されたコードの検証を参照してください。

MATLAB 関数のネイティブ浮動小数点の指定

MATLAB HDL ワークフロー アドバイザーまたはコマンド ラインを使用して、HDL コード生成用のネイティブ浮動小数点設定を指定できます。

MATLAB HDL ワークフロー アドバイザーでネイティブ浮動小数点設定を指定するには、次の手順に従います。

MATLAB HDL ワークフロー アドバイザーを開きます。MATLAB HDL ワークフロー アドバイザーの使用を開始するには、HDL ワークフロー アドバイザーを使用した対称 FIR フィルター用の HDL コードの生成および合成を参照してください。

左側のペインで、[HDL コード生成] タスクをクリックします。右側のペインで、[浮動小数点] タブに移動し、[ライブラリ] を

[ネイティブ浮動小数点]に設定します。[クロックと端子] タブをクリックし、[オーバーサンプリング係数] を 1 よりも大きい値に設定します。

[レイテンシ手法] を

[最小値]、[最大値]、または[ゼロ]に設定して、設計をそれぞれ最小、最大、またはレイテンシなしにマッピングします。レイテンシ手法を参照してください。設計に非正規数がある場合は、[非正規化数の処理] をオンにします。非正規数は、ゼロに等しい指数フィールドおよび非ゼロ仮数フィールドをもつ数値です。Handle Denormalsを参照してください。

設計に乗算器がある場合、[仮数乗算手法] パラメーターを使用して、HDL Coder での乗算演算の実装方法を指定します。

左側のペインで、[HDL コード生成] タスクを右クリックし、[選択したタスクまで実行] を選択します。

コマンド ラインで HDL コード生成用のネイティブ浮動小数点を適用するには、関数 coder.config を使用して HDL コード生成用の coder.HdlConfig オブジェクトを作成し、関数 hdlcoder.createFloatingPointTargetConfig を使用してネイティブ浮動小数点ライブラリ用の hdlcoder.FloatingPointTargetConfig オブジェクトを作成します。

hdlcfg = coder.config("hdl"); nfpconfig = hdlcoder.createFloatingPointTargetConfig('NATIVEFLOATINGPOINT'); hdlcfg.FloatingPointLibrary = 'NativeFloatingPoint'; hdlcfg.FloatingPointTargetConfiguration = nfpconfig;

オプションで、レイテンシ手法と、HDL Coder により設計で非正規数を処理するかどうかを指定できます。

nfpconfig.LibrarySettings.HandleDenormals = 'on'; nfpconfig.LibrarySettings.LatencyStrategy = 'MAX';

コード生成レポートの表示

浮動小数点ライブラリ マッピングのコード生成レポートを表示するには、コード生成を開始する前にリソース利用レポートと最適化レポートの生成を有効にします。レポートを有効にするには、[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード] タブで [設定] 、 [レポート オプション] をクリックし、[HDL コード生成] ペインで [リソース利用レポートを生成] および [最適化レポートを生成] を有効にします。詳細については、コード生成レポートの作成と使用を参照してください。

HDL Coder がサポートするネイティブ浮動小数点演算子と、Simulink ブロックのマッピング先の浮動小数点演算子のリストを参照するには、[コード生成レポート] で [ネイティブ浮動小数点リソース レポート] を選択します。

詳細なレポートには、指定したターゲット デバイスで浮動小数点ブロックが使用するさまざまなリソースが表示されます。ネイティブ浮動小数点設計からの HDL コード生成では、指数値に基づく仮数の調整に動的シフト演算子を使用します。これらの動的なシフターはモデルでのリソース使用量が大きいため、静的シフト演算子とは別に報告されます。動的なシフターと静的なシフターの詳細については、コード生成レポートを使用した合成前のコードの評価を参照してください。

モデルに適用したネイティブ浮動小数点設定、および HDL Coder で HDL コードが正常に生成されたかどうかを確認するには、[コード生成レポート] で、[ターゲット コード生成] を選択します。

結果の解析

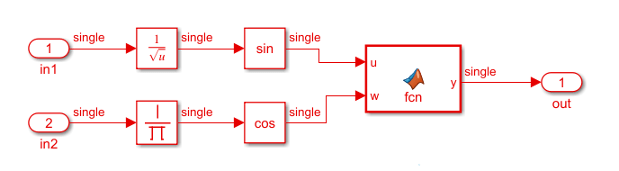

浮動小数点演算子にはレイテンシがあります。Simulink モデルが遅延を持たない場合、HDL コード生成時に、コード ジェネレーターは演算子レイテンシを割り出し、並列パスの遅延のバランスを取ります。2 つの single 入力があり、1 つの single 出力がある、この Simulink モデルについて考えます。

Simulink モデルの MATLAB Function ブロックには、このコードが含まれます。

function y = fcn(u, w) %#codegen y1 = (u+w) * 20; y2 = w^16; y3 = (u-w) / 10; y = y1 + y2 - y3;

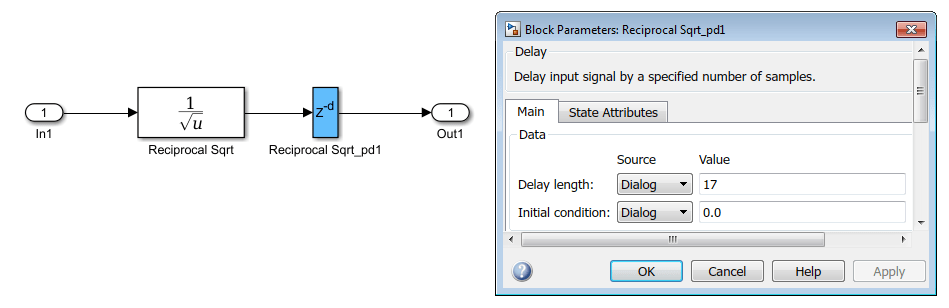

HDL コードを生成すると、コード ジェネレーターは Simulink モデルのブロックを合成可能なネイティブ浮動小数点演算子にマッピングします。コード ジェネレーターが浮動小数点演算を実装した方法を確認するには、生成されたモデルを開きます。NFP math ブロック、NFP Sqrt ブロック、および NFP trig ブロックは、それぞれ元のモデルにおける Reciprocal Sqrt ブロック、Reciprocal ブロック、sin ブロック、cos ブロックの浮動小数点実装に対応しています。

すべての浮動小数点演算子にはレイテンシがあります。Reciprocal Sqrt のレイテンシが 30 で、Reciprocal のレイテンシが 31 であるため、コード ジェネレーターは一致する遅延を追加で挿入しました。演算子のレイテンシは、NFP ブロック内の Delay ブロックの [遅延の長さ] と等しくなります。たとえば、NFP sqrt ブロックをダブルクリックすると、Delay ブロックの [遅延の長さ] を見ることで、レイテンシが分かります。浮動小数点演算子のレイテンシ値を参照してください。

浮動小数点データ型をもつ MATLAB Function ブロックを使用する場合、HDL Coder は MATLAB Datapath アーキテクチャを使用します。このアーキテクチャは、MATLAB Function ブロックを通常の Subsystem ブロックとして処理します。コードを生成する場合、コード ジェネレーターは、加算や乗算などの基本的な演算を対応するネイティブ浮動小数点演算子にマッピングします。コード ジェネレーターが MATLAB Function ブロックを実装した方法を確認するには、MATLAB Function サブシステムを開きます。

生成されたモデルの詳細については、生成されたモデルと検証モデルを参照してください。

制限

ネイティブ浮動小数点モードで HDL コードを生成するには、離散サンプル時間を使用します。連続サンプル時間で動作するブロックはサポートされません。