ネイティブ浮動小数点から生成されたコードの検証

HDL Coder™ のネイティブ浮動小数点テクノロジーによって、ターゲットに依存しない HDL コードを浮動小数点設計から生成できます。汎用 FPGA または ASIC で浮動小数点設計を合成できます。浮動小数点設計では、固定小数点設計に比べて、精度が向上し、ダイナミック レンジが高くなり、開発サイクルが短縮されます。設計に複雑な算術演算および三角関数演算がある場合は、ネイティブ浮動小数点テクノロジーを使用します。

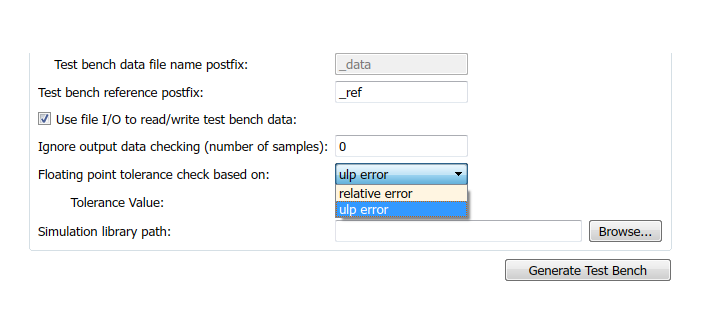

有限ビット数で無限実数を表現すると、IEEE-754 標準で指定されている正しい値の丸め範囲で丸め誤差が生じることがあります。丸め誤差を測定するには、[relative error] または [ulp error] に基づいて浮動小数点許容誤差チェックを指定できます。これらの丸め誤差の詳細については、相対精度と ULP の考慮事項を参照してください。

許容誤差手法の指定

テストベンチを生成する前に、生成されたコードを検証する浮動小数点許容誤差チェックを指定します。

[コンフィギュレーション パラメーター] ダイアログ ボックスで許容誤差チェックを指定するには、次の手順に従います。

[アプリ] タブで、[HDL Coder] を選択します。[HDL コード] タブが表示されます。

[設定] をクリックします。[HDL コード生成] 、 [テストベンチ] ペインの [浮動小数点許容誤差チェックの基準] で、

[相対誤差]または[ULP 誤差]を指定します。

[許容誤差の値] を入力し、[適用] をクリックします。

[relative error]を選択すると、既定は1e-07の許容誤差の値になります。[ulp error]を選択すると、既定の許容誤差の値は 0 になります。詳細については、ネイティブ浮動小数点の数値に関する考慮事項を参照してください。

コマンド ラインで許容誤差手法を指定するには、次の手順を使用します。

FPToleranceStrategyを使用して浮動小数点許容誤差チェック設定を指定します。% check for floating-point tolerance based on relative error hdlset_param('sfir_single', 'FPToleranceStrategy', 'Relative'); % check for floating-point tolerance based on the ULP error hdlset_param('sfir_single', 'FPToleranceStrategy', 'ULP');

FPToleranceStrategy設定に基づいて、FPToleranceValueを使用して許容誤差の値を入力します。% if using relative error, enter custom tolerance value hdlset_param('FP_test_16a', 'FPToleranceValue', 1e-06); % if using ULP error, enter tolerance value greater % than or equal to 1 hdlset_param('FP_test_16a', 'FPToleranceValue', 1);

HDL テスト ベンチを使用した生成されたコードの検証

生成されたコードを検証するために HDL テスト ベンチを生成するには、次の手順に従います。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [テスト ベンチ]ペインの [テスト ベンチ生成出力] で [HDL テスト ベンチ] を選択します。

[構成] セクションで、[ファイル I/O を使用してテスト ベンチ データの読み取り/書き込みを行います] が有効であるか確認します。ファイル I/O ではなく定数を使用するテスト ベンチを生成するには、[ファイル I/O を使用してテスト ベンチ データの読み取り/書き込みを行います] をクリアします。

[適用] をクリックし、[テスト ベンチを生成] をクリックします。

HDL テスト ベンチ生成方法の詳細については、テスト ベンチ生成を参照してください。

コシミュレーションによる生成されたコードの検証

生成されたコードを検証するコシミュレーション モデルを生成するには、次の手順に従います。

[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [テスト ベンチ] ペインの [使用するコシミュレーション モデル] で、コシミュレーション ツールを選択します。

[適用] をクリックし、[テスト ベンチを生成] をクリックします。

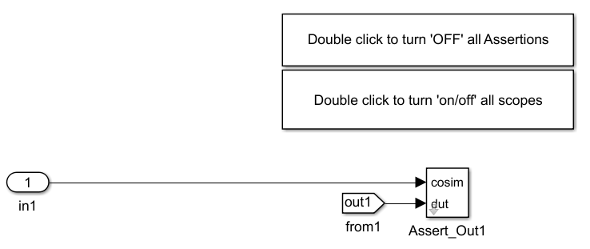

テスト ベンチの生成後、コシミュレーション モデルを保存します。モデルで、

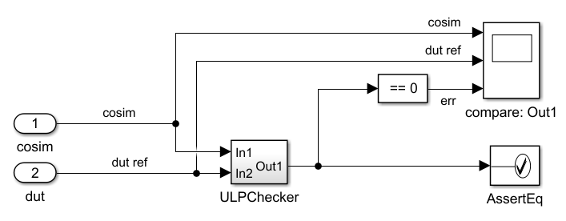

Compareサブシステムをダブルクリックします。

Assert_Out1ブロックをダブルクリックすると、ブロック パラメーターに、指定した [許容誤差の値] が示されます。Assert_Out1ブロック内を確認するには、マスクをクリックします。[ulp error]に基づいて浮動小数点許容誤差チェックを指定すると、モデルにULPCheckerブロックが表示されます。

ULPCheckerには、数値の精度をチェックするときに HDL Coder で ULP 誤差をどのように考慮するかを示す MATLAB Function ブロックがあります。[relative error]に基づいて浮動小数点許容誤差チェックを指定すると、モデルにはRelErrCheckブロックが示されます。

RelerrCheckには、数値の精度をチェックするときに HDL Coder で相対誤差をどのように考慮するかを示す MATLAB Function ブロックがあります。モデルの Simulink® エディター内でシミュレーションを開始します。コシミュレーションの終わりに、

compare: Out1のスコープをチェックします。このスコープでは、コシミュレーション ブロックからの結果の信号と DUT からの基準信号の差が比較されます。

コシミュレーション モデルの生成も参照してください。

制限

生成されたコードを検証する場合、VHDL-2008 よりも前の IEEE® 標準を使用する構造はネイティブ浮動小数点でサポートされません。