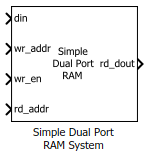

Simple Dual Port RAM System

読み取りと書き込みの同時処理をサポートするシンプル デュアルポート RAM

ライブラリ:

HDL Coder /

HDL RAMs

説明

Simple Dual Port RAM System ブロックは、読み取りデータ用の単一の出力端子を介して読み取りと書き込みの同時処理をサポートするシンプル デュアルポート RAM をモデル化します。このブロックを構成するには、ブロックを開き、[Type of RAM] を [Simple dual port] に設定します。このブロックを使用して次のことが可能です。

din 端子、addr 端子、we 端子のベクトル データを使用して並列 RAM バンクを作成する。

[Initial output of RAM] パラメーターを使用して RAM の初期値を指定する。

[Use asynchronous read feature in target hardware] パラメーターを選択して、ターゲット ハードウェアで非同期読み取りを実行する。

[Model RAM with one cycle of delay] パラメーターを選択して、サイクル アキュレートな読み取り操作を実行する。

列書き込みメソッドを使用して、アドレス指定されたメモリ位置の指定したビットへの書き込みを行う。

メモ

書き込み操作中に同時に同じアドレスで読み取り操作が発生すると、古いデータが読み取り出力端子に現れます。

制限

RAM の FPGA ビットストリームを作成する場合、RAM の内容はグローバルなリセット ロジックでリセットされません。RAM をリセットするには、リセット ロジックを実装してください。

RAM アドレスは

fixed-point (fi)またはintegerのいずれかで、符号なしの2~31ビット長でなければなりません。

端子

入力

書き込むデータ。スカラーまたはベクトルとして指定します。端子 we の書き込みイネーブル信号が true の場合、このデータを RAM のメモリ位置に書き込むことができます。この値は、整数か、double、single、または half のいずれかの型になります。この値は fi オブジェクトにすることもでき、実数または複素数のいずれかになります。

バスのサポート:

HDL コード生成用に非バーチャル バスおよびバス配列を使用できます。

データ型: single | double | half | int8 | int16 | uint8 | uint16 | Boolean | fixed point

書き込みアドレス。スカラーまたはベクトルとして指定します。このアドレスは、端子 we の信号が true の場合の RAM への書き込みに使用します。この値は fixed-point (fi) または符号なし integer のいずれかで、2 ~ 31 ビット長でなければなりません。

データ型: uint8 | uint16 | fixed point

書き込みイネーブル。スカラーまたはベクトルとして指定します。端子 we の信号が true の場合、ブロックは指定されたメモリ位置にデータを書き込みます。端子 [we] の信号が false の場合、ブロックは [rd_addr] 端子で指定されたメモリ位置から値を読み取ります。

メモ

列書き込みメソッドを使用するには、データ型が integer または fixed-point でなければなりません。

データ型: uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

読み取りアドレス。スカラーまたはベクトルとして指定します。このアドレスは、RAM からの読み取りに使用します。この値は fixed-point (fi) または符号なし integer のいずれかで、2 ~ 31 ビット長でなければなりません。

依存関係

この端子を有効にするには、[Type of RAM] パラメーターを [Simple dual port] または Dual port に設定します。

データ型: uint8 | uint16 | fixed point

出力

読み取り出力データ。スカラーまたはベクトルとして返されます。RAM は [rd_addr] 端子で指定されたメモリ位置から古い出力データを読み取ります。

パラメーター

Main

RAM のタイプ。次のいずれかとして指定します。

Single port— Single Port RAM を作成します。入力は書き込みデータ、アドレス、および書き込みイネーブルのデータ、出力は読み取りデータです。Simple dual port— Simple Dual Port RAM を作成します。入力は書き込みデータ、書き込みアドレス、書き込みイネーブル、および読み取りアドレス、出力は読み取りアドレスからのデータです。Dual port— Dual Port RAM を作成します。入力は書き込みデータ、書き込みアドレス、書き込みイネーブル、および読み取りアドレス、出力は読み取りアドレスと書き込みアドレスからのデータです。True dual port— True Dual Port RAM を作成します。入力は書き込みデータaとb、aとbの書き込みアドレスと読み取りアドレス、および書き込みイネーブルaとb、出力は書き込みアドレスaとbからのデータです。Simple tri port— Simple Tri Port RAM を作成します。入力は書き込みデータ、書き込みアドレス、書き込みイネーブル、および読み取りアドレスaとb、出力は読み取りアドレスaとbからのデータです。

指定した RAM タイプに基づいて、ブロックの入力端子と出力端子がコード ジェネレーターによって動的に構成されます。

プログラムでの使用

ブロック パラメーター: RAMType |

| 型: 文字ベクトル、string |

値: Dual port | Simple dual port | Single port | True dual port | Simple tri port |

既定の設定: Simple dual port |

このオプションを有効にすると、ハードウェアで 1 サイクル待機せずに即時に読み取り命令を実行できます。

プログラムでの使用

ブロック パラメーター: AsyncRead |

| 型: 文字ベクトル、string |

値: 'on' | 'off' |

既定の設定: 'off' |

次のいずれかのオプションを使用して RAM の最初のシミュレーション出力を指定します。

スカラー値。

初期値と RAM ワードが 1 対 1 でマッピングされたベクトル。

RAM バンクにおける初期値と RAM ワードが 1 対 1 でマッピングされた n 行 m 列の行列。ここで、n は RAM バンクの数を表し、m は RAM ブロック内のアドレス位置の数を表します (またはその逆になります)。

プログラムでの使用

ブロック パラメーター: RAMInitialValue |

| 型: 整数、浮動小数点 |

値: 0.0 | Scalar | Vector |

既定の設定: 0.0 |

データ型: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64

詳細設定

R2024b 以降

このパラメーターをオンにすると、出力の読み取り前に RAM で入力データが 1 サイクル遅延します。生成された HDL コードとこのブロックを確実にサイクル アキュレートにするには、このオプションを使用します。

このパラメーターをオフにすると、RAM の入力データの読み取りと出力はすぐに行われますが、HDL コード生成時に 1 サイクルのレイテンシが追加されます。オーバーサンプリング値を指定する場合やマルチレート モデルを処理する場合にクロックレート パイプラインを利用するには、このオプションを使用します。

依存関係

このパラメーターを有効にするには、[Use asynchronous read feature in target hardware] パラメーターをオフにします。

プログラムでの使用

ブロック パラメーター: ModelRAMDelay |

| 型: 文字ベクトル、string |

値: 'on' | 'off' |

既定の設定: 'on' |

R2025a 以降

このパラメーターを

serialに設定すると、コード ジェネレーターは RAM System ブロックへのベクトル入力から RAM の並列バンクを推定します。このパラメーターを

parallelに設定すると、次のようになります。HDL コードを生成するときに、コード ジェネレーターは RAM の消費量をベクトル入力のサイズに応じてスケールアップしません。代わりに、入力信号の各演算を最初のインデックスから順番に一度に 1 つずつ適用します。順次アクセスを有効にすると、ベクトル入力を使用してデータ レートでモデル化しながら、より高速なクロック レートでマルチサイクルの RAM アクセスを利用できます。

RAM System ブロックがクロックレート パイプライン領域に存在する場合、ローカル マルチレート実装の代わりにクロックレートの実装がシリアル化に使用されます。

依存関係

このパラメーターを有効にするには、[Model RAM with one cycle of delay] パラメーターをオフにするか、[Use asynchronous read feature in target hardware] パラメーターを有効にします。

プログラムでの使用

ブロック パラメーター: VectorAccess |

| 型: 文字ベクトル、string |

値: 'serial' | 'parallel' |

既定の設定: 'serial' |

詳細

列書き込みメソッドを使用すると、RAM を等しいサイズの列の集合として表示できます。書き込みサイクル中に、それらの各列に個別に書き込むことができます。書き込みイネーブル入力のデータ型と値、および書き込みデータ入力のデータ型により、各列のサイズとアドレス指定されたメモリ位置でブロックが書き込みを行う列が決まります。

このコンテキストでは次のようになります。

DT は、書き込みデータ入力信号

dinのデータ型です。DW は、入力データのデータ幅です。

dinの値の語長と等しくなります。DTWE は、書き込みイネーブル信号

weのデータ型です。この信号により、アドレス指定されたメモリ位置でブロックが書き込みを行う列が決まります。ブロックはweの値のバイナリ表現における 1 の位置に基づいて列の書き込みを行います。NC は、RAM 空間を分割してデータを書き込むことができる列数です。

weの値の語長と等しくなります。WC は、各列の幅です。DW を NC で割った値と等しくなります。

次の表は、書き込みデータ入力のデータ型、書き込みイネーブル入力のデータ型、列数、および各列の幅の関係をまとめたものです。

| DT | DW | DTWE | NC | WC (ビット) |

|---|---|---|---|---|

uint16 | 16 | ufix4 | 4 | 4 |

uint32 | 32 | ufix4 | 4 | 8 |

uint64 | 64 | ufix4 | 4 | 16 |

uint32 | 32 | uint8 | 8 | 4 |

uint64 | 64 | uint8 | 8 | 8 |

int32 | 32 | uint16 | 16 | 2 |

たとえば、DT が uint16 で WE が ufix4 の場合、DW は 16、NC は 4、WC は 4 ビットになります。din への入力が 980 の場合、バイナリ表現は 0000001111010100 です。din の列方向の表現は、c4 = 0000、c3 = 0011、c2 = 1101、c1 = 0100 です。ここで、c1 が最初の列です。

次の表は、さまざまな入力の組み合わせに対して列書き込みメソッドを使用した場合の結果をまとめたものです。

we の値 | we のバイナリ表現 | RAM への書き込みで選択される列 | メモリ位置のデータ | dout | |

|---|---|---|---|---|---|

| 書き込み操作の実行前 | 書き込み操作の実行後 | ||||

| 3 | 0011 | c2、c1 | c4 = c3 = c2 = c1 = | c4 = c3 = c2 = c1 = | 212 |

| 4 | 0100 | c3 | c4 = c3 = c2 = c1 = | c4 = c3 = c2 = c1 = | 768 |

| 6 | 0110 | c3、c2 | c4 = c3 = c2 = c1 = | c4 = c3 = c2 = c1 = | 976 |

| 9 | 1001 | c4、c1 | c4 = c3 = c2 = c1 = | c4 = c3 = c2 = c1 = | 4 |

| 9 | 1001 | c4、c1 | c4 = c3 = c2 = c1 = | c4 = c3 = c2 = c1 = | 4084 |

書き込みイネーブル入力端子では、符号付きデータ型の入力および小数部の長さがゼロでない入力はサポートされません。

書き込みデータ入力の語長は書き込みイネーブルの語長の倍数でなければなりません。

拡張機能

C/C++ コード生成

Simulink® Coder™ を使用して C および C++ コードを生成します。

HDL Coder™ には、HDL の実装および合成されたロジックに影響する追加の構成オプションがあります。

このブロックには、ブロックの実装で hdl.RAM System object™ を使用していることを示す MATLABSystem アーキテクチャがあります。

| 一般 | |

|---|---|

| ConstrainedOutputPipeline | 既存の遅延を設計内で移動することによって出力に配置するレジスタの数。分散型パイプラインではこれらのレジスタは再分散されません。既定の設定は |

| InputPipeline | 生成されたコードに挿入する入力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| OutputPipeline | 生成されたコードに挿入する出力パイプライン ステージ数。分散型パイプラインと制約付き出力パイプラインでは、これらのレジスタを移動できます。既定の設定は |

| SynthesisAttributes | モデル内のブロックとブロック出力信号の合成属性を指定します。生成された HDL コードには以下の属性が含まれます。詳細については、SynthesisAttributesを参照してください。 |

このブロックは複素信号のコード生成をサポートしています。

ブロックでは以下はサポートされません。

データ端子における入れ子にされたバス。

データ端子への非バーチャル バス入力を使用する場合における、[Initial output of RAM] での非ゼロ値。

バージョン履歴

R2017b で導入[RAMDirective] HDL ブロック プロパティは削除されました。設計内の RAM ブロックをターゲット FPGA 上の RAM ブロックにマッピングするには、代わりに [SynthesisAttributes] HDL ブロック プロパティを使用します。

[SynthesisAttributes] HDL ブロック プロパティを使用して、ブロックとその出力信号の合成属性を指定します。HDL Coder により、生成された HDL コードにこれらの属性が含められます。

データ レート フィードバック ループの内部で Simple Dual Port RAM System ブロックを使用し、クロックレート パイプライン最適化を使用できます。このモデル設計は、ビットストリームを再生成せずにプログラムや調整が可能なルックアップ テーブルを必要とするアプリケーションに役立ちます。

新しいパラメーターの [Model RAM with one cycle of delay] は、シミュレーションにおける遅延をモデル化するために使用します。[Model RAM with one cycle of delay] は既定では有効になっていて、[Use asynchronous read feature in target hardware] を有効にすると無効になります。

次のパラメーターの名前が変更されています。

| 以前の名前 | 現在の名前 |

|---|---|

| Specify the type of RAM | Type of RAM |

| Enable asynchronous reads | Use asynchronous read feature in target hardware |

| Specify the RAM initial value | Initial output of RAM |

このブロックでは、列書き込みメソッドを使用して、指定したメモリ アドレスにある残りの部分は変えずにメモリの特定の部分を選択的に変更できます。

このブロックでは、固有の初期値で RAM バンクを初期化できます。

このブロックでは、バス配列として指定された入力データの HDL コード生成がサポートされるようになりました。

このブロックで、Half 型または Boolean 型の入力データによる HDL コード生成がサポートされるようになりました。

参考

オブジェクト

ブロック

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)