hdl.RAM System object からの HDL コード生成

この例では、MATLAB で hdl.RAM System object™ からの MATLAB® コードから HDL コードを生成し、生成されたハードウェアで RAM を推定する方法を示します。

MATLAB 設計

この例では、リング構造のメモリを使用するライン遅延の実装を示します。この構造では、書き込まれたデータが特定のサイクル数後に読み取られるように、データをある位置に書き込み、別の位置から読み取ります。Virtex FPGA でのこのアーキテクチャの効率的な実装では、オンチップのデュアル ポート ブロック RAM およびアドレス カウンターを使用します。ブロック RAM は、512x8 または 256x9 の同期デュアル ポート RAM として構成できます。遅延の長さをパラメーター化するために、RAM 書き込みアドレスはカウンターによって生成され、読み取りアドレスは書き込みアドレスに定数 K を加算して生成されます。メモリ サイズが M の場合、入力は、メモリに書き込まれてから M-K クロック サイクル後に読み取られます。そのため、M-K 単語シフト動作を実装します。

design_name = 'mlhdlc_hdlram'; testbench_name = 'mlhdlc_hdlram_tb';

MATLAB 設計を確認します。

type(design_name);

%#codegen

function data_out = mlhdlc_hdlram(data_in)

%

% This example shows implementation of a line delay that uses a memory in a

% ring structure, where data is written in one position and read from

% another position in such a way that the data written will be read after a

% specific number of cycles. An efficient implementation of this

% architecture on Virtex FPGAs uses the on-chip Dual Port Block RAMs and an

% address counter. The Block RAMs can be configured as 512x8 or 256x9

% synchronous Dual Port RAMs. To parameterize the delay length, the RAM

% write address is generated by a counter and the read address is generated

% by adding a constant K to the write address. If the memory size is M, the

% input will be read M-K clock cycles after it was written to the memory,

% hence implementing M-K word shift behaviour.

% Copyright 2012-2015 The MathWorks, Inc.

persistent hRam;

if isempty(hRam)

hRam = hdl.RAM('RAMType', 'Dual port');

end

% read address counter

persistent rdAddrCtr;

if isempty(rdAddrCtr)

rdAddrCtr = 0;

end

% ring counter length

ringCtrLength = 10;

ramWriteAddr = rdAddrCtr + ringCtrLength;

ramWriteData = data_in;

ramWriteEnable = true;

ramReadAddr = rdAddrCtr;

% execute single step of RAM

[~, ramRdDout] = step(hRam, ramWriteData, ramWriteAddr, ramWriteEnable, ramReadAddr);

rdAddrCtr = rdAddrCtr + 1;

data_out = ramRdDout;

type(testbench_name);

function mlhdlc_hdlram_tb

%

% Copyright 2012-2015 The MathWorks, Inc.

clear test_hdlram;

data = 100:200;

ring_out = zeros(1, length(data));

for ii=1:100

ring_in = data(ii);

ring_out(ii) = mlhdlc_hdlram(ring_in);

end

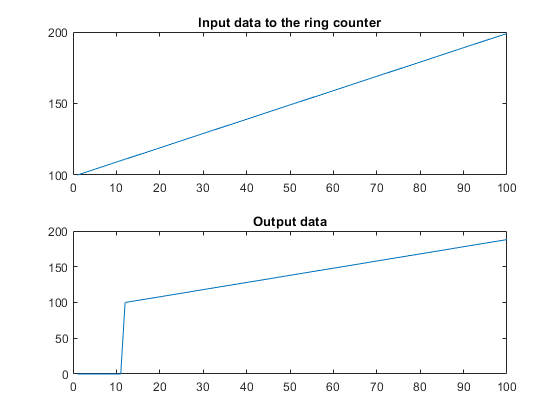

figure('Name', [mfilename, '_plot']);

subplot(2,1,1);

plot(1:100,data(1:100));

title('Input data to the ring counter')

subplot(2,1,2);

plot(1:100,ring_out(1:100));

title('Output data')

end

設計のシミュレーション

コードの生成前にテスト ベンチを使用して設計をシミュレートし、実行時エラーがないことを確認します。

mlhdlc_hdlram_tb

HDL Coder™ プロジェクトの新規作成

新しいプロジェクトを作成するには、次のコマンドを入力します。

coder -hdlcoder -new mlhdlc_sysobj_prj

次に、mlhdlc_hdlram.m ファイルを MATLAB 関数としてプロジェクトに追加し、mlhdlc_hdlram_tb.m を MATLAB テスト ベンチとして追加します。

MATLAB HDL Coder プロジェクトの作成と入力に関する詳細なチュートリアルについては、Generate HDL Code from MATLAB Algorithmsを参照してください。

固定小数点変換と HDL コード生成の実行

ワークフロー アドバイザーを起動します。ワークフロー アドバイザーで、[コード生成] の手順を右クリックします。[選択したタスクまで実行] オプションを選択して、最初から HDL コード生成までのすべての手順を実行します。

ログ ウィンドウにあるリンクをクリックして、生成された HDL コードを確認します。

サポートされている System object

HDL コード生成でサポートされている System object のリストについては、HDL コード生成に使用できる事前定義済みの System Objectsを参照してください。