Simulink の RAM および ROM 入門

この例では、HDL Coder™ を使用して FPGA 設計で RAM リソースを利用する方法を示します。

はじめに

FPGA の専用 RAM ブロックは、デジタル設計においては貴重なリソースです。Simulink® では RAM と ROM を使用した設計が容易であり、HDL Coder を使用して FPGA で利用可能な専用 RAM ブロックを簡単に利用できます。

HDL サンプル ライブラリの RAM ブロック

HDL Coder の HDL RAMs ブロック ライブラリには、次の種類の RAM ブロックが備わっています。hdllib を使用して HDL Coder™ と互換性のあるブロックを表示してから、HDL Coder から HDL RAMs ライブラリを選択します。

Single Port RAM

Single Port RAM System

Simple Dual Port RAM

Simple Dual Port RAM System

Dual Port RAM

Dual Port RAM System

Dual Rate Dual Port RAM

HDL ライブラリの RAM ブロックに移動するには、次のコマンドを実行します。

hdllib

RAM ブロックは、動作のシミュレーションのために Simulink ブロックを使用して作成されたマスク サブシステムです。コード生成では、HDL Coder は HDL 内の RAM 構造を記述する、事前定義されたテンプレートを生成します。大部分の合成ツールは、テンプレートの RAM 構造を認識し、それらを FPGA 上の使用可能な RAM リソースにマッピングします。

RAM ブロックの一般的な RAM コーディング スタイルの使用

既定では、HDL Coder は RAM 構造にクロック イネーブルを使用する RAM テンプレートを提供しています。あるいは、HDL Coder はクロック イネーブルを使用しない汎用テンプレートのスタイルも提供しています。汎用 RAM スタイル テンプレートは、RAM のラッパーにロジックをもつクロック イネーブルを実装します。これを制御するには、HDL Coder の [グローバル設定] パネルにある [RAM アーキテクチャ] オプションを使用できます。

合成ツールがクロック イネーブルを含む RAM 構造をサポートしていない場合、汎用 RAM スタイルを使用する場合があり、結果として FPGA RAM リソースに HDL をマッピングできません。

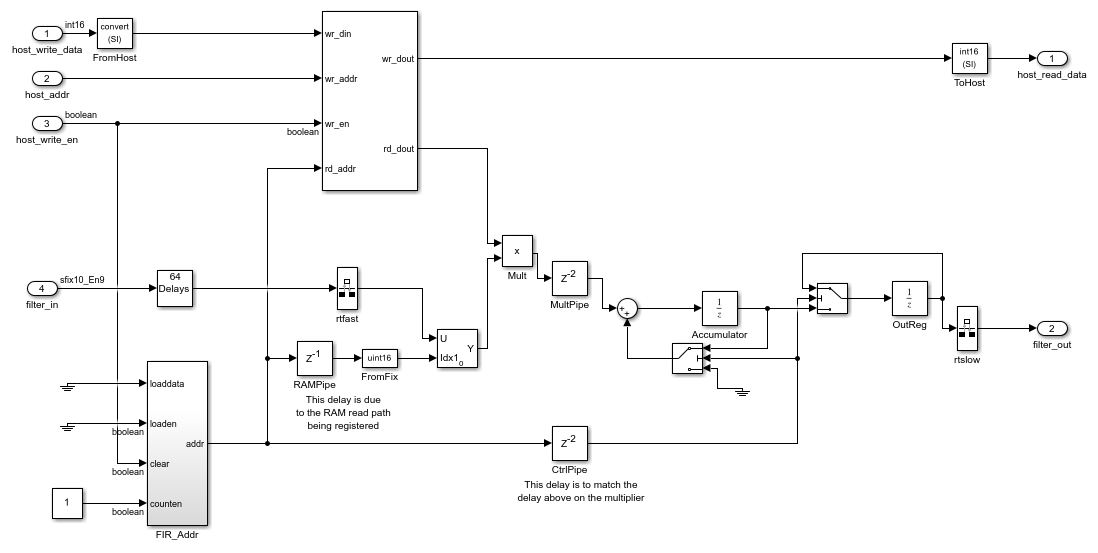

hdlcoderfirram の例で、設計で汎用 RAM スタイルを使用する方法を示します。

open_system('hdlcoderfirram'); open_system('hdlcoderfirram/FIR_RAM');

RAM コーディング スタイルの選択

[コンフィギュレーション パラメーター] ウィンドウから RAM コーディング スタイルを選択できます。Simulink ツールストリップの [アプリ] タブで、[HDL Coder] を選択します。[HDL コード] タブで、[設定] を選択します。[HDL コード生成]、[グローバル設定]、[コーディング スタイル] で、RAM アーキテクチャパラメーターを目的の RAM コーディング スタイルに設定します。

[RAM アーキテクチャ] パラメーターは、サブシステム内の RAM のクロック イネーブル ロジックの生成を制御し、HDL Coder が RAM の HDL コードを生成するときにクロック イネーブル信号を実装する方法を決定します。

既定では、[RAM アーキテクチャ] は RAM with clock enable に設定されています。HDL Coder は、専用のクロック イネーブル信号を使用する RAM 用の HDL コードを生成します。専用クロック イネーブル信号が利用できるかどうかは、FPGA ハードウェアの仕様によって異なります。

[RAM アーキテクチャ] を Generic RAM without clock enable に設定すると、HDL Coder はクロック イネーブル信号をサポートしない RAM 用の HDL コードを生成します。代わりに、HDL Coder はクロック イネーブル ロジックを実装する RAM ラッパーを生成します。クロック イネーブル信号を使用する RAM をサポートしていない合成ツール、または RAM 用に生成された HDL コードを FPGA RAM リソースに適切にマップしないターゲット ハードウェアを使用する場合は、この設定を使用します。

Simulink ブロックを使用した ROM の作成

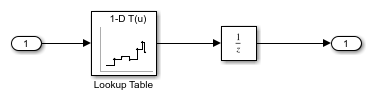

HDL Coder は ROM ブロックを提供しませんが、次の例に示すように、Simulink の Lookup Table ブロックと Unit Delay ブロックを使用してブロックを作成できます。

open_system('hdlcoderrom'); open_system('hdlcoderrom/ROM');

Simulink から ROM を作成する際は次のモデリングのガイドラインに準拠してください。

n ビット アドレスについては、ルックアップ テーブル データの

のエントリすべてを指定します。そうでない場合、合成ツールは生成されたコードの RAM へのマッピングを行わない可能性があり、コードは Simulink モデルと一致しない可能性があります。

のエントリすべてを指定します。そうでない場合、合成ツールは生成されたコードの RAM へのマッピングを行わない可能性があり、コードは Simulink モデルと一致しない可能性があります。Lookup Table ブロックと Unit Delay ブロックは、同じモデルの階層構造に配置します。

RAM リセット ロジックのサポートは FPGA デバイスと合成ツールによって異なります。最良な合成結果を得るには、[HDL ブロック プロパティ] ダイアログ ボックスで "ResetType" プロパティを

noneに設定して、Unit Delay ブロックでのリセット ロジックの生成を抑制します。さらに、[HDL テスト ベンチ] コンフィギュレーション パラメーターの "IgnoreDataChecking" プロパティを 1 に設定して、リセット ロジックの抑制によって生じる最初のシミュレーションの不一致を無視します。

これらのガイドラインに従う場合、大部分の合成ツールは、FPGA の専用 RAM ブロックを使用して ROM を実装します。

RAM の最小サイズ要件

設計内の RAM または ROM のサイズが小さい場合、合成ツールは最良な速度パフォーマンスを得るために、生成されたコードを専用 RAM リソースではなくレジスタにマッピングする場合があります。合成ツールの RAM の最小サイズ要件と、必要に応じて、その要件をオーバーライドする方法を確認してください。