importhdl

Verilog または VHDL コードをインポートして Simulink モデルを生成

説明

importhdl( は、1 つ以上の名前と値のペアの引数で指定されたオプションを使用して、指定された HDL ファイルをインポートし、出力に直接影響しない未接続のコンポーネントは削除して対応する Simulink モデルを生成します。FileNames,Name=Value)

例

この例では、Verilog コードを含む 1 つのファイルをインポートして対応する Simulink™ モデルを生成する方法を示します。この例の Verilog コードは、モデル内のシンプルな Compare to Constant ブロックを推定します。

入力 Verilog ファイルの指定

入力 HDL ファイルが構文エラーを含んでおらず、合成可能であり、HDL インポートでサポートされている構造を使用していることを確認します。この例は、比較を実行する Verilog コードを示しています。

edit('comparator.v')

// File Name: comparator.v

// This module implements a simple comparator module

`define value 12

module comparator (clk, rst, a, b);

input clk, rst;

input [3:0] a;

output reg [3:0] b;

always@(posedge clk) begin

if (rst)

b <= 0;

else if (a < `value)

b <= a + 1;

end

endmodule

Verilog ファイルのインポート

HDL ファイルをインポートして Simulink™ モデルを生成するには、ファイル名を文字ベクトルとして関数 importhdl に渡します。

importhdl('comparator.v');

### Parsing <a href="matlab:edit('comparator.v')">comparator.v</a>.

### Top Module name: 'comparator'.

### Identified ClkName::clk.

### Identified RstName::rst.

### Hdl Import parsing done.

### Removing unconnected components.

### Creating Target model comparator

### Begin model generation 'comparator'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Start Layout...

### Working on hierarchy at ---> 'comparator'.

### Laying out components.

### Working on hierarchy at ---> 'comparator/comparator'.

### Laying out components.

### Drawing block edges...

### Drawing block edges...

### Model generation complete.

### Setting model parameters.

### Generated model file C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Bdoc.May28\hdlcoder-ex77699673\hdlimport\comparator\comparator.slx.

### Importhdl completed.

HDL インポートは、入力ファイルを解析し、MATLAB™ コマンド ウィンドウにインポート処理のメッセージを表示します。インポートすると、生成された Simulink™ モデル comparator.slx へのリンクが示されます。生成されたモデルには、入力 Verilog ファイルの名前と同じ名前が使用されます。

生成された Simulink™ モデルの確認

生成された Simulink™ モデルを開くには、リンクを選択します。このモデルは、現在のフォルダーに対して相対的なパス hdlimport/comparator に保存されます。モデルをシミュレートしてシミュレーション結果を確認できます。

addpath('hdlimport/comparator'); open_system('comparator.slx'); sim('comparator.slx');

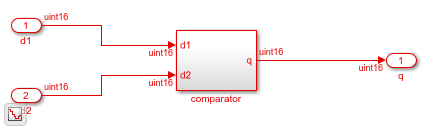

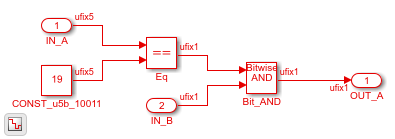

最上位の DUT サブシステムの名前が入力ファイル内の最上位モジュールと同じ名前になっています。インポート時に入力 Verilog コードから Compare to Constant ブロックが推定されたことがわかります。

open_system('comparator/comparator')

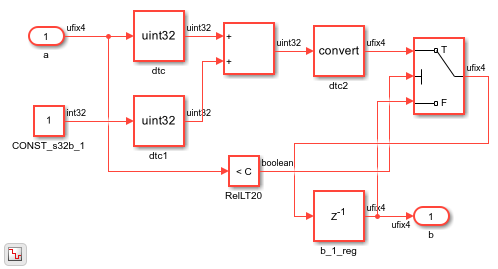

この例では、VHDL ファイルをインポートして、対応する Simulink モデルを生成する方法を示します。この例の VHDL コードはシンプルな 4 ビット カウンターです。

入力 VHDL ファイルの指定

入力 HDL ファイルが構文エラーを含んでおらず、合成可能であり、importhdl 関数でサポートされている構造を使用していることを確認します。この例の VHDL コードは 4 ビット カウンターを実行します。

edit('counter.vhd')

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity Counter is

Port (

clk : in STD_LOGIC;

rst : in STD_LOGIC;

count : out STD_LOGIC_VECTOR(3 downto 0)

);

end Counter;

architecture Behavioral of Counter is

signal temp_count : STD_LOGIC_VECTOR(3 downto 0) := "0000";

begin

process(clk, rst)

begin

if rst = '1' then

temp_count <= "0000";

elsif rising_edge(clk) then

if temp_count = "1111" then

temp_count <= "0000";

else

temp_count <= temp_count + 1;

end if;

end if;

end process;

count <= temp_count;

end Behavioral;

VHDL ファイルのインポート

HDL ファイルをインポートして Simulink™ モデルを生成するには、ファイル名を文字ベクトルとして関数 importhdl に渡します。

importhdl('counter.vhd');

### Parsing <a href="matlab:edit('counter.vhd')">counter.vhd</a>.

### Top Module name: 'counter'.

### Identified ClkName::clk.

### Identified RstName::rst.

### Hdl Import parsing done.

### Removing unconnected components.

### Creating Target model counter

### Begin model generation 'counter'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Start Layout...

### Working on hierarchy at ---> 'counter'.

### Laying out components.

### Working on hierarchy at ---> 'counter/counter'.

### Laying out components.

### Drawing block edges...

### Drawing block edges...

### Model generation complete.

### Setting model parameters.

### Generated model file C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Bdoc.Jul3\hdlcoder-ex36839477\hdlimport\counter\counter.slx.

### Importhdl completed.

importhdl 関数は、入力ファイルを解析し、MATLAB コマンド ウィンドウにインポート処理に関するメッセージを表示します。インポートすると、生成された Simulink モデル counter.slx にリンクされます。生成されたモデルには、入力 VHDL ファイルと同じ名前が使用されます。

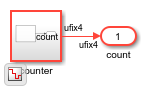

生成された Simulink™ モデルを開く

生成された Simulink™ モデルを開くには、リンクをクリックします。関数は、現在のフォルダーに対して相対的なパス hdlimport/counter にモデルを保存します。モデルをシミュレートしてシミュレーション結果を確認できます。

addpath('hdlimport/counter'); open_system('counter.slx'); sim('counter.slx');

最上位の DUT サブシステムの名前が入力ファイル内の最上位モジュールと同じ名前になっています。VHDL コードを表すために importhdl 関数で Counter ブロックが選択されています。

open_system('counter/counter')

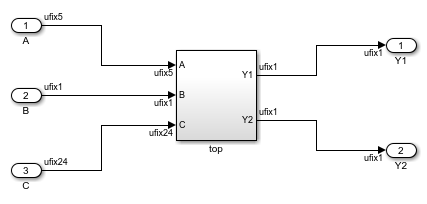

この例では、Verilog コードを含む複数のファイルをインポートして対応する Simulink™ モデルを生成する方法を示します。

入力 Verilog ファイルの指定

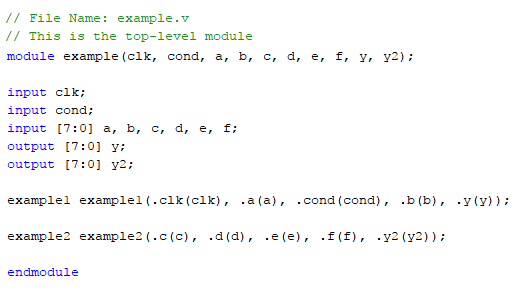

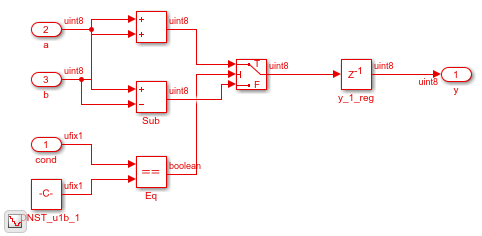

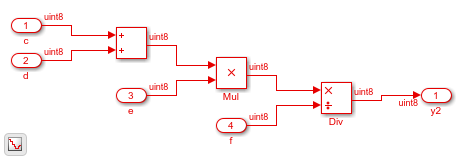

入力 HDL ファイルが構文エラーを含んでおらず、合成可能であり、HDL インポートでサポートされている構造を使用していることを確認します。たとえば、次のコードは、モジュールのインスタンス化を使用して階層設計を形成する 3 つの Verilog ファイルを示しています。モジュール example1.v は、if-else 条件に基づく単純な順序回路を実装します。もう一方のモジュール example2.v は、単純な組み合わせ演算式を実装します。

edit('example1.v') edit('example2.v')

ファイル example.v に含まれる最上位モジュールは、example1.v および example2.v 内の 2 つのモジュールをインスタンス化します。

edit('example.v')

Verilog ファイルのインポート

HDL ファイルをインポートして Simulink™ モデルを生成するには、ファイル名を文字ベクトルの cell 配列として関数 importhdl に渡します。既定では、HDL インポートは入力ファイルを解析する際、最上位モジュールとクロック バンドルを識別します。

importhdl({'example.v','example1.v','example2.v'})

### Parsing <a href="matlab:edit('example.v')">example.v</a>.

### Parsing <a href="matlab:edit('example1.v')">example1.v</a>.

### Parsing <a href="matlab:edit('example2.v')">example2.v</a>.

### Top Module of the source: 'example'.

### Identified ClkName::clk.

### Hdl Import parsing done.

### Creating Target model example

### Generating Dot Layout...

### Start Layout...

### Working on hierarchy at ---> 'example'.

### Laying out components.

### Working on hierarchy at ---> 'example/example'.

### Laying out components.

### Working on hierarchy at ---> 'example/example/example1'.

### Laying out components.

### Applying Dot Layout...

### Drawing block edges...

### Working on hierarchy at ---> 'example/example/example2'.

### Laying out components.

### Applying Dot Layout...

### Drawing block edges...

### Applying Dot Layout...

### Drawing block edges...

### Applying Dot Layout...

### Drawing block edges...

### Setting the model parameters.

### Generated model as C:\Temp\examples\examples\hdlcoder-ex56732899\hdlimport\example\example.slx.

### HDL Import completed.

HDL インポートは、入力ファイルを解析し、MATLAB™ コマンド ウィンドウにインポート処理のメッセージを表示します。インポートすると、生成された Simulink™ モデル example.slx へのリンクが示されます。生成されたモデルは、入力 Verilog ファイル example1.v に含まれる最上位モジュールと同じ名前を使用します。

生成された Simulink™ モデルの確認

生成された Simulink™ モデルを開くには、リンクを選択します。このモデルは、現在のフォルダーに対して相対的なパス hdlimport/example に保存されます。モデルをシミュレートしてシミュレーション結果を確認できます。

addpath('hdlimport/example') open_system('example.slx')

ゼロ除算を避けるため、シミュレーション前に警告診断を非表示にすることができます。

Simulink.suppressDiagnostic({'example/example/example2/Div'}, ...

'SimulinkFixedPoint:util:fxpDivisionByZero')

sim('example')

モジュールのインスタンス化を使用する Verilog コードを実装するサブシステムの階層を表示できます。

open_system('example/example/example1')

open_system('example/example/example2')

この例では、Verilog コードを含む複数のファイルをインポートして対応する Simulink™ モデルを生成する方法を示します。複数のファイルをインポートする際、HDL コードを難読化する必要がある場合やファイルにベンダー固有 IP の HDL コードが含まれている場合、関数 importhdl を使用して HDL コードを BlackBox モジュールとしてインポートできます。

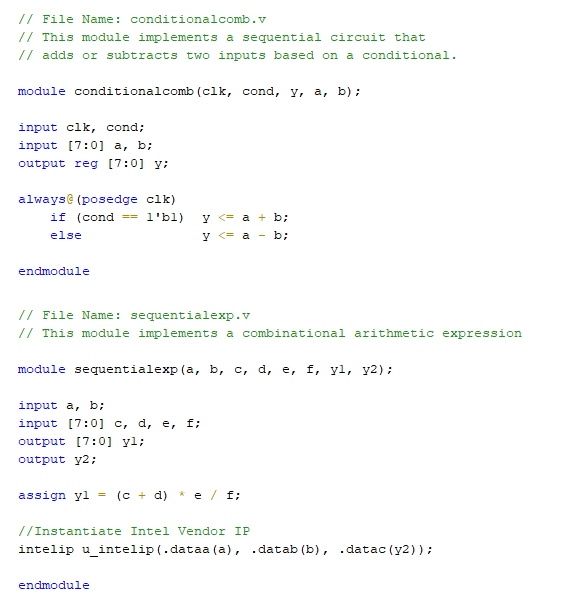

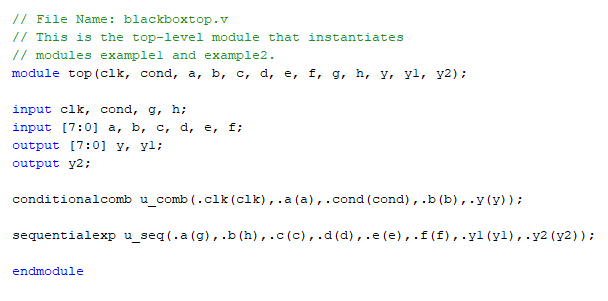

入力 Verilog ファイルの指定

入力 HDL ファイルが構文エラーを含んでおらず、合成可能であり、HDL インポートでサポートされている構造を使用していることを確認します。たとえば、次のコードは、モジュールのインスタンス化を使用して階層設計を形成する 3 つの Verilog ファイルを示しています。モジュール sequentialexp.v は、if-else 条件に基づく単純な順序回路を実装します。もう一方のモジュール comditionalcomb.v は、単純な組み合わせ演算式を実装します。

edit('conditionalcomb.v') edit('sequentialexp.v') edit('intelip.v')

sequentialexp.v モジュールが、単精度浮動小数点加算器を実装する Intel® IP をインスタンス化することを確認します。

ファイル blackboxtop.v に含まれる最上位モジュール top は、conditionalcomb.v および sequentialexp.v 内の 2 つのモジュールをインスタンス化します。

edit('blackboxtop.v')

Verilog ファイルのインポート

HDL ファイルをインポートして Simulink™ モデルを生成するには、ファイル名を文字ベクトルの cell 配列として関数 importhdl に渡します。既定では、HDL インポートは入力ファイルを解析する際、最上位モジュールとクロック バンドルを識別します。

importhdl({'blackboxtop.v','conditionalcomb.v','sequentialexp.v','intelip.v'}, ...

'topModule','top','blackBoxModule','intelip')

### Parsing <a href="matlab:edit('blackboxtop.v')">blackboxtop.v</a>.

### Parsing <a href="matlab:edit('conditionalcomb.v')">conditionalcomb.v</a>.

### Parsing <a href="matlab:edit('sequentialexp.v')">sequentialexp.v</a>.

### Parsing <a href="matlab:edit('intelip.v')">intelip.v</a>.

### Top Module of the source: 'top'.

### Identified ClkName::clk.

### Hdl Import parsing done.

### Creating Target model top

### Generating Dot Layout...

### Start Layout...

### Working on hierarchy at ---> 'top'.

### Laying out components.

### Working on hierarchy at ---> 'top/top'.

### Laying out components.

### Working on hierarchy at ---> 'top/top/u_comb'.

### Laying out components.

### Applying Dot Layout...

### Drawing block edges...

### Working on hierarchy at ---> 'top/top/u_seq'.

### Laying out components.

### Working on hierarchy at ---> 'top/top/u_seq/u_intelip'.

### Laying out components.

### Applying Dot Layout...

### Drawing block edges...

### Applying Dot Layout...

### Drawing block edges...

### Applying Dot Layout...

### Drawing block edges...

### Applying Dot Layout...

### Drawing block edges...

### Setting the model parameters.

### Generated model as C:\Temp\examples\examples\hdlcoder-ex63017378\hdlimport\top\top.slx.

### HDL Import completed.

HDL インポートは、入力ファイルを解析し、MATLAB™ コマンド ウィンドウにインポート処理のメッセージを表示します。インポートすると、生成された Simulink™ モデル top.slx へのリンクが示されます。生成されたモデルは、入力 Verilog ファイル conditionalcomb.v に含まれる最上位モジュールと同じ名前を使用します。

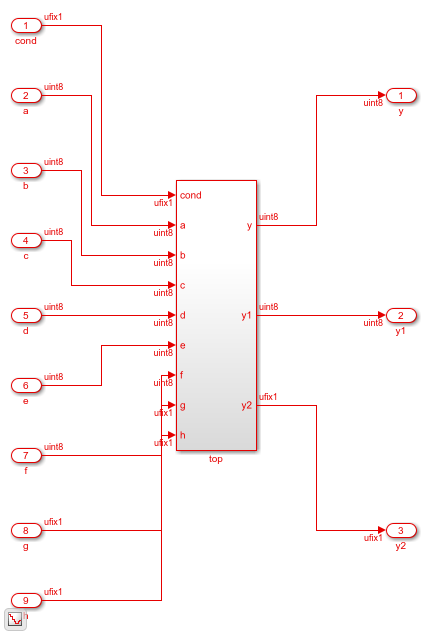

生成された Simulink™ モデルの確認

生成された Simulink™ モデルを開くには、リンクを選択します。このモデルは、現在のフォルダーに対して相対的なパス hdlimport/top に保存されます。モデルをシミュレートしてシミュレーション結果を確認できます。

addpath('hdlimport/top') open_system('top.slx') set_param('top','SimulationCommand','update')

ゼロ除算を避けるため、シミュレーション前に警告診断を非表示にすることができます。

Simulink.suppressDiagnostic({'top/top/u_seq/Div'}, ...

'SimulinkFixedPoint:util:fxpDivisionByZero')

sim('top')

モジュールのインスタンス化を使用する Verilog コードを実装するサブシステムの階層を表示できます。

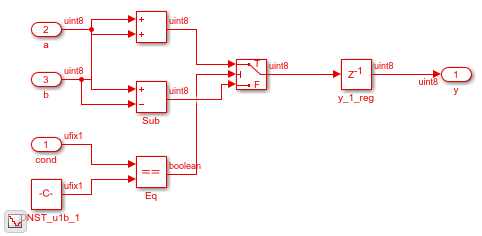

open_system('top/top/u_comb')

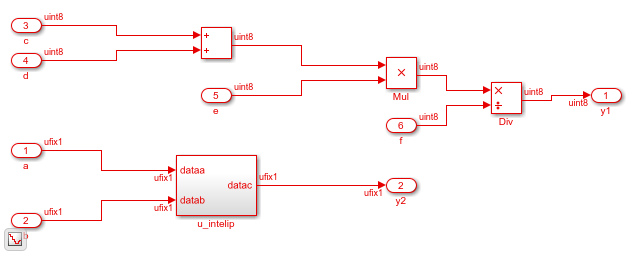

順序回路を実装するサブシステムを開くと、u_intelip サブシステムを開いて BlackBox 実装を表示できます。

open_system('top/top/u_seq')

open_system('top/top/u_seq/u_intelip')

この例では、さまざまな算術演算子と論理演算子を含む VHDL コードをインポートして、対応する Simulink モデルを生成する方法を示します。

入力 VHDL ファイルの指定

入力 VHDL ファイルが構文エラーを含んでおらず、合成可能であり、さまざまな演算子の構造を使用していることを確認します。

edit('operator.vhd')

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity Operator is

Port ( A : in STD_LOGIC_VECTOR(3 downto 0);

B : in STD_LOGIC_VECTOR(3 downto 0);

OpSelect : in STD_LOGIC_VECTOR(2 downto 0);

Result : out STD_LOGIC_VECTOR(3 downto 0));

end Operator;

architecture Behavioral of Operator is

begin

process(A, B, OpSelect)

begin

case OpSelect is

when "000" => -- Addition

Result <= A + B;

when "001" => -- Subtraction

Result <= A - B;

when "010" => -- Bitwise AND

Result <= A and B;

when "011" => -- Bitwise OR

Result <= A or B;

when "100" => -- Bitwise XOR

Result <= A xor B;

when others => -- Default case

Result <= not (A + B);

end case;

end process;

end Behavioral;

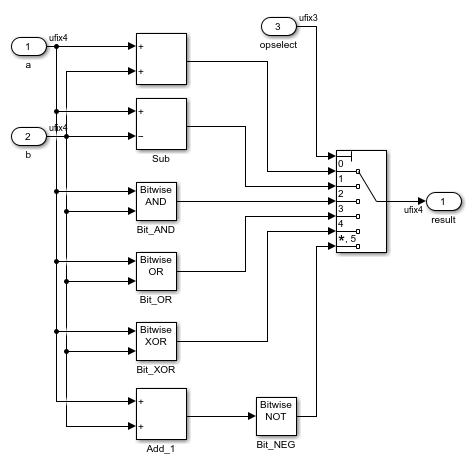

この VHDL コードには、次のような各種の演算子があります。

加算

減算

ビット単位 AND

ビット単位 OR

ビット単位 XOR

ビット単位 NOT

出力信号の制御に case ステートメントが使用されています。

VHDL ファイルのインポート

HDL ファイルをインポートして Simulink™ モデルを生成するには、ファイル名を文字ベクトルとして関数 importhdl に渡します。

importhdl('operator.vhd')

### Parsing <a href="matlab:edit('operator.vhd')">operator.vhd</a>.

### Top Module name: 'operator'.

### Hdl Import parsing done.

### Removing unconnected components.

### Creating Target model operator

### Begin model generation 'operator'...

### Rendering DUT with optimization related changes (IO, Area, Pipelining)...

### Start Layout...

### Working on hierarchy at ---> 'operator'.

### Laying out components.

### Working on hierarchy at ---> 'operator/operator'.

### Laying out components.

### Drawing block edges...

### Drawing block edges...

### Model generation complete.

### Generated model file C:\Users\user\OneDrive - MathWorks\Documents\MATLAB\ExampleManager\user.Bdoc.Jul3\hdlcoder-ex18098826\hdlimport\operator\operator.slx.

### Importhdl completed.

importhdl 関数は、入力ファイルを解析し、MATLAB コマンド ウィンドウにインポート処理に関するメッセージを表示します。インポートすると、生成された Simulink モデル operator.slx へのリンクが示されます。生成されたモデルには、入力 VHDL ファイル内の最上位モジュールと同じ名前が使用されます。

生成された Simulink™ モデルを開く

生成された Simulink™ モデルを開くには、リンクを選択します。関数は、現在のフォルダーに対して相対的なパス hdlimport/operator にモデルを保存します。モデルをシミュレートしてシミュレーション結果を確認できます。

addpath('hdlimport/operator') open_system('operator.slx')

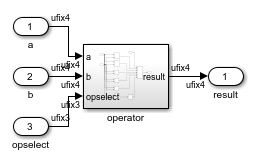

VHDL コードの機能を表すために、さまざまな数学演算ブロックと論理演算ブロックがインポート関数で選択され、case ステートメントのロジックには Multiport Switch ブロックが使用されています。

open_system('operator/operator')

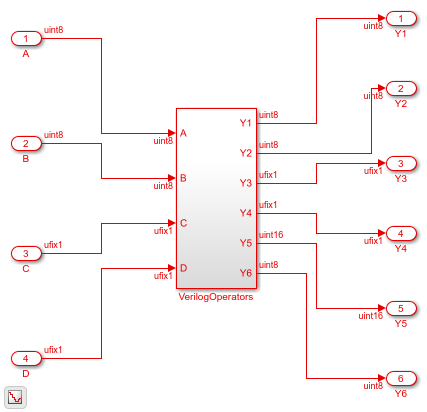

この例では、以下の演算子を含む Verilog コードをインポートして、対応する Simulink™ モデルを生成する方法を示します。

算術

論理

XOR

ビット

条件

関係

連結

入力 Verilog ファイルの指定

入力 HDL ファイルが構文エラーを含んでおらず、合成可能であり、さまざまな演算子の構造を使用していることを確認します。たとえば、次の Verilog コードはさまざまな演算子を示しています。

edit('VerilogOperators.v')

Verilog ファイルのインポート

HDL ファイルをインポートして Simulink™ モデルを生成するには、ファイル名を文字ベクトルとして関数 importhdl に渡します。

importhdl('VerilogOperators.v')

### Parsing <a href="matlab:edit('VerilogOperators.v')">VerilogOperators.v</a>.

### Top Module of the source: 'VerilogOperators'.

### Hdl Import parsing done.

### Creating Target model VerilogOperators

### Generating Dot Layout...

### Start Layout...

### Working on hierarchy at ---> 'VerilogOperators'.

### Laying out components.

### Working on hierarchy at ---> 'VerilogOperators/VerilogOperators'.

### Laying out components.

### Applying Dot Layout...

### Drawing block edges...

### Applying Dot Layout...

### Drawing block edges...

### Generated model as C:\Temp\examples\examples\hdlcoder-ex29847655\hdlimport\VerilogOperators\VerilogOperators.slx.

### HDL Import completed.

HDL インポートは、入力ファイルを解析し、MATLAB™ コマンド ウィンドウにインポート処理のメッセージを表示します。インポートすると、生成された Simulink™ モデル VerilogOperators.slx へのリンクが示されます。生成されたモデルは、入力 Verilog ファイル内の最上位モジュールと同じ名前を使用します。

生成された Simulink™ モデルの確認

生成された Simulink™ モデルを開くには、リンクを選択します。このモデルは、現在のフォルダーに対して相対的なパス hdlimport/VerilogOperators に保存されます。モデルをシミュレートしてシミュレーション結果を確認できます。

addpath('hdlimport/VerilogOperators') open_system('VerilogOperators.slx') sim('VerilogOperators.slx')

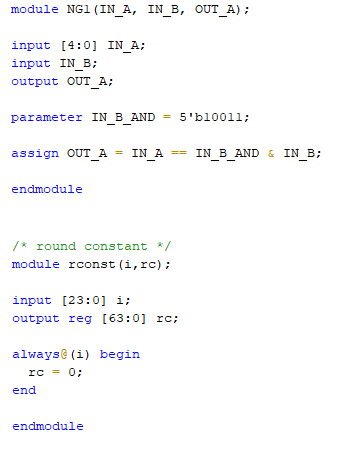

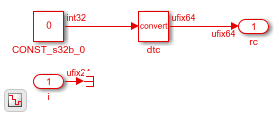

この例では、暗黙的なデータ型変換を実行する Verilog コードを含む複数のファイルをインポートして、対応する Simulink™ モデルを生成する方法を示します。HDL インポートは、算術演算、データ型の変換、ビットの選択、ビットの連結などに含まれる暗黙的なデータ型変換を実行できます。

入力 Verilog ファイルの指定

入力 HDL ファイルが構文エラーを含んでおらず、合成可能であり、HDL インポートでサポートされている構造を使用していることを確認します。たとえば、次のコードは、モジュールのインスタンス化を使用して階層設計を形成する 3 つの Verilog ファイルを示しています。モジュール NG1_implicit.v および round_const.v は、暗黙的なデータ型変換を実行します。

edit('NG1_implicit.v') edit('round_constant.v')

ファイル example.v に含まれる最上位モジュールは、NG1_implicit.v および round_constant.v 内の 2 つのモジュールをインスタンス化します。

edit('implicit_top.v')

Verilog ファイルのインポート

HDL ファイルをインポートして Simulink™ モデルを生成するには、ファイル名を文字ベクトルの cell 配列として関数 importhdl に渡します。既定では、HDL インポートは入力ファイルを解析する際、最上位モジュールを識別します。

importhdl({'implicit_top.v','NG1_implicit.v','round_constant.v'})

### Parsing <a href="matlab:edit('implicit_top.v')">implicit_top.v</a>.

### Parsing <a href="matlab:edit('NG1_implicit.v')">NG1_implicit.v</a>.

### Parsing <a href="matlab:edit('round_constant.v')">round_constant.v</a>.

### Top Module name: 'top'.

Warning: Unused input port 'i' in 'rconst' module.

### Hdl Import parsing done.

### Creating Target model top

### Generating Dot Layout...

### Start Layout...

### Working on hierarchy at ---> 'top'.

### Laying out components.

### Working on hierarchy at ---> 'top/top'.

### Laying out components.

### Working on hierarchy at ---> 'top/top/NG1'.

### Laying out components.

Configurable Subsystem block 'simulink/Ports & Subsystems/Configurable Subsystem' must be converted to a Variant Subsystem block. Variant subsystems offers enhanced capabilities while maintaining equivalant functionality. Support of Configurable Subsystem will be removed in a future release.

### Applying Dot Layout...

### Drawing block edges...

### Working on hierarchy at ---> 'top/top/rconst'.

### Laying out components.

### Applying Dot Layout...

### Drawing block edges...

### Applying Dot Layout...

### Drawing block edges...

### Applying Dot Layout...

### Drawing block edges...

### Generated model file C:\TEMP\Examples\hdlcoder-ex12503110\hdlimport\top\top.slx.

### Importhdl completed.

HDL インポートは、入力ファイルを解析し、MATLAB™ コマンド ウィンドウにインポート処理のメッセージを表示します。インポートすると、生成された Simulink™ モデル implicit_top.slx へのリンクが示されます。生成されたモデルは、入力 Verilog ファイル implicit_top.v に含まれる最上位モジュールと同じ名前を使用します。

生成された Simulink™ モデルの確認

生成された Simulink™ モデルを開くには、リンクを選択します。このモデルは、現在のフォルダーに対して相対的なパス hdlimport/example に保存されます。モデルをシミュレートしてシミュレーション結果を確認できます。

addpath('hdlimport/top'); open_system('top.slx')

rconst サブシステムで、入力端子の 1 つが未接続です。Terminator ブロックを追加して未終端の出力を避けることが推奨されます。

addterms('top'); sim('top');

モジュールのインスタンス化を使用する Verilog コードを実装するサブシステムの階層を表示できます。

open_system('top/top/NG1')

open_system('top/top/rconst')

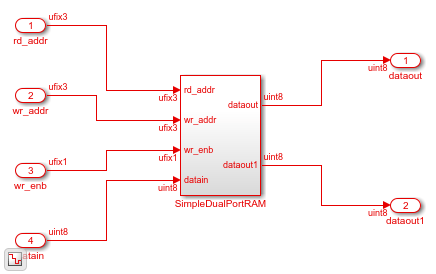

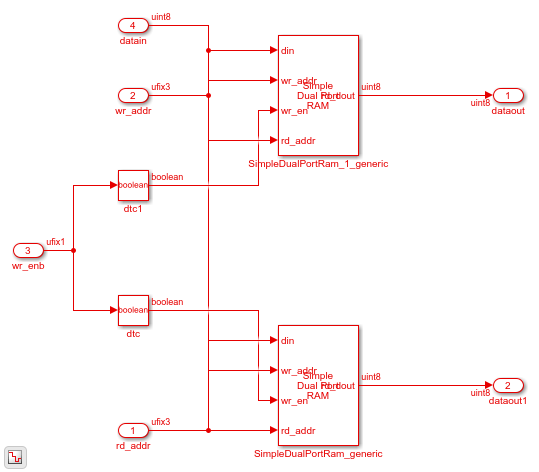

この例では、Verilog コードを含むファイルをインポートして、生成される Simulink™ モデル内の RAM ブロックを推定する方法を示します。hdl.RAM System-Object に基づくブロックやブロック RAM など、HDL RAM ライブラリに含まれるさまざまな RAM のいずれかを推定する Verilog コードをインポートできます。

入力 Verilog ファイルの指定

入力 HDL ファイルが構文エラーを含んでおらず、合成可能であり、HDL インポートでサポートされている構造を使用していることを確認します。この例は Verilog コードを示します。

edit('simple_dual_port_ram.v')

Verilog ファイルのインポート

HDL ファイルをインポートして Simulink™ モデルを生成するには、ファイル名を文字ベクトルとして関数 importhdl に渡します。

importhdl('simple_dual_port_ram.v')

### Parsing <a href="matlab:edit('simple_dual_port_ram.v')">simple_dual_port_ram.v</a>.

### Top Module name: 'SimpleDualPortRAM'.

### Identified ClkName::clk.

### Hdl Import parsing done.

### Creating Target model SimpleDualPortRAM

### Generating Dot Layout...

### Start Layout...

### Working on hierarchy at ---> 'SimpleDualPortRAM'.

### Laying out components.

### Working on hierarchy at ---> 'SimpleDualPortRAM/SimpleDualPortRAM'.

### Laying out components.

Configurable Subsystem block 'simulink/Ports & Subsystems/Configurable Subsystem' must be converted to a Variant Subsystem block. Variant subsystems offers enhanced capabilities while maintaining equivalant functionality. Support of Configurable Subsystem will be removed in a future release.

### Applying Dot Layout...

### Drawing block edges...

### Applying Dot Layout...

### Drawing block edges...

### Setting model parameters.

### Generated model file C:\TEMP\Examples\hdlcoder-ex67646187\hdlimport\SimpleDualPortRAM\SimpleDualPortRAM.slx.

### Importhdl completed.

HDL インポートは、入力ファイルを解析し、MATLAB™ コマンド ウィンドウにインポート処理のメッセージを表示します。インポートすると、生成された Simulink™ モデル SimpleDualPortRAM.slx へのリンクが示されます。生成されたモデルは、入力 Verilog ファイル内の最上位モジュールと同じ名前を使用します。

生成された Simulink™ モデルの確認

生成された Simulink™ モデルを開くには、リンクを選択します。このモデルは、現在のフォルダーに対して相対的なパス hdlimport/SimpleDualPortRAM に保存されます。モデルをシミュレートしてシミュレーション結果を確認できます。

addpath('hdlimport/SimpleDualPortRAM'); open_system('SimpleDualPortRAM.slx'); sim('SimpleDualPortRAM.slx');

モデルをナビゲートすると、Simple Dual Port RAM ブロックが表示されます。

open_system('SimpleDualPortRAM/SimpleDualPortRAM')

入力引数

Simulink モデルの生成のためにインポートする HDL ファイルの名前。既定では、importhdl は Verilog ファイルをインポートします。インポート対象に応じて次を行います。

1 つの HDL ファイルの場合、ファイル名を文字ベクトルとして指定します。

複数の HDL ファイルの場合、ファイル名を文字ベクトルの cell 配列として指定します。

1 つのフォルダー内のすべての HDL ファイルの場合、フォルダー名を文字ベクトルとして指定します。

複数のフォルダー、およびファイルとフォルダーの組み合わせの場合、文字ベクトルの cell 配列として指定します。また、再帰的フォルダーを含むサブフォルダーも使用できます。

例: importhdl('example') は、指定された HDL ファイルをインポートします。example が現在の作業フォルダーのサブフォルダーである場合、HDL インポートはサブフォルダー example とそのサブフォルダー内のモジュールのインスタンス化を解析し、すべての .v ファイルに対する Simulink モデルを生成します。importhdl が example という名前のサブフォルダーを見つけられない場合、MATLAB® パス上で example という名前の HDL ファイルを検索します。

例: importhdl({'top.v','subsystem1.v','subsystem2.v'}) は、指定された Verilog® ファイルをインポートし、対応する Simulink モデルを生成します。

例: importhdl(pwd) は、現在のフォルダーにあるすべての HDL ファイルをインポートし、対応する Simulink モデルを生成します。

例: importhdl('root/example/hdlsrc') は、指定されたパス上にあるすべての HDL ファイルをインポートし、対応する Simulink モデルを生成します。相対パスまたは絶対パスを指定できます。

例: importhdl('subfolder') は、指定されたサブフォルダーの配下にあるすべての HDL ファイルをインポートし、対応する Simulink モデルを生成します。既定では、importhdl は再帰的フォルダーを含むサブフォルダーを解析します。

名前と値の引数

オプションの引数のペアを Name1=Value1,...,NameN=ValueN として指定します。ここで、Name は引数名で、Value は対応する値です。名前と値の引数は他の引数の後に指定しなければなりませんが、ペアの順序は重要ではありません。

例: importhdl({'top.vhd','subsystem1.vhd','subsystem2.vhd'},Language="VHDL") は、指定された VHDL® ファイルをインポートし、対応する Simulink モデルを生成します。

HDL コードを含む入力ソース ファイルの言語。文字ベクトルとして指定します。

例: importhdl('fifo.v',Language="Verilog") は、Verilog ファイル fifo.v をインポートし、対応する Simulink モデル fifo.slx を生成します。

HDL コードの最上位モジュールの名前。文字ベクトルとして指定します。この名前は、生成された Simulink モデル内で最上位 Subsystem の名前になり、HDL インポートはこの下にサブシステム階層を作成します。入力 HDL ファイルに複数の最上位モジュールが含まれている場合、TopModule プロパティを使用して Simulink モデルの生成に使用する最上位モジュールを指定します。

例: importhdl('full_adder.v',topModule="two_half_adders") は、Verilog ファイル full_adder.v をインポートし、two_half_adders を最上位サブシステムとして、対応する Simulink モデル full_adder.slx を生成します。

順序回路のクロック、リセット、クロック イネーブル信号の名前。文字ベクトルの cell 配列として指定します。クロック バンドル信号の既定の名前は次のとおりです。

クロック信号 -

clk、clockリセット信号 -

rst、resetクロック イネーブル信号 -

clk_enb、clk_en、clk_enable、enb、enable

クロック バンドル情報を指定しない場合、HDL インポートは既定の値を使用します。入力ファイルの解析時に、HDL インポートが ClockBundle で指定されたクロック名と異なるクロック名を識別した場合、インポートはエラーを生成します。

例: importhdl('example.v','clockBundle',{'clk','rst','clk_enb'}) は、指定されたクロック バンドル情報をもつ Verilog ファイル example.v をインポートします。

生成された Simulink モデルに BlackBox サブシステムとしてインポートされる HDL 入力ファイル内の 1 つ以上のモジュールの名前。BlackBox としてインポートされる Subsystem ブロックは、モジュール定義に指定した入力端子と出力端子を使用します。サブシステムの内部では、入力端子は Terminator ブロックに接続され、zero の値をもつ Constant ブロックは出力端子に接続されています。この機能を使用して、ベンダー固有の IP を BlackBox サブシステムとしてモデルにインポートします。

例: importhdl({'example.v,'example1.v','example2.v','xilinxIP.v},topModule="top",blackBoxModule="xilinxIP") は、xilinxIP を BlackBox モジュールとして、指定された Verilog ファイルをインポートします。Simulink モデル内の対応するサブシステムでは、入力端子が Terminator ブロックに接続され、定数値 0 をもつ Constant ブロックが出力端子に接続されます。

importhdl の実行によって生成された Simulink モデル内のブロックを自動的に調整します。既定では、autoPlace は on です。importhdl は、Simulink.BlockDiagram.arrangeSystem を使用してブロックの再配置、サイズ変更、移動を行ったり、信号線をまっすぐにすることで、モデル レイアウトを改良します。

例: importhdl('example.v','autoPlace','on') は、Verilog ファイル example.v をインポートし、改良されたモデル レイアウトをもつ Simulink モデルを生成します。

制限

関数 importhdl は Mac プラットフォームではサポートされていません。

バージョン履歴

R2018b で導入

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)