このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

HDL コードのインポートと Simulink モデルの生成

合成可能な HDL コードを Simulink® モデリング環境にインポートするには、importhdl 関数を使用します。この関数は、入力 HDL ファイルを解析し、Simulink モデルを生成します。モデルは、機能や動作の観点から HDL コードを視覚的に表すブロック線図環境です。HDL コードを Simulink にインポートして、モデルベースのシミュレーション環境でモデルをコンパイルしてシミュレーションを実行することで、HDL コードの機能を検証できます。また、信号をテスト ポイントとしてログに記録して内部信号をデバッグすることもできます。

HDL Coder™ ソフトウェアを使用して Simulink モデルから以前に生成された HDL コードをインポートする場合は importHDL 関数を使用しないでください。作成する Simulink モデルは通常、抽象化レベルが高くなります。importHDL で生成されるモデルは抽象化レベルが低くなる可能性があります。このモデルから生成した HDL コードは、量産コードに使用できない場合があります。

量産 HDL コードを生成するには、Simulink ブロック、MATLAB® コード、または Stateflow® グラフを使用してアルゴリズムを開発します。次に、HDL Coder を使用してコードを生成します。

要件

Simulink モデルを生成するには、インポートする HDL ファイルが次の状態であることを確認します。

構文エラーがない。

合成可能である。

インポートに対してサポートされている Verilog® または VHDL® 構造を使用している。詳細については、HDL インポートでサポートされている Verilog 構造およびSupported VHDL Constructs When Generating Simulink Models from VHDL Codeを参照してください。

HDL コードのインポート

HDL コードをインポートするには、MATLAB コマンド ウィンドウで、関数 importhdl を実行します。この関数は、指定された HDL 入力ファイルを解析して対応する Simulink モデルを生成し、そのモデルを開くためのリンクを提供します。

たとえば、比較器の Verilog コードについて考えます。

// File Name: comparator.v // This module implements a simple comparator module `define value 12 module comparator (clk, rst, a, b); input clk, rst; input [1:0] a; output reg [1:0] b; parameter d = 2'b11; always@(posedge clk) begin if (rst) b <= 0; else if (a < `value) b <= a + 1; end endmodule

importhdl を実行して HDL 入力ファイルの名前を指定します。ファイル名はさまざまな方法で指定できます。importhdl の入力引数 'FileNames' を参照してください。 importhdl('comparator.v')HDL コードで使用する構造体で、Add や Product などの単純な Simulink ブロックから Dual Rate Dual Port RAM のような RAM ブロックまで推定できます。推定されるさまざまな Simulink モデルの他の例については、importhdl を参照してください。

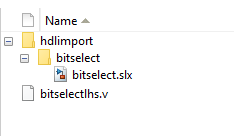

モデルの場所

生成された Simulink モデルは、指定した入力 HDL ファイル内の最上位モジュールに従って名前が付けられます。このモデルは、現在の作業フォルダーに対して相対的なパス hdlimport/TopModule に保存されます。たとえば、bitselect を最上位モジュール名として使用する関数 importhdl に bitselectlhs.v という名前のファイルを入力する場合、生成された Simulink モデルの名前は bitselect.slx になり、現在の作業フォルダーに対して相対的なパス hdlimport/bitselect に保存されます。

エラーと警告

importhdl 関数を実行すると、関数は入力 HDL コードの構文とセマンティクスを検証します。セマンティック検証では、モジュールのインスタンス化構造、モジュール定義での未使用の端子、always ブロックのセンシティビティ リストなどをチェックします。HDL インポートが失敗すると、importhdl はエラー メッセージ、およびファイル名と行番号へのリンクを提供します。

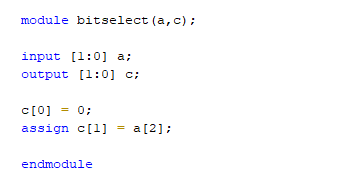

たとえば、次のような bitselect モジュールの Verilog コードについて考えます。

関数 importhdl を実行すると、HDL インポートが次のエラー メッセージを生成します。

Parser Error: bitselectlhs.v:6:2: error:Syntax Error near '['.

エラー メッセージは、6 行目に構文エラーがあることを示しています。このエラーを修正するには、構文を代入ステートメントに変更します。

assign c[0] = 0;

制限

HDL インポートでは次のことはサポートされません。

Mac プラットフォーム。

読み取り専用フォルダーからの HDL ファイルのインポート。

関数

importhdlに入力した HDL コードを解析する、読み取り専用ファイル システム内での前処理ファイルの生成。1 より多いクロック信号。

マルチレート モジュール。

1024を超える入力を指定した Multiport Switch 推定。HDL コードから推定される Multiport Switch ブロックに対して1024を超える入力を指定すると、HDL インポートでエラーが発生します。このエラーが生成されるのは、ブロックに対する1024を超える入力が Simulink モデリング環境でサポートされないためです。サポートされていない HDL 構造を使用する HDL ファイルのインポート。HDL インポートでサポートされている Verilog 構造およびSupported VHDL Constructs When Generating Simulink Models from VHDL Codeを参照してください。