HDL インポートでサポートされている Verilog 構造

合成可能な Verilog® コードを Simulink® モデリング環境にインポートするには、importhdl 関数を使用します。HDL コードで使用されている構造が HDL インポートでサポートされていることを確認します。

以下の表には、HDL コードをインポートするときに使用できる、サポートされている Verilog 構造がリストされています。サポートされていない構造を使用する場合、入力 HDL ファイルの解析時に HDL インポートがエラーを生成します。Verilog HDL インポートでは、HDL コード内の特定の構造の存在を無視できる場合があります。詳細については、表のコメント セクションを参照してください。

モジュール定義とインスタンス化

| Verilog 構造 | サポート | コメント |

|---|---|---|

| ライブラリ宣言 | いいえ | – |

| コンフィギュレーション宣言 | いいえ | – |

| モジュール宣言 | はい | 複数のサンプルレートと複数のクロック入力はサポートされません。 |

| モジュールのパラメーター端子リスト | はい | – |

| 端子宣言 | はい | INOUT 端子はサポートされません。 |

| 端子を使用しないモジュール | いいえ | – |

| ローカル パラメーター宣言 | はい | – |

| パラメーター宣言 | はい | 最大サイズが 64 ビットのパラメーターと定数を使用できます。既定では、パラメーター サイズは 32 ビットです。 |

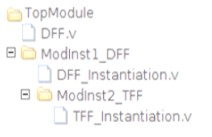

| モジュールのインスタンス化 | はい |

|

データ型とベクトル

| Verilog 構造 | サポート | コメント |

|---|---|---|

| ネット宣言 (Wire、Supply0、Supply1) | はい | – |

| 実数宣言 | いいえ | – |

| 文字列宣言 | いいえ | – |

| ベクトル宣言 | はい | – |

| 配列のサポートと配列のインデックス付け | はい | – |

| reg 宣言 | はい | – |

| 整数宣言 | はい | – |

識別子とコメント

| Verilog 構造 | サポート | コメント |

|---|---|---|

| 字句トークン (空白、演算子、コメント) | はい | – |

| 識別子 (単純、エスケープ) | はい | – |

| システム関数 ($signed、$unsigned) | はい | – |

| 属性インスタンス | いいえ | HDL インポートはこれらの構造を無視します。 |

| コメント | いいえ | HDL インポートはこれらの構造を無視します。 |

| 数値 (10 進数、バイナリ、16 進数、8 進数) | はい | – |

| コンパイラ命令 (`define、`undef、`ifndef、`else if) | はい | – |

代入

| Verilog 構造 | サポート | コメント |

|---|---|---|

| 連続代入 | はい | – |

| ブロッキング代入 | はい | -- |

| 非ブロッキング代入 | はい | – |

手続き的代入 (Always ブロック) | はい | – |

演算子

| Verilog 構造 | サポート | コメント |

|---|---|---|

| 算術演算子 (+、-、*、**、/、<<<、>>>) | はい | – |

| 論理演算子 (<<、>>、!、&&、| |、==、!=) | はい | – |

| 関係演算子 (>、<、>=、<=、==、!=) | はい | – |

| ビット演算子 (~、&、|、^、~^、^~) | はい | – |

| 単項演算子 (+、-) | はい | 限られたデータ型でサポート |

| べき乗演算子 | はい | 限られたデータ型でサポート |

| 条件演算子 (?:) | はい | – |

| 連結 | はい | – |

| ビット選択 | はい | – |

| 簡約演算子 (&、~&、|、~|、^、~^、または ^~) | はい | – |

各種演算子の使用方法を示す例については、さまざまな演算子に対応する Verilog コードからの Simulink モデルの生成を参照してください。

条件付きステートメントとループ ステートメント

| Verilog 構造 | サポート | コメント |

|---|---|---|

| If-else ステートメント | はい | – |

| 条件演算子 (?:) | はい | – |

| For ループ | はい | – |

| loop generate 文 | はい | for-generate、case-generate、if-generate などの loop generate 文がサポートされます。 |

| conditional generate 文 | いいえ | – |

| generate 領域 | いいえ | – |

| genvar 宣言 | いいえ | – |

| Case ステートメント | はい | casex ステートメントと casez ステートメントもサポートされます。 |

手続きブロックとイベント

| Verilog 構造 | サポート | コメント |

|---|---|---|

| タスク宣言 | いいえ | – |

| 初期構造 (ROM モデリング) | いいえ | – |

| 連続ブロック | はい | – |

| ブロック宣言 | はい | – |

| イベント制御ステートメント | はい | – |

| 関数呼び出し | はい | HDL インポートは再帰的な関数呼び出しをサポートしません。 |

| タスク イネーブル | いいえ | – |

Always 文 | はい | – |

| 関数宣言 | はい | – |

その他の構造

| Verilog 構造 | サポート | コメント |

|---|---|---|

| ゲートのインスタンス化 | いいえ | – |

| specparam | いいえ | – |

| specify ブロック | いいえ | – |

| セマンティック検証 (未使用の端子、正しいモジュールのインスタンス化) | はい | – |

| クロック バンドルの特定 | はい | 複数のサンプルレートと複数のクロック信号はサポートされていません。 |

| レジスタ推定 | はい | – |

| Compare to Constant ブロック推定 | はい | – |

| Gain ブロック推定 | はい | – |

| RAM 推定 | はい | – |

| ROM 推定 | いいえ | – |

| カウンター推定 | いいえ | – |

| 駆動強度 | いいえ | – |

制限と考慮事項

Verilog インポートでは以下はサポートされません。

読み取り専用フォルダーからの Verilog ファイルのインポート。

関数

importhdlに入力した HDL コードを解析する、読み取り専用ファイル システム内での前処理ファイルの生成。属性インスタンスとコメント。これらは無視されます。

#25などの (#) 遅延値。この値は無視されます。列挙データ型。

1 より多いクロック信号。

マルチレート モジュール。

再帰モジュールのインスタンス化。

1024を超える入力を指定した Multiport Switch 推定。Verilog コードから推定される Multiport Switch ブロックに対して1024を超える入力を指定すると、Verilog インポートでエラーが発生します。このエラーが生成されるのは、ブロックに対する1024を超える入力が Simulink モデリング環境でサポートされないためです。Verilog コードからの ROM 検出。

サポートされていないデータフロー モデリング パターンを使用する HDL ファイルのインポート。サポートされない Verilog データフロー パターンを参照してください。