面積の最適化

RAM マッピング、リソース共有、ストリーミング

面積の最適化を適用することで、ターゲットの FPGA または SoC デバイスでの設計によるリソース使用量を削減します。RAM マッピング、リソース共有、ストリーミング、およびその他の面積の最適化を使用して、設計に必要な面積を削減できます。面積の最適化の概要については、HDL Coder での速度および面積の最適化を参照してください。

トピック

RAM マッピング

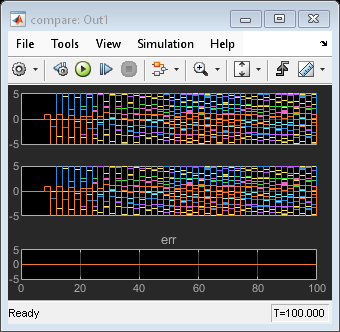

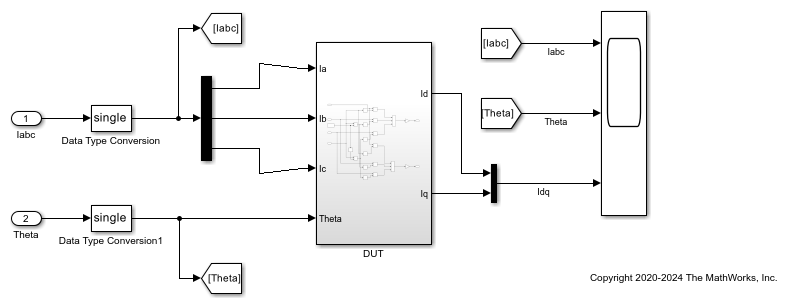

- Apply RAM Mapping to Optimize Area

Map elements to RAM to optimize area on your target hardware. - Manage How HDL Coder Maps RAM

Learn how HDL Coder™ settings affect RAM mapping. - MATLAB Function ブロックを使用した RAM マッピング

モデル内の MATLAB Function ブロックでMapPersistentVarsToRAMパラメーターを指定して RAM マッピング最適化を使用する方法。 - ROM への行列のマッピング

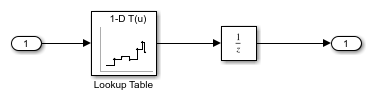

行列定数を ROM にマッピングするには、次の条件があります。

リソース共有、ストリーミング、およびその他の面積の最適化

- リソース共有

リソース共有を使用してチップ面積を節約する方法。 - ストリーミング

ストリーミングの概要と、最適化を使用してリソースを節約する方法。 - フィードバック ループの検出

最適化を抑制するフィードバック ループの強調表示 - フィルターのサブシステム最適化

リソース共有とパイプラインの最適化オプションを選択する。 - MATLAB Datapath アーキテクチャを使用した、MATLAB Function ブロック境界を越えた HDL 最適化

MATLAB Function ブロック内、および MATLAB Function ブロックを越えたその他の Simulink® ブロックとの間で最適化を適用する。 - Configure Custom Synthesis Attributes for Simulink Blocks

This example shows how to configure custom synthesis attributes for a Simulink model using the command-line interface and propagate them to the generated HDL code. - Use Synthesis Attributes to Map Adders to DSPs on FPGAs

Apply synthesis attributes to map adders to dedicated DSP slices for optimized FPGA implementation. (R2026a 以降)