Turbo Encoder

並列連結符号化スキームを使用したバイナリ データの符号化

ライブラリ:

Communications Toolbox /

Error Detection and Correction /

Convolutional

説明

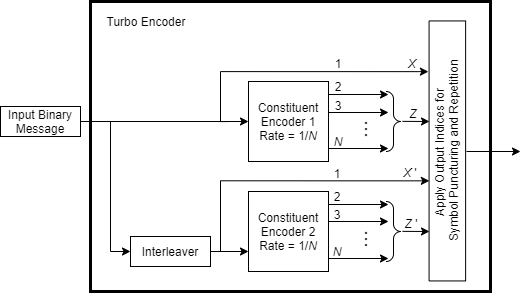

Turbo Encoder ブロックは、並列連結符号化スキームを使用してバイナリ入力信号を符号化します。この符号化スキームは、2 つの同一の畳み込み符号化器と 1 つの内部インターリーバーを備えています。それぞれの構成符号化器は、テール ビットで個別に終了します。構成符号化器の詳細については、並列連接畳み込み符号化スキームを参照してください。

このアイコンには、利用可能なすべての端子を使用したブロックが表示されています。

![]()

例

端子

入力

出力

パラメーター

詳細

参照

[1] Berrou, C., A. Glavieux, and P. Thitimajshima. “Near Shannon Limit Error-Correcting Coding and Decoding: Turbo-Codes.” Proceedings of ICC 93 - IEEE® International Conference on Communications, 2: 1064–70. Geneva, Switzerland: IEEE, 1993. https://doi.org/10.1109/icc.1993.397441.

[2] Benedetto, S., G. Montorsi, D. Divsalar, and F. Pollara. "A Soft-Input Soft-Output Maximum A Posterior (MAP) Module to Decode Parallel and Serial Concatenated Codes." Jet Propulsion Lab TDA Progress Report (November 1996): 42–127.

[3] Schlegel, Christian, and Lance Perez. Trellis and Turbo Coding. IEEE Press Series on Digital & Mobile Communication. Piscataway, NJ; Hoboken, NJ: IEEE Press; Wiley-Interscience, 2004.

[4] 3GPP TS 36.212. "Multiplexing and channel coding." 3rd Generation Partnership Project; Technical Specification Group Radio Access Network; Evolved Universal Terrestrial Radio Access (E-UTRA).

拡張機能

バージョン履歴

R2011b で導入