General CRC Generator

生成多項式に基づいて CRC 符号ビットを生成し、入力データ フレームに付加する

ライブラリ:

Communications Toolbox /

Error Detection and Correction /

CRC

説明

General CRC Generator ブロックは入力データ フレームごとに巡回冗長検査 (CRC) 符号ビットを生成し、それらをフレームに付加します。詳細については、CRC 発生器の動作を参照してください。

例

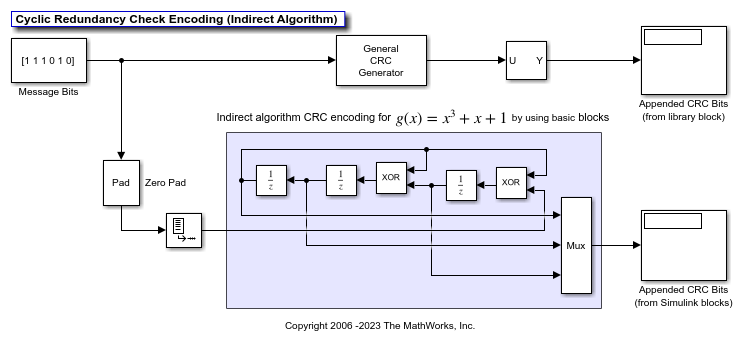

Simulink® ブロックを使用することによって生成多項式 g(x) = x³ + x + 1 と間接アルゴリズムで CRC を構成してフレームに CRC ビットを付加し、その結果を、同じ構成をもつ Communications Toolbox™ の General CRC Generator ブロックの演算と比較します。

cm_crcgen_indirect モデルは、レジスタが特定の初期状態に設定された状態で、長さ 6 ビットの既知の入力メッセージについて両方の CRC 発生器を実行します。初期状態は、PreLoadFcn コールバック関数を使用してワークスペース変数 iniStates に読み込まれます。詳細については、モデル コールバック (Simulink)を参照してください。

シミュレーションを実行すると、General CRC Generator ブロックを使用して生成された追加の CRC ビットと、Simulink® ブロックによって作成された生成多項式を使用して生成された CRC が表示されます。モデルの出力を表示し、両方の実装の結果が一致することを確認します。異なるメッセージ ビット、または異なる初期状態を使用して、モデルを実行することができます。初期状態を調整するには、シミュレーションを実行する前にワークスペース変数 iniStates を変更します。

高次多項式の指定など、CRC 発生器にその他の変更を加えるには、個々の Simulink® ブロックから作成された生成多項式のモデル ブロックのレイアウトを修正しなければなりません。ただし、General CRC Generator ブロックを再構成する場合は、パラメーターの設定の更新だけで済みます。

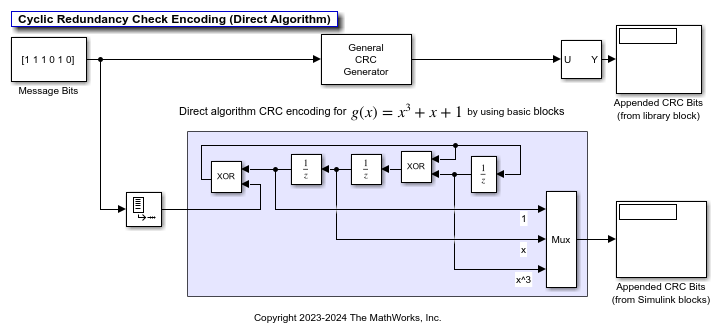

Simulink® ブロックを使用することによって生成多項式 g(x) = x³ + x + 1 と直接アルゴリズムで CRC を構成してフレームに CRC ビットを付加し、その結果を、同じ構成をもつ Communications Toolbox™ の General CRC Generator ブロックの演算と比較します。

cm_crcgen_direct モデルは、レジスタが特定の初期状態に設定された状態で、長さ 6 ビットの既知の入力メッセージについて両方の CRC 発生器を実行します。初期状態は、PreLoadFcn コールバック関数を使用してワークスペース変数 iniStates に読み込まれます。詳細については、モデル コールバック (Simulink)を参照してください。

シミュレーションを実行すると、General CRC Generator ブロックを使用して生成された追加の CRC ビットと、Simulink® ブロックによって作成された生成多項式を使用して生成された CRC が表示されます。モデルの出力を表示し、両方の実装の結果が一致することを確認します。異なるメッセージ ビット、または異なる初期状態を使用して、モデルを実行することができます。初期状態を調整するには、シミュレーションを実行する前にワークスペース変数 iniStates を変更します。

高次多項式の指定など、CRC 発生器にその他の変更を加えるには、個々の Simulink® ブロックから作成された生成多項式のモデル ブロックのレイアウトを修正しなければなりません。ただし、General CRC Generator ブロックを再構成する場合は、パラメーターの設定の更新だけで済みます。

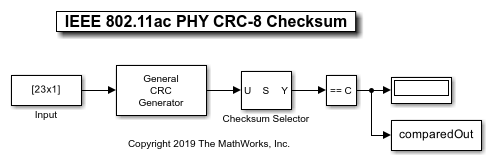

802.11™-2016、節 21.3.10.3 に示されている例の CRC-8 チェックサムを生成し、期待される CRC と比較します。

モデルの検証

802.11-2016 の CRC 計算に一致させるため、"General CRC Generator" ブロック マスクは生成多項式を  、初期状態を 1、最終的な XOR パラメーターを 1 に設定し、直接法を選択します。

、初期状態を 1、最終的な XOR パラメーターを 1 に設定し、直接法を選択します。

このシミュレーションは、802.11-2016 規格の節 21.3.10.3 にある例をモデル化する 1 つの入力フレームを処理するように構成されています。この例では、入力ビット ストリーム {m0, ... m22} は {1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1} で、期待される CRC チェックサム {c7, ... c0} は {0 0 0 1 1 1 0 0} です。生成された CRC チェックサム ビットが期待されるビットと比較され、8 ビット CRC チェックサムの各等価ビットに対して 1 が出力されます。

comparedOut = 8×1 logical array 1 1 1 1 1 1 1 1

参考文献

[1] IEEE Std 802.11™-2016 IEEE Standard for Information Technology—Local and Metropolitan Area Networks—Specific Requirements Part 11:Wireless LAN MAC and PHY Specifications.

端子

入力

入力信号。バイナリ列ベクトルとして指定します。入力フレームの長さは [Checksums per frame] パラメーターの値の倍数でなければなりません。

データ型: double | Boolean

出力

出力コードワード フレーム。入力信号のデータ型を継承するバイナリ列ベクトルとして返されます。出力には、CRC ビット シーケンスが付加された入力データ フレームが含まれています。

出力フレームの長さは m + k * r です。ここで、m は入力フレームのサイズ、k はフレームあたりのチェックサムの数、r は生成多項式の次数です。

パラメーター

ブロック パラメーターを対話的に編集するには、プロパティ インスペクターを使用します。Simulink® ツールストリップの [シミュレーション] タブの [準備] ギャラリーで [プロパティ インスペクター] を選択します。

CRC アルゴリズムの生成多項式。次のいずれかとして指定します。

'z^3 + z^2 + 1'などの多項式の文字ベクトル。バイナリ行ベクトル。降べきの順に並べた生成多項式の係数を表します。このベクトルの長さは (N+1) です。ここで N は生成多項式の次数です。たとえば、

[1 1 0 1]は、多項式 x3+ z2+ 1 を表します。多項式の非ゼロの項の z の指数を降べきの順に含む整数行ベクトル。たとえば、

[3 2 0]は、多項式 z3 + z2 + 1 を表します。

詳細については、Communications Toolbox での多項式の表現を参照してください。

既定値は CRC-16-CCITT 生成多項式です。次の表に、よく使用される生成多項式の例を示します。

| CRC 名 | 生成多項式 |

|---|---|

| CRC-32 | 'z^32 + z^26 + z^23 + z^22 + z^16 + z^12 + z^11 + z^10 + z^8 + z^7 + z^5 + z^4 + z^2 + z + 1' |

| CRC-24 | 'z^24 + z^23 + z^14 + z^12 + z^8 + 1' |

| CRC-16 | 'z^16 + z^15 + z^2 + 1' |

| CRC-16-CCITT | 'z^16 + z^12 + z^5 + 1' |

| 反転 CRC-16 | 'z^16 + z^14 + z + 1' |

| CRC-8 | 'z^8 + z^7 + z^6 + z^4 + z^2 + 1' |

| CRC-4 | 'z^4 + z^3 + z^2 + z + 1' |

例: 'z^7 + z^2 + 1'、[1 0 0 0 0 1 0 1]、および [7 2 0] は同一の多項式 p(z) = z 7 + z 2 + 1 を表します。

内部シフト レジスタの初期状態。バイナリ スカラー、または生成多項式の次数に等しい長さをもつバイナリ行ベクトルとして指定します。スカラー値は、生成多項式の次数に等しい長さの行ベクトルに拡張されます。

選択すると、CRC チェックサムの計算に直接アルゴリズムが使用されます。オフにした場合、ブロックでは、CRC チェックサムの計算に非直接アルゴリズムが使用されます。

直接アルゴリズムと非直接アルゴリズムの詳細については、誤りの検出と訂正を参照してください。

選択すると、シフト レジスタに入力される前に入力データがバイト単位で反転されます。[Reflect input bytes] を選択する場合、入力フレーム長を [Checksums per frame] パラメーターの値で除算したものが、整数かつ 8 の倍数でなければなりません。[Reflect input bytes] をオフにすると、入力データは反転されません。

選択すると、入力データがシフト レジスタを完全に通過した後に CRC チェックサムが 180° 反転されます。[Reflect checksums before final XOR] をオフにすると、CRC チェックサムは反転されません。

Final XOR。バイナリ スカラー、または生成多項式の次数に等しい長さをもつバイナリ行ベクトルとして指定します。CRC を入力データに追加する前に、[Final XOR] パラメーターの値を使用して、XOR 演算を CRC チェックサムに対して実行します。スカラー値は、生成多項式の次数に等しい長さの行ベクトルに拡張されます。0 に設定すると、XOR 演算を実行しないことと等価になります。

各フレームで計算されるチェックサムの数。正の整数として指定します。

ブロックの特性

データ型 |

|

多次元信号 |

|

可変サイズの信号 |

|

アルゴリズム

General CRC Generator ブロックは、間接または直接の CRC アルゴリズムを使用した CRC チェックサムの生成をサポートします。

間接 CRC アルゴリズム

間接 CRC アルゴリズムは、多項式 M に対応するバイナリ データ ベクトルを受け取り、多項式 C に対応する r ビットのチェックサムを追加します。xr による乗算は入力ベクトルを左側に r ビット シフトすることに相当するので、入力ベクトルとチェックサムの連結は、多項式 T = M×xr + C に対応します。アルゴリズムは、T が次数 r の定義済み多項式 P (生成多項式) によって除算されるように C を選択します。

アルゴリズムは、T を P で除算し、チェックサムを剰余に対応するバイナリ ベクトルに等しくなるように設定します。したがって、T = Q×P + R の場合 (ここで、R は r より小さい次数の多項式)、チェックサムは R に対応するバイナリ ベクトルです。アルゴリズムは、チェックサムの長さが r になるように、必要に応じてチェックサムの先頭に 0 を追加します。

CRC アルゴリズムの伝送位相を実装する CRC 生成機能は、以下の処理を行います。

入力データ ベクトルを r ビットだけ左にシフトし、対応する多項式を P で除算します。

チェックサムを長さ r (ステップ 1 の剰余に相当) のバイナリ ベクトルと等しくなるように設定します。

チェックサムを入力データ ベクトルに追加します。結果は出力ベクトルです。

先に説明したように、CRC 検出機能は、その入力ベクトル全体のチェックサムを計算します。

CRC アルゴリズムは、バイナリ ベクトルを使用してバイナリ多項式を降べきの順で表します。たとえば、ベクトル [1 1 0 1] は、多項式 x3+ x2+ 1 を表します。

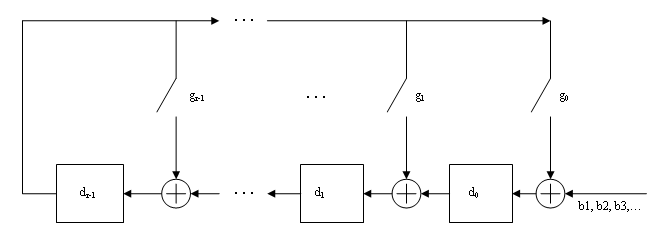

ビットは、最小のインデックス ビットから最大のインデックス ビットに向かって線形フィードバック シフト レジスタ (LFSR) に入力されます。入力メッセージ ビットのシーケンスは、メッセージ多項式の係数を降べきの順で表します。メッセージ ベクトルは r 個の 0 で拡張され、LFSR をフラッシュします (ここで r は生成多項式の次数です)。左端のレジスタ ステージからの出力 d(1) が 1 の場合、シフト レジスタ内のビットは生成多項式の係数と XOR 計算されたものです。拡張されたメッセージ シーケンスが LFSR を介して完全に送信されると、レジスタにはチェックサム [d(1) d(2) . . . d(r)] が含まれます。これはバイナリ長除算の実装です (メッセージ シーケンスが分子で多項式が分母です)。CRC チェックサムは、除算演算の剰余です。

直接 CRC アルゴリズム

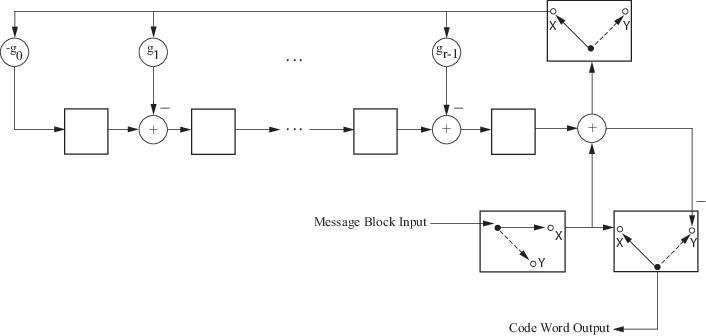

次のブロック線図は直接 CRC アルゴリズムを示しています。

"メッセージ ブロック入力" が の場合の "コード ワード出力" は次のようになります。

直接 CRC 符号化の初期ステップは、位置 X にある 3 つのスイッチによって生起します。このアルゴリズムは k 個のメッセージ ビットを符号化器に送り込みます。これらのビットは、符号語出力の最初の k ビットです。同時に、線形フィードバック シフト レジスタ (LFSR) に k 個のビットが送信されます。k 番目のメッセージ ビットの LFSR への送り込みが完了すると、スイッチは Y の位置に移動します。この例では、LFSR には多項式除算の数値剰余が含まれます。これらのビットは、LFSR からシフトされます。これらのビットは、符号語出力の残りのビット (チェックサム) です。

CRC 発生器は、指定された生成多項式とフレームあたりのチェックサムの数に従って、CRC チェックサムを入力フレームに追加します。

内部シフト レジスタが特定の初期状態にあり、入力フレームあたり k 個のチェックサムがある場合、次のようになります。

入力信号は等しいサイズの k 個のサブフレームに分割されます。

k 個の各サブフレームの前に、初期状態のベクトルが付加されます。

CRC アルゴリズムが各サブフレームに適用されます。

各サブフレームの終わりに結果のチェックサムが付加されます。

サブフレームが連結されて、1 つの列ベクトルとして出力されます。

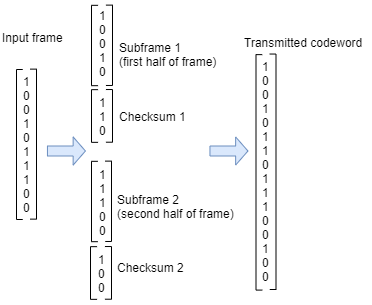

次に示すシナリオでは、10 ビットのフレームが入力であり、生成多項式 z3 + z2 + 1 で CRC チェックサムを計算します。また、初期状態は 0 で、フレームあたりのチェックサムの数は 2 です。

入力フレームはサイズ 5 の 2 つのサブフレームに分割され、サイズ 3 のチェックサムが計算されて、それぞれのサブフレームに付加されます。初期状態 [0] は CRC アルゴリズムの出力に影響を与えないため、初期状態は表示されません。出力から送信されるコードワード フレームのサイズは 5 + 3 + 5 + 3 = 16 ビットになります。

参照

[1] Sklar, Bernard. Digital Communications: Fundamentals and Applications. Englewood Cliffs, N.J.: Prentice-Hall, 1988.

[2] Wicker, Stephen B. Error Control Systems for Digital Communication and Storage. Upper Saddle River, N.J.: Prentice Hall, 1995.

拡張機能

C/C++ コード生成

Simulink® Coder™ を使用して C および C++ コードを生成します。

バージョン履歴

R2006a より前に導入

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Web サイトの選択

Web サイトを選択すると、翻訳されたコンテンツにアクセスし、地域のイベントやサービスを確認できます。現在の位置情報に基づき、次のサイトの選択を推奨します:

また、以下のリストから Web サイトを選択することもできます。

最適なサイトパフォーマンスの取得方法

中国のサイト (中国語または英語) を選択することで、最適なサイトパフォーマンスが得られます。その他の国の MathWorks のサイトは、お客様の地域からのアクセスが最適化されていません。

南北アメリカ

- América Latina (Español)

- Canada (English)

- United States (English)

ヨーロッパ

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)