このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

アーキテクチャ、動作、回路ドメインにおける SerDes Toolbox CTLE の検証

この例では、ツールの自動化によって基礎となるモデルの同期を維持しながら、複数の設計ドメインで連続時間線形イコライザー (CTLE) をシミュレートするワークフローを示します。

SerDes Toolbox™ によって生成されたモデルは、最初は、望ましいアナログ回路の動作の高レベルの仕様として機能します。HDL Verifier™ を使用すると、Simulink® CTLE モデルが SystemVerilog 動作モデルにエクスポートされ、アナログ回路が完全に設計される前にアナログ キャリブレーションのための早期のデジタル制御開発が可能になります。設計が完了すると、アナログ シミュレーションを使用して CTLE の回路実装を特性評価できます。シミュレーション結果は Simulink アーキテクチャ モデルにフィードバックされ、回路を表す Simulink モデルに変換されます。ミックスドシグナル検証に頻繁に使用される SystemVerilog 動作モデルは、HDL Verifier を介して再生成できます。仕様ベースの SystemVerilog モデルを回路を表す SystemVerilog モデルに自動的に変換し、システム モデル、動作モデル、回路モデルの同期を維持します。

はじめにと動機

この例では、SerDes Toolbox CTLE の SystemVerilog 動作エクスポート フローを示します。CTLE は、アナログベースと ADC ベースの両方の SerDes に共通するアナログ ブロックです。CTLE は、チャネル損失を均等化するアナログ ハイパス フィルタです。また、後続のイコライザー ステージまたはデータ サンプラー用に、チャネルから取得した信号を調整します。CTLE は、対象となる SerDes 標準とその実装に応じて調整できる場合があります。デジタル制御を使用して、高周波成分に対する低周波信号成分の減衰を設定できます。回路の複雑さが増すものの、さらなる CTLE チューニング機能をサポートする実装も可能です。

この例では、SerDes Toolbox で生成されたモデルから CTLE の SystemVerilog モデルを生成します。次に、Simulink と Verilog シミュレーションを使用して、CTLE モデルのオープン ループ動作の同等性を実証します。最後に、この例では、SystemVerilog モデルを使用してデジタル回路の設計と検証を支援する方法を示します。

サポート モデル、スクリプト、および HDL ファイルはプロジェクトに含まれています。

openProject('serdes_ctle_proj');SerDes Toolbox を使用して SerDes Simulink モデルを作成する

SerDes Designer から設計を作成し、それを Simulink モデルにエクスポートし、シミュレーション用に構成するには、次の手順に従います。

SerDes デザインを作成して Simulink にエクスポートする

SerDes Designer アプリを開きます。

serdesDesigner

Rx パスにパススルーと CDR ブロックを追加します。IBIS-AMI の「In」パラメータを使用できるようにするには、このキャンバス上で CTLE を直接インスタンス化しないでください。これにより、SystemVerilog および IBIS シミュレーションで Configuration Select パラメータのハードウェア制御が可能になります。モデルを Simulink にエクスポートした後、CTLE を設定できます。

Pass-Through ブロックの名前を「CTLE_core」に変更します。

![]() または、

または、models/spec_CTLE_as_passthrough.mat から提供されている SerDes Designer デザインをロードすることもできます。

エクスポート ボタンをクリックして、Simulink モデルを生成します。

Simulink モデルで CTLE を構成し、ブースト設定をパラメータ化する

このモデルを調整して CTLE を定義し、IBIS-AMI と SystemVerilog ワークフローの両方をターゲットにできるようにします。

Rx サブシステムで、CTLE_core ブロックの左下隅にある矢印をクリックして、その内容を編集します。

MATLAB システム ブロックを追加し、System object の名前を

serdes.CTLEに変更します。CTLE System object ブロック パラメータ ダイアログ ボックスの メイン タブで、モード を

1に、仕様 をDC Gain and Peaking Gainに、ピーク周波数 を20e9に、DC ゲイン を0:-1:-20に、ピーク ゲイン を0:20に設定します。ConfigSelectPortも選択します。詳細設定タブで、シンボル時間 (秒)をモデルワークスペース変数

SymbolTimeに、サンプル間隔 (秒)をモデルワークスペース変数SampleIntervalに、入力波形タイプをSampleに、CTLE適応最適化基準コントロールをSNRに、フィルター方法をCascadedに設定します。PassThrough サブシステムを削除し、MATLAB システム ブロックに置き換えます。

MATLAB システム ブロックの名前を

CTLE_coreに変更します。最上位の Rx サブシステムで、SerDes IBIS-AMI Manager アノテーションをクリックします。

AMI-Rx タブと CTLE_core ブロックを選択します。パラメータの追加ボタンをクリックします。

以下に示すように、

ConfigSelect(Boost とも呼ばれます) という名前の入力パラメータを作成します。

Rx/CTLE サブシステムで、生成されたパラメーター ブロックを ConfigSelect 入力に接続します。ConfigSelect 出力をターミネータに接続します。結果として得られる Rx/CTLE サブシステムは次のようになります。

モデルを spec_CTLE_ibisami.slx として保存します。

![]() 代わりに、提供されている models/spec_CTLE_ibisami.slx をロードすることもできます。

代わりに、提供されている models/spec_CTLE_ibisami.slx をロードすることもできます。

モデルを構成し、SystemVerilog コンポーネントを生成する

spec_CTLE_ibisami.slx モデルを使用して、Signal Integrity Toolbox™ アプリまたは同様のシグナル インテグリティ シミュレーターの Serial Link Designer 内で使用する IBIS-AMI モデルを生成します。いくつかのターゲット パラメータを変更することで、SystemVerilog 動作モデルを生成することもできます。

ターゲット SystemVerilog に合わせてモデルを構成する

SystemVerilog 生成用にモデルを設定するには、次の手順に従います。

![]() または、これらの手順をスキップして、提供されているモデル models/spec_CTLE_svdpi.slx を使用することもできます。

または、これらの手順をスキップして、提供されているモデル models/spec_CTLE_svdpi.slx を使用することもできます。

「名前を付けて保存...」をクリックし、spec_CTLE_svdpi.slx として保存します。

Simulink の アプリ メニューから HDL Verifier アプリを開きます。

左側のペインで DPI コンポーネントの生成 を選択します。

Rx/CTLE_coreサブシステムを選択し、ツールストリップにピン留めします。

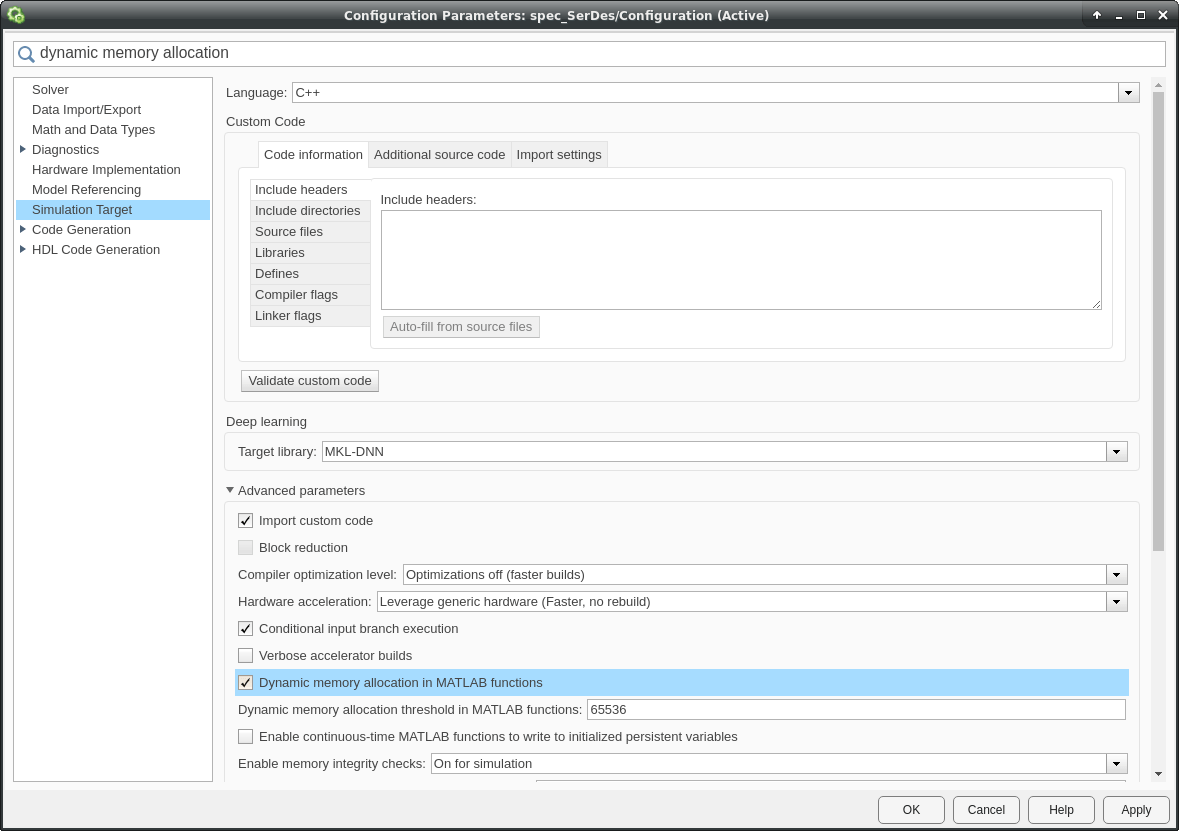

C コード設定ボタンをクリックします。ツールチェーンの場合は、

Automatically locate an installed toolchainを選択します。同じ構成パラメータ ウィンドウで、検索バーに「動的メモリ割り当て」と入力し、MATLAB 関数での動的メモリ割り当て を有効にします。

SerDes Toolbox はコールバック関数を利用して Simulink にシームレスに統合します。ただし、これらのコールバックは、HDL Verifier 経由の DPI エクスポート フローに干渉する可能性があります。コールバックを無効にするには、次のコマンドを実行してください:

set_param('spec_CTLE_svdpi/Rx/CTLE_core', 'PreCopyFcn', '');

HDL のコンポーネントはクロックで動作しないため、SystemVerilog ベースのシステムへの DPI モデルの統合は、イベントを使用して DPI 呼び出しをトリガーすることによって最も適切に処理されます。生成された SystemVerilog コードをカスタマイズ を選択し、参照 をクリックします。現在の作業ディレクトリに移動し、scripts/svdpi_setparam_event.vgt を選択します。

OK をクリックして、構成パラメータ ウィンドウを受け入れて閉じます。

Simulink と SystemVerilog シミュレーションを比較するための計測器モデル

CTLE の入力に ctle_in、出力に ctle_out という名前を付けて、Simulink と SystemVerilog シミュレーション結果を比較するようにモデルを構成します。両方の信号を選択し、「...」を選択して、信号のログ記録を選択します。

モデルを spec_CTLE_svdpi.slx として保存します。

![]() 代わりに、提供されている models/spec_CTLE_svdpi.slx をロードすることもできます。

代わりに、提供されている models/spec_CTLE_svdpi.slx をロードすることもできます。

open_system('models/spec_CTLE_svdpi');SystemVerilog 生成

ConfigSelect パラメータの調整のみに関心があるため、最適化される調整可能なパラメータに関する警告をオフにします。

warning('off','HDLLink:DPIG:AutoTunableVarMayBeOptimized');

次に、HDL Verifier タブの DPI コンポーネントの生成 をクリックして、CTLE DPI モデルを構築できます。

あるいは、コマンドラインからコンポーネントを生成することもできます。

slbuild('spec_CTLE_svdpi/Rx/CTLE_core');### Starting build procedure for model: CTLE_core ### Starting SystemVerilog DPI Component Generation ### Generating DPI H Wrapper CTLE_core_dpi.h ### Generating DPI C Wrapper CTLE_core_dpi.c ### Generating SystemVerilog module CTLE_core_dpi.sv using template /home/merickso/Documents/MATLAB/ExampleManager/merickso.Bdoc23b.j2328999.r23bI12_fixes/shared_hdlv_serdes_mixed-ex34477068/serdes_ctle_proj/scripts/svdpi_setparam_event.vgt ### Generating makefiles for: CTLE_core_dpi ### Invoking make to build the DPI Shared Library ### Successful completion of build procedure for model: CTLE_core Build Summary Top model targets built: Model Action Rebuild Reason ======================================================================= CTLE_core Code generated and compiled. Global variable gpz changed. 1 of 1 models built (0 models already up to date) Build duration: 0h 1m 35.229s

結果の DPI モデルは、現在の作業ディレクトリの CTLE_core_build フォルダーで使用できるようになります。

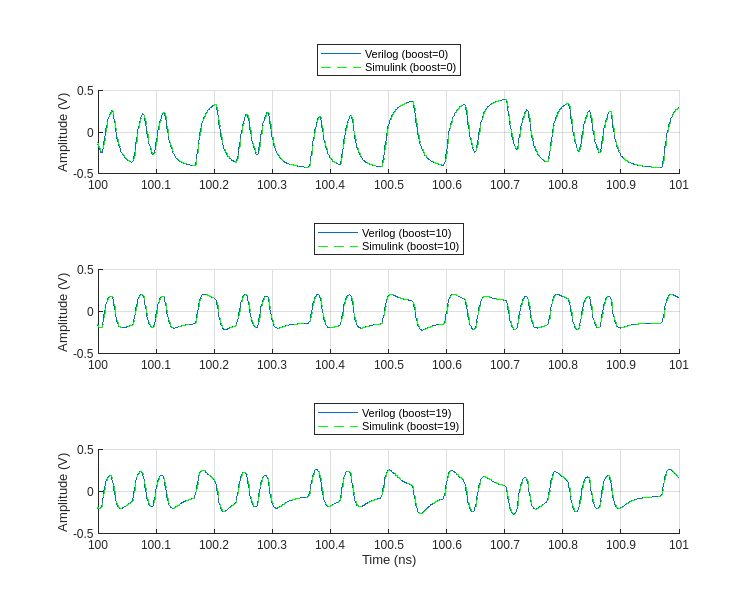

Simulink と SystemVerilog モデルの相関

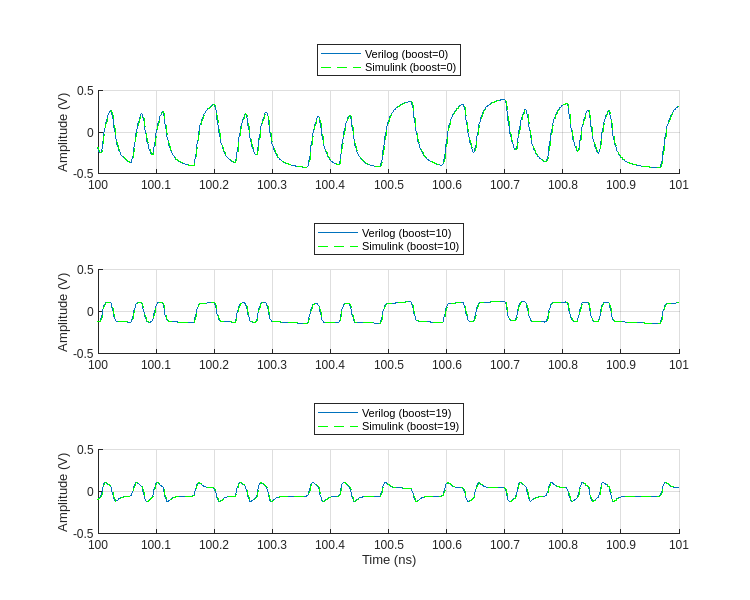

さまざまな ConfigSelect/ブースト (BOOST_VAL) 設定 (0、10、19dB) の一連のテストを実行するには、提供されている ctle_run_cases スクリプトを使用します。このスクリプトは、まず単一の BOOST_VAL 設定を使用して Simulink シミュレーションを実行します。次に、入力データと出力データを BOOST_VAL インデックス ログ ファイルに保存します: BOOST_VAL=0 の場合は simulink_out_b00.log。次に、同じ BOOST_VAL 設定を使用して Verilog シミュレーションが実行されます。Verilog シミュレーションは、Simulink シミュレーションに使用される入力波形を読み取り、それを Verilog シミュレータの DPI CTLE モデルに適用します。提供されている CTLE テストベンチは、Verilog シミュレーションのログ ファイルも作成します。ファイルの名前は、使用されるブースト設定に応じて付けられます。BOOST_VAL=0 の場合は verilog_out_b00.log です。データは ctle.v モジュール境界で記録されることに注意してください。これは、下の図の緑色のボックスで示されており、したがって、個々のシングルエンド信号が保存されます。このファイルの内容は、MATLAB® 環境に読み戻して、ctle_plot_cases スクリプトを使用して付随する Simulink 出力に対してプロットすることができます。また、GTKWaves などを使用して、MATLAB の外部で Verilog 結果の生成された VCD ファイルを視覚化することもできます。

実行スクリプトはさまざまな HDL シミュレータをサポートします。スクリプトを編集して、シミュレータのパスと環境を設定します。

% This is a MathWorks-specific setup. You must assign PATH and % other settings specific to your environment for your chosen simulator. setup_questa();

シミュレーションする CTLE モデルを選択します。

% First, choose the model to simulate current_model = 'spec_CTLE_svdpi'; %#ok<*NASGU>

次に、HDL シミュレータを選択します。

% Uncomment one of the following supported HDL simulator choices: current_hdl_simulator = 'Questa'; % Windows or Linux % current_hdl_simulator = 'Xcelium'; % Linux only % current_hdl_simulator = 'VCS'; % Linux only % current_hdl_simulator = 'Vivado'; % Linux only % Run Simulink and HDL sim and plot results comparison ctle_run_cases

Reading pref.tcl # 2022.2 # do scripts/ctle_tb_tran_questa.do # 0 # Environment BOOST_VAL=0 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:19:03 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:19:03 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:19:03 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_tran # # Top level modules: # ctle_tb_tran # End time: 12:19:03 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_tran "+BOOST_VAL=0" # Start time: 12:19:03 on Jul 21,2023 # ** Note: (vsim-3813) Design is being optimized due to module recompilation... # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_tran(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB: Running with boost = 0 # ** Note: $finish : hdl_tb/ctle_tb_tran.v(61) # Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran # End time: 12:19:07 on Jul 21,2023, Elapsed time: 0:00:04 # Errors: 0, Warnings: 0 Reading pref.tcl # 2022.2 # do scripts/ctle_tb_tran_questa.do # 10 # Environment BOOST_VAL=10 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:20:23 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:20:23 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:20:23 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_tran # # Top level modules: # ctle_tb_tran # End time: 12:20:23 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_tran "+BOOST_VAL=10" # Start time: 12:20:23 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_tran(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB: Running with boost = 10 # ** Note: $finish : hdl_tb/ctle_tb_tran.v(61) # Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran # End time: 12:20:26 on Jul 21,2023, Elapsed time: 0:00:03 # Errors: 0, Warnings: 0 Reading pref.tcl # 2022.2 # do scripts/ctle_tb_tran_questa.do # 19 # Environment BOOST_VAL=19 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:21:42 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:21:42 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:21:42 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_tran # # Top level modules: # ctle_tb_tran # End time: 12:21:43 on Jul 21,2023, Elapsed time: 0:00:01 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_tran "+BOOST_VAL=19" # Start time: 12:21:43 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_tran(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB: Running with boost = 19 # ** Note: $finish : hdl_tb/ctle_tb_tran.v(61) # Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran # End time: 12:21:46 on Jul 21,2023, Elapsed time: 0:00:03 # Errors: 0, Warnings: 0

Simulink および Verilog 実行の結果は、提供されている ctle_plot_cases.m スクリプトを使用してプロットできます。このスクリプトは、サブプロットを使用してシミュレートされたすべてのケースを 1 つの図にプロットします。

% Plot the Simulink and Verilog Simulation results

ctle_plot_cases

Verilog モデルの出力はサンプルごとに Simulink 出力に等しいことに注意してください。

シミュレートされたCTLEデータを使用してCTLEを変更する

これまで使用されてきた CTLE モデルはパラメーター化された CTLE であり、DC ゲインとピーキング ゲインはブロック マスク内のパラメーターとして指定されます。

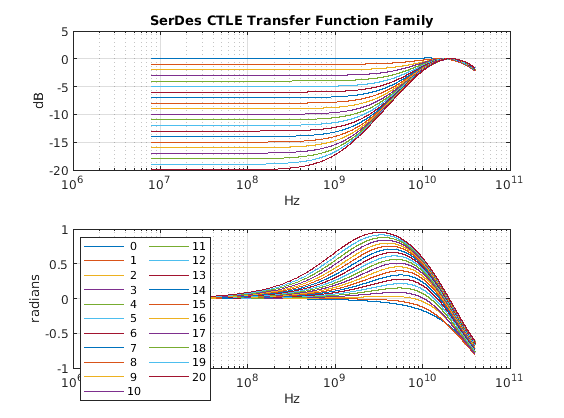

CTLE の応答を視覚化するには、応答の視覚化 ボタンをクリックします。

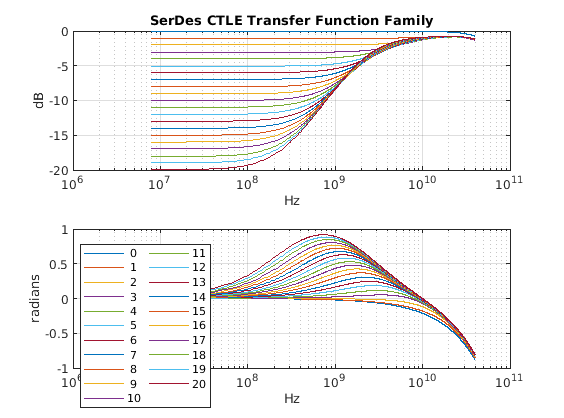

CTLE の回路実装が利用可能になると、代わりに CTLE のシミュレートされた応答を使用できます。この例では、さまざまな制御値に対して測定された CTLE 応答がシミュレートされました。これらの応答は、ゲイン・ポール・ゼロ (GPZ) の合理的な適合を生成するために使用されました。このデータは models/gpz.mat の GPZ マトリックスとして保存されます。

% Load the simulated response of the CTLE via GPZ load models/gpz

CTLE ダイアログを開き、その 仕様 パラメータを DC ゲインとピーキング ゲイン から GPZ Matrix に変更し、ゲイン ポール ゼロ マトリックス を、以前にロードした MATLAB 環境変数 gpz として指定します。

応答の視覚化 ボタンを使用してフィルターの応答を視覚化すると、以下に示すように CTLE 周波数が表示されます。

この周波数応答の DC およびブースト ゲイン値 (0 - 20dB) は同じですが、回路 CTLE のブースト帯域幅は仕様ベースの CTLE よりも高いことに注意してください。

更新された Simulink モデルを circuit_CTLE_svdpi.slx として保存し、以前使用した spec_CTLE_svdpi.slx と区別します。

Simulink と Verilog で新しい CTLE の動作を検証する

回路ベースのゲイン CTLE について、Simulink と SystemVerilog での動作を再検証しました。前の手順から続行するか、models/circuit_CTLE_svdpi.slx を開きます。

open_system('models/circuit_CTLE_svdpi.slx')まず、ツールストリップの DPI コンポーネントの生成 ボタンをクリックするか、slbuild 関数を再度呼び出して、SystemVerilog の CTLE 動作を再生成します。

slbuild('circuit_CTLE_svdpi/Rx/CTLE_core')### Starting build procedure for model: CTLE_core ### Starting SystemVerilog DPI Component Generation ### Generating DPI H Wrapper CTLE_core_dpi.h ### Generating DPI C Wrapper CTLE_core_dpi.c ### Generating SystemVerilog module CTLE_core_dpi.sv using template /home/merickso/Documents/MATLAB/ExampleManager/merickso.Bdoc23b.j2328999.r23bI12_fixes/shared_hdlv_serdes_mixed-ex34477068/serdes_ctle_proj/scripts/svdpi_setparam_event.vgt ### Generating makefiles for: CTLE_core_dpi ### Invoking make to build the DPI Shared Library ### Successful completion of build procedure for model: CTLE_core Build Summary Top model targets built: Model Action Rebuild Reason ========================================================================== CTLE_core Code generated and compiled. Generated code was out of date. 1 of 1 models built (0 models already up to date) Build duration: 0h 1m 37.822s

回路を代表する CTLE を評価するには、MATLAB スクリプトと Verilog テストベンチ (Simulink と Verilog モデルの以前の動作を検証および相関させるために使用される) を変更せずに再利用できます。

CTLE モデルを変更してシミュレーションし、テストケースを再実行して結果をプロットします。

% First, choose the model to simulate current_model = 'circuit_CTLE_svdpi'; % Run Simulink and HDL sim and plot results comparison ctle_run_cases

Reading pref.tcl # 2022.2 # do scripts/ctle_tb_tran_questa.do # 0 # Environment BOOST_VAL=0 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:24:55 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:24:55 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:24:55 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_tran # # Top level modules: # ctle_tb_tran # End time: 12:24:55 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_tran "+BOOST_VAL=0" # Start time: 12:24:55 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_tran(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB: Running with boost = 0 # ** Note: $finish : hdl_tb/ctle_tb_tran.v(61) # Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran # End time: 12:24:58 on Jul 21,2023, Elapsed time: 0:00:03 # Errors: 0, Warnings: 0 Reading pref.tcl # 2022.2 # do scripts/ctle_tb_tran_questa.do # 10 # Environment BOOST_VAL=10 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:26:13 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:26:13 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:26:13 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_tran # # Top level modules: # ctle_tb_tran # End time: 12:26:13 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_tran "+BOOST_VAL=10" # Start time: 12:26:13 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_tran(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB: Running with boost = 10 # ** Note: $finish : hdl_tb/ctle_tb_tran.v(61) # Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran # End time: 12:26:16 on Jul 21,2023, Elapsed time: 0:00:03 # Errors: 0, Warnings: 0 Reading pref.tcl # 2022.2 # do scripts/ctle_tb_tran_questa.do # 19 # Environment BOOST_VAL=19 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:27:27 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:27:27 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:27:27 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_tran # # Top level modules: # ctle_tb_tran # End time: 12:27:27 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_tran "+BOOST_VAL=19" # Start time: 12:27:28 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_tran(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB: Running with boost = 19 # ** Note: $finish : hdl_tb/ctle_tb_tran.v(61) # Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran # End time: 12:27:31 on Jul 21,2023, Elapsed time: 0:00:03 # Errors: 0, Warnings: 0

% Plot the CTLE correlation results

ctle_plot_cases

ここでも、Verilog モデルと Simulink モデルの出力はサンプルごとに一致しています。ブースト帯域幅の増加は、時間領域シミュレーション出力で確認できます。ブースト設定が高いほど、信号の低周波成分はそれほど減衰せず、全体的な信号振幅が大きくなります。

クローズドループ混合信号検証

DPI モデルの強力な使用例は、ミックスドシグナル サブシステムの開発と検証です。CTLE はアナログ回路であるため、製造後には有限かつランダムな入力オフセットが発生します。このオフセットがキャンセルされない場合、出力にオフセットが発生し、CTLE のブースト制御によって調整されます。CTLE の回路オフセットは、SerDes の起動時に調整されると想定されるため、SerDes システム モデルまたは IBIS モデルで表現されることはほとんどありません。ただし、SerDes キャリブレーション アルゴリズムをテストするには、キャリブレーション アルゴリズムを CTLE の動作モデルで表現する必要があります。

生成された CTLE DPI をラップする CTLE Verilog モデルは、このランダム入力オフセットを考慮し、全デジタル オフセット キャリブレーション エンジンのシンプルな実装も含んでいます。

ctle.v の内容を確認します。ブロック図と一致していることに注意してください。

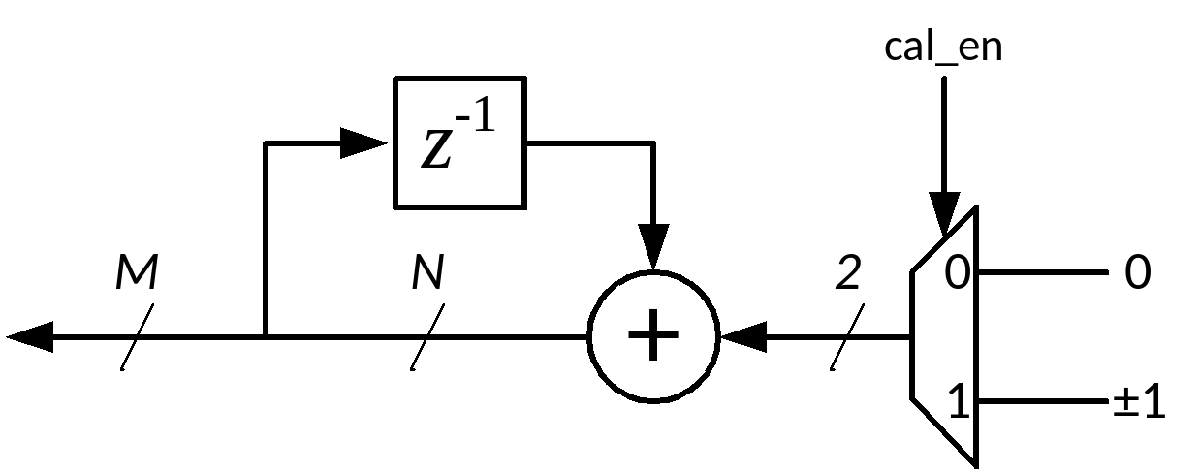

デジタル キャリブレーション エンジンの実装は、単純な 1 次積分器に基づいています。キャリブレーション中、CTLE の差動入力はコモンモード電圧に短絡され、差動入力は 0V に設定されます。CTLE の出力は非同期でサンプリングされ、入力オフセット DAC は負帰還で駆動され、有効入力オフセットをゼロにします。

提供されているテストベンチ (ctle_tb_offcomp.v) を使用して、仕様ベースまたは回路ベースの CTLE モデルを使用してオフセット キャリブレーション エンジンを検証します。

% Run offset compensation test-cases

ctle_run_offset_calsReading pref.tcl # 2022.2 # do scripts/ctle_tb_offcomp_questa.do # 0 # Environment BOOST_VAL=0 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:27:40 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:27:40 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:27:40 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_offcomp # # Top level modules: # ctle_tb_offcomp # End time: 12:27:40 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_offcomp "+BOOST_VAL=0" # Start time: 12:27:40 on Jul 21,2023 # ** Note: (vsim-3813) Design is being optimized due to module recompilation... # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_offcomp(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB_OFFCOMP: Running with boost = 0 # ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55) # Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp # End time: 12:27:44 on Jul 21,2023, Elapsed time: 0:00:04 # Errors: 0, Warnings: 0 Reading pref.tcl # 2022.2 # do scripts/ctle_tb_offcomp_questa.do # 10 # Environment BOOST_VAL=10 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:27:47 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:27:48 on Jul 21,2023, Elapsed time: 0:00:01 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:27:48 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_offcomp # # Top level modules: # ctle_tb_offcomp # End time: 12:27:48 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_offcomp "+BOOST_VAL=10" # Start time: 12:27:48 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt1 # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_offcomp(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB_OFFCOMP: Running with boost = 10 # ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55) # Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp # End time: 12:27:51 on Jul 21,2023, Elapsed time: 0:00:03 # Errors: 0, Warnings: 0 Reading pref.tcl # 2022.2 # do scripts/ctle_tb_offcomp_questa.do # 19 # Environment BOOST_VAL=19 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:27:54 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:27:54 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:27:54 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_offcomp # # Top level modules: # ctle_tb_offcomp # End time: 12:27:55 on Jul 21,2023, Elapsed time: 0:00:01 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_offcomp "+BOOST_VAL=19" # Start time: 12:27:55 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt1 # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_offcomp(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB_OFFCOMP: Running with boost = 19 # ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55) # Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp # End time: 12:27:58 on Jul 21,2023, Elapsed time: 0:00:03 # Errors: 0, Warnings: 0

% Plot the results

ctle_plot_offset_cals

仕様ベースの CTLE モデルを使用して、このオフセット キャリブレーション スキームのアルゴリズムとテストベンチを事前に開発および検証できることに注意してください。MATLAB コマンド ラインにこれらのコマンドを入力すると、そのモデルを使用して上記のテスト スイートを再実行できます。

open models/spec_CTLE_svdpi.slx current_model = 'spec_CTLE_svdpi'; ctle_run_offset_cals

Reading pref.tcl # 2022.2 # do scripts/ctle_tb_offcomp_questa.do # 0 # Environment BOOST_VAL=0 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:28:07 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:28:08 on Jul 21,2023, Elapsed time: 0:00:01 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:28:08 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_offcomp # # Top level modules: # ctle_tb_offcomp # End time: 12:28:08 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_offcomp "+BOOST_VAL=0" # Start time: 12:28:08 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt1 # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_offcomp(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB_OFFCOMP: Running with boost = 0 # ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55) # Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp # End time: 12:28:11 on Jul 21,2023, Elapsed time: 0:00:03 # Errors: 0, Warnings: 0 Reading pref.tcl # 2022.2 # do scripts/ctle_tb_offcomp_questa.do # 10 # Environment BOOST_VAL=10 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:28:15 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:28:15 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:28:15 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_offcomp # # Top level modules: # ctle_tb_offcomp # End time: 12:28:15 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_offcomp "+BOOST_VAL=10" # Start time: 12:28:15 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt1 # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_offcomp(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB_OFFCOMP: Running with boost = 10 # ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55) # Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp # End time: 12:28:18 on Jul 21,2023, Elapsed time: 0:00:03 # Errors: 0, Warnings: 0 Reading pref.tcl # 2022.2 # do scripts/ctle_tb_offcomp_questa.do # 19 # Environment BOOST_VAL=19 # ** Warning: (vlib-34) Library already exists at "work". # Errors: 0, Warnings: 1 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:28:22 on Jul 21,2023 # vlog -sv CTLE_core_build/CTLE_core_dpi.sv # -- Compiling module CTLE_core_dpi # # Top level modules: # CTLE_core_dpi # End time: 12:28:22 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022 # Start time: 12:28:22 on Jul 21,2023 # vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v # -- Compiling module ctle_cm_cal # -- Compiling module ctle # -- Compiling module ctle_tb_offcomp # # Top level modules: # ctle_tb_offcomp # End time: 12:28:22 on Jul 21,2023, Elapsed time: 0:00:00 # Errors: 0, Warnings: 0 # vsim -c -sv_lib CTLE_core_build/CTLE_core work.ctle_tb_offcomp "+BOOST_VAL=19" # Start time: 12:28:22 on Jul 21,2023 # ** Note: (vsim-8009) Loading existing optimized design _opt1 # // Questa Sim-64 # // Version 2022.2 linux_x86_64 Apr 25 2022 # // # // Copyright 1991-2022 Mentor Graphics Corporation # // All Rights Reserved. # // # // QuestaSim and its associated documentation contain trade # // secrets and commercial or financial information that are the property of # // Mentor Graphics Corporation and are privileged, confidential, # // and exempt from disclosure under the Freedom of Information Act, # // 5 U.S.C. Section 552. Furthermore, this information # // is prohibited from disclosure under the Trade Secrets Act, # // 18 U.S.C. Section 1905. # // # Loading sv_std.std # Loading work.ctle_tb_offcomp(fast) # Loading ./CTLE_core_build/CTLE_core.so # CTLE_TB_OFFCOMP: Running with boost = 19 # ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55) # Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp # End time: 12:28:26 on Jul 21,2023, Elapsed time: 0:00:04 # Errors: 0, Warnings: 0

ctle_plot_offset_cals

プロットは前回の実行と同じであることに注意してください。これは、CTLE の DC 特性のみがオフセットに影響するためです。ブースト周波数依存またはブースト帯域幅依存の特性は、オフセット キャリブレーション アルゴリズムに影響を与えません。

その他の調査

hdl_tb/ctle_tb_offcomp.v の 10 行目を編集して DC オフセットをキャンセルし、デジタル アルゴリズムの補正限界が何であるかを確認してください。

localparam offset = 0.05;

9 行目の非同期サンプラーの周波数を変更することもできます。

localparam async_freq = 400e6;

非同期サンプラーの周波数は、収束する値には影響しませんが、収束時間、つまり先ほどプロットした曲線の傾きには影響します。

デジタル アルゴリズムもパラメトリックに設計されており、積分器の幅 (上図の N) と、DAC を駆動するビット数 (M) を制御できます。これらの値は、hdl_rtl/ctle.v の 45 行目と 46 行目を編集することで変更できます。

ctle_cm_cal #(

.out_width(7),

.int_width(9))

ctle_cm_cal (

ここで、out_width は M であり、int_width は N である。

IBIS-AMI および SystemVerilog ターゲットのモデルのリセット

この例では、各ステップのモデルを示します。多くのワークフローでは、IBIS-AMI シミュレーションと SystemVerilog シミュレーションを対象とした仕様シミュレーションの設計反復中に単一のモデルが使用されます。この例で使用されているモデルのいずれかを IBIS-AMI または SystemVerilog のいずれかをターゲットにリセットするには、これらの関数のいずれかを呼び出します。

reset_model_for_svdpi('model_name') reset_model_for_ibisami('model_name')

まとめ

この例では、SerDes Designer アプリでデザインを作成し、それを Simulink にエクスポートしました。次に、SystemVerilog 環境でも調整可能な ConfigSelect の IBIS-AMI パラメータを持つ CTLE を使用するようにモデルを調整しました。SystemVerilog DPI 生成ターゲットを使用して CTLE をエクスポートし、生成されたモデルの動作を元の Simulink モデルと比較して確認しました。CTLE は GPZ マトリックスを使用して再構成され、SystemVerilog 用に再生成され、Simulink の動作と一致するように検証されました。最後に、SystemVerilog アナログ ミックスド シグナル設計がオフセット キャリブレーションを適切に処理することを確認しました。

参考文献

検証シフト左:早期の SerDes ミックス信号検証の実現 、DesignCon 2022 カンファレンス ペーパー、David Halupka 他

Find Zeros, Poles, and Gains for CTLE from Transfer Function (SerDes Toolbox)

Hammerstein-Wiener モデルとは (System Identification Toolbox)

ADC IBIS-AMI Model Based on COM (SerDes Toolbox)