このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

トランザクション レベル モデルの生成

SystemC TLM仮想プロトタイプの生成

HDL Verifier™ は Simulink® Coder™ または Embedded Coder® と統合して、SystemC™ TLM 互換のトランザクション レベル モデルをエクスポートします。このコンポーネントを動作モデルとして HDL シミュレーションに統合できます。

TLM 生成ツールは、デフォルトのソケットとメモリ構成を提供します。TLM コンポーネントのソケットとメモリ マップをカスタマイズするには、IP-XACT™ ファイルを提供します。生成されたコンポーネントを SystemC スレッドまたはコールバック関数を使用するように構成できます。

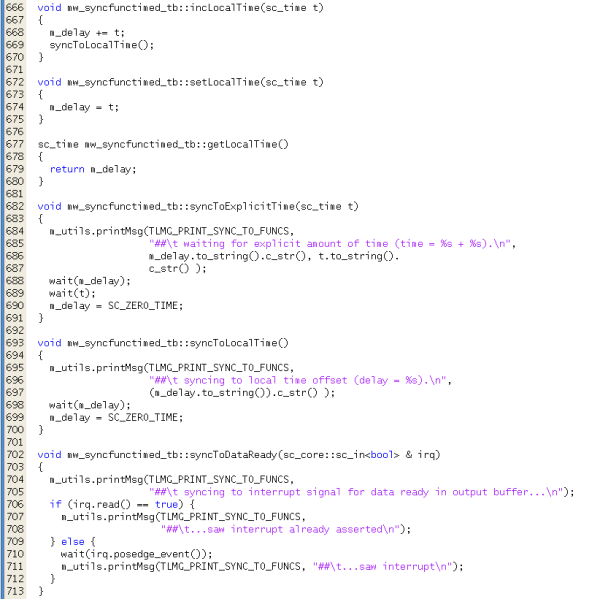

HDL Verifier は、コンポーネントを検証し、HDL シミュレータ環境への統合を支援するために、TLM テストベンチ、テストベクトル、および makefile を生成します。

この機能を使用するには、ASIC Testbench for HDL Verifier アドオンをダウンロードしてインストールしてください。

すべての TLM 生成機能が MATLAB Online で使用できるわけではありません。

モデル設定

トピック

TLMコンポーネントとテストベンチを生成する

- TLMジェネレータを使い始める

この例では、Simulink Coder ™ または Embedded Coder® のいずれかの tlmgenerator ターゲットを使用して SystemC™/TLM コンポーネントを生成するように Simulink® モデルを構成する方法を示します。 - TLM生成プロセス

HDL Verifier ソフトウェアによって生成された TLM コンポーネント ファイルを取得したら、TLM コンポーネントとオプションのテスト ベンチを OSCI SystemC ライブラリと OSCI TLM ライブラリを使用してコンパイルできます。 - TLM生成アルゴリズム

TLM コンポーネントの生成に使用するアルゴリズムは、C コードを生成できる Simulink ブロックの任意の組み合わせで作成できます。 - サブシステムのガイドラインと制限

C コードに変換できるサブシステムのほとんどは、TLM コンポーネントの生成に適しています。 - TLM コンポーネント アーキテクチャ

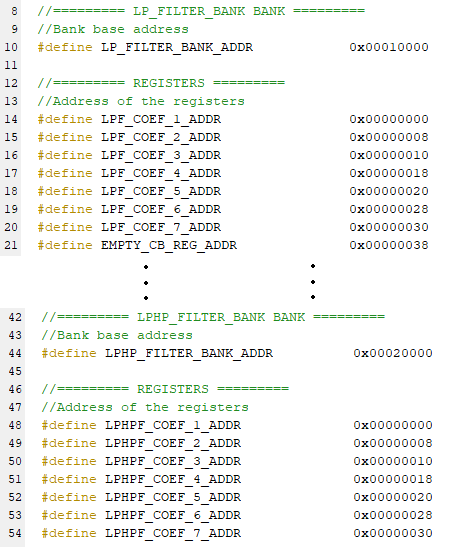

TLM ジェネレーターは、Simulink モデル サブシステムからターゲット TLM コンポーネントをエクスポートします。 - 生成されたTLMファイル

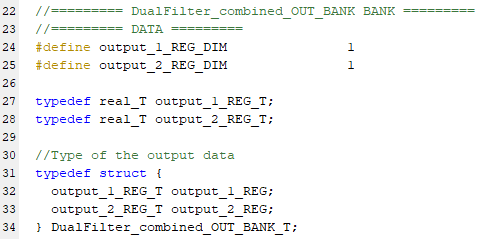

HDL Verifier ソフトウェアは次のファイルを生成します。 - TLMコンポーネント生成ワークフロー

次のワークフローは、HDL Verifier ソフトウェアを使用して TLM コンポーネントを生成するために必要な手順を示しています。

メモリマップを定義する

- インポート用の IP-XACT ファイルを準備する

生成するコンポーネントの TLM インターフェイスをカスタマイズするには、独自の IP-XACT XML ファイルを TLM ジェネレーターにインポートします。 - 生成された IP-XACT ファイルの内容

TLM ジェネレーターは、IP-XACT 1685-2009 の IEEE® 標準に準拠した IP-XACT ファイルを自動的に生成します。 - SCMLでメモリマップを実装する

SystemC モデリング ライブラリ (SCML) は、Synopsys® プロトタイピング ツールで使用するための TLM モデル インターフェイスを作成するための TLM 2.0 互換 API ライブラリです。

TLM コンポーネントのエクスポート

- TLMコンポーネントのエクスポート

コード生成が完了したら、作業フォルダーに移動します。 - TLM コンポーネント コンストラクター

生成された TLM コンポーネントのコンストラクターとデフォルトのパラメーター、およびそれらのパラメーターを変更するための情報について説明します。 - TLM コンポーネントのテスト

テストベンチ生成オプションは、[構成パラメータ] ダイアログ ボックスの [TLM Testbench] タブによって制御されます。