このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

TLM コンポーネント アーキテクチャ

コンポーネント機能の概要

TLM ジェネレーターは、Simulink® モデル サブシステムからターゲット TLM コンポーネントをエクスポートします。ターゲット TLM コンポーネントには、TLM 汎用プロトコルと汎用ペイロードを使用して読み取りおよび書き込みトランザクションをサポートする単一の TLM ソケットがあります。

メモ

この機能には ASIC Testbench for HDL Verifier アドオンが必要です。

次の図は、生成された TLM コンポーネントに指定できる最も単純な動作を示しています。メモリ マップやコマンドおよびステータス レジスタは含まれておらず、トランザクションは直ちに実行されます。

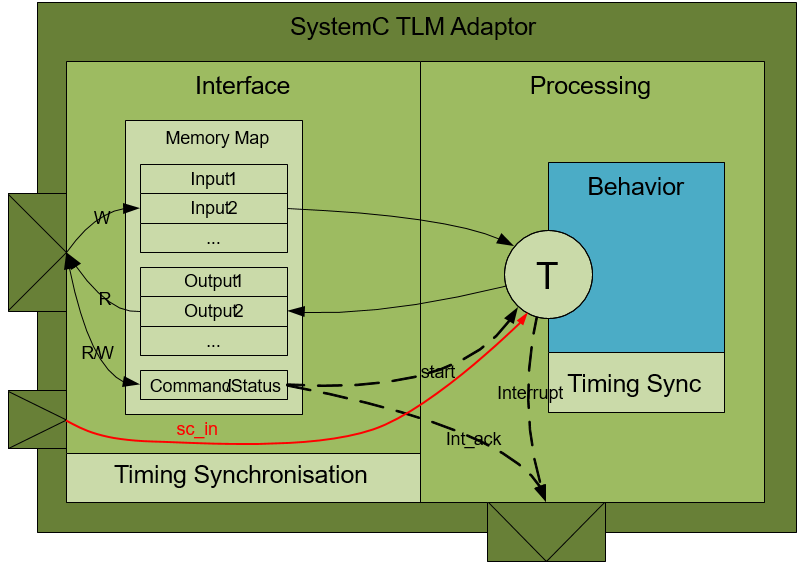

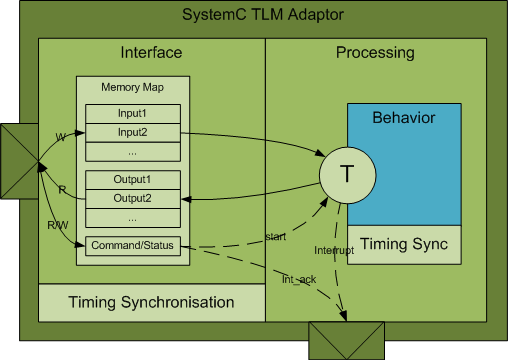

生成された TLM コンポーネントのアーキテクチャを制御するには、いくつかのオプションから選択できます。メモリ マップを組み込むことは、最も効果的なオプションの 1 つです。次の図は、すべての機能が有効になっている生成された TLM コンポーネントの動作を示しています。

次の TLM コンポーネント機能のオプションを設定できます。

インターフェース タイミング — 実際のシステムでトランザクションによって使用される時間をモデル化します。

アルゴリズムの実行 - コンポーネントを SystemC™ スレッドまたはコールバック関数として実装します。

メモリ マッピング

メモリマップなし

メモリ マップなしオプションでは、アドレスのない読み取りレジスタ 1 つと書き込みレジスタ 1 つだけを持つ TLM コンポーネントが生成されます。Simulink モデルの入力は書き込みレジスタで表され、出力は読み取りレジスタで表されます。

メモリ マップがない場合、生成された TLM コンポーネントには次の特性があります。

1 つの入力レジスタと 1 つの出力レジスタがあります。

デバイス上の特定のレジスタを選択するために、SystemC シミュレーション中に読み取りおよび書き込み要求でアドレスを必要とせず、無視します。

1回の書き込み要求ですべての入力データを受け取り、読み取り要求では戻り値ですべての出力データを受け取ります。

仮想プラットフォーム環境で動作(アルゴリズムのステップ関数)を実行するときにTLMコンポーネントによって必要なデータセット全体を保持するか、作成される入力レジスタと出力レジスタがあります。

入力レジスタがいっぱいになると、この条件により SystemC シミュレータでの動作の実行がトリガー (スケジュール) されます。出力レジスタも同様に処理されます。

コマンドとステータスのすべてのデフォルトが適用されます。

このオプションを使用して TLM コンポーネントを生成すると、仮想プラットフォーム (VP) で次のように使用できます。

検証テストベンチのスタンドアロンコンポーネント

直接結合されたコプロセッシングユニット

プロトコルアダプタを使用して通信チャネルに接続されたデバイス

単一アドレスのメモリマップを自動生成

単一アドレス オプションを使用して自動的に生成されるメモリ マップは、それぞれ 1 つのアドレスを持つ 1 つの読み取りデータ レジスタと 1 つの書き込みデータ レジスタのみを持つ TLM コンポーネントを生成します。

Simulink モデルの入力は書き込みレジスタで表され、出力は読み取りレジスタで表されます。HDL Verifier™ ソフトウェアは、コード生成中にこれらの特定のレジスタにアクセスするために必要なアドレスを自動的に割り当てます。これらのアドレスは、読み取りおよび書き込み操作を通じて各レジスタをアドレス指定するために必要な特定のオフセットを提供します。生成された TLM コンポーネント全体のベース アドレスの定義は、TLM コンポーネントが存在する仮想プラットフォームによって定義される必要があります。オフセット アドレス定義は、TLM コンポーネントとともに生成される定義ファイルに表示されます。

単一アドレス メモリ マップでは、生成された TLM コンポーネントには次の特性があります。

1 つの入力レジスタと 1 つの出力レジスタ、およびオプションのコマンドおよびステータス レジスタとテストおよびセット レジスタがあります。

デバイス上の特定のレジスタを選択するには、SystemC シミュレーション中に読み取りおよび書き込み要求にアドレスを指定する必要があります。

1回の書き込み要求ですべての入力データを受け取り、読み取り要求では戻り値ですべての出力データを受け取ります。

仮想プラットフォーム環境で動作(アルゴリズムのステップ関数)を実行するときにTLMコンポーネントによって必要なデータセット全体を保持するか、作成される入力レジスタと出力レジスタがあります。

コマンドおよびステータス レジスタが使用されていない場合、またはコマンドおよびステータス レジスタが使用され、デフォルト値が適用されている場合、入力レジスタがいっぱいになると、コンテンツがバッファーにプッシュされ、SystemC シミュレータでの動作の実行がトリガー (スケジュール) されます。コマンドとステータス レジスタが使用され、プッシュ入力コマンドが 1 に設定されている場合、イニシエーター モジュールは入力データ セットを入力レジスタから入力バッファーに移動します。出力レジスタも同様に処理されます。

コマンドおよびステータス レジスタが使用されていない場合は、コマンドおよびステータスのすべてのデフォルトが適用されます。

このオプションを使用して TLM コンポーネントを生成すると、テストベンチ内のスタンドアロン コンポーネントとして仮想プラットフォーム (VP) で使用したり、通信チャネルに接続したりできます。

個別のアドレスを持つメモリマップを自動生成

個別のアドレス オプションを使用して自動的に生成されたメモリ マップは、個別のアドレスを持つモデル出力ごとに 1 つの読み取りデータ レジスタとモデル入力ごとに 1 つの書き込みデータ レジスタを持つ TLM コンポーネントを生成します。

各 Simulink モデル入力は対応する書き込みレジスタによって表され、各出力は対応する読み取りレジスタによって表されます。HDL Verifier ソフトウェアは、コード生成中にこれらの特定のレジスタにアクセスするために必要なアドレスを自動的に割り当てます。これらのアドレスは、読み取りおよび書き込み操作を通じて各レジスタをアドレス指定するために必要な特定のオフセットを提供します。生成された TLM コンポーネント全体のベース アドレスの定義は、TLM コンポーネントが存在する仮想プラットフォームによって定義される必要があります。オフセット アドレス定義は、TLM コンポーネントとともに生成される定義ファイルに表示されます。

個別のアドレス メモリ マップでは、生成された TLM コンポーネントには次の特性があります。

各入力レジスタと各出力レジスタには独自のアドレスがあり、オプションのコマンドおよびステータス レジスタとテストおよびセット レジスタもあります。

デバイス上の特定のレジスタを選択するには、SystemC シミュレーション中に読み取りおよび書き込み要求にアドレスを指定する必要があります。

各入力レジスタと出力レジスタには個別にアクセスする必要があります。

イニシエーター モジュールは、複数のトランザクションや部分的なトランザクションで各入力レジスタと出力レジスタに書き込みまたは読み取りを行うことができます。

各入力レジスタと出力レジスタのサイズはデータのサイズです。

すべての入力が書き込まれたとき、またはコマンドとセット レジスタ ビットが自動に設定されたときに実行がトリガーされます。手動に設定されている場合、イニシエーター モジュールは入力データ セットを入力レジスタから入力バッファーに移動します。

出力レジスタは、すべての出力レジスタが読み取られたとき、またはコマンドおよび設定レジスタ ビットが自動に設定されたときに更新されます。手動に設定されている場合、イニシエーター モジュールは出力データ セットを出力バッファーから出力レジスタに移動します。

このオプションを使用して TLM コンポーネントを生成すると、テストベンチ内のスタンドアロン コンポーネントとして仮想プラットフォーム (VP) で使用したり、通信チャネルに接続したりできます。

コマンドおよびステータスレジスタ

アドレス付きのメモリ マップを自動的に生成して TLM コンポーネントを生成することもできます。これを実行すると、TLM ジェネレーターは、生成された TLM コンポーネントにコマンドおよびステータス レジスタ (CSR) を組み込むオプションを提供します。このレジスタの定義は表に表示されます。

書き込み専用ビット

書き込み専用 (WO) ビットは相互に排他的なコマンドをアサートします。CSR への単一の書き込み操作では、1 つのコマンド ビットのみをアサートできます。CSR への書き込みで複数のコマンド ビットが設定されている場合、コマンドは未定義になります。レジスタ内のコマンド ビットに 1 を書き込むことで、各コマンドをアクティブにします。その後、コマンドが実行されると、各コマンド ビットは自動的にクリアされます。コマンド ビットをクリアするためにレジスタに 0 を書き込む必要はありません。書き込み専用ビットは、CSR の読み取りでは常に 0 として返されます。コマンドを書き込むと、読み取り/書き込みビットまたは書き込み専用ビットは上書きされません。

読み書きビット

読み取りおよび書き込み (R/W) ビットを使用して、現在のステータスと設定を取得します。R/W ビットは スティッキー です。つまり、レジスタ内のビットに 1 を書き込んで設定した後は、同じビットに 0 が書き込まれるか、リセット コマンドが呼び出されるまで、R/W ビットは設定されたままになります。読み取り/書き込みビットは、CSR の読み取り時に実際の値を返します。

CSR への単一の書き込み操作により、レジスタ内のすべての読み取りおよび書き込みビットが設定されます。一部のビットのみを設定し、他のビットの以前の値を維持することを選択できます。これを実行する前に、まず CSR を読み、要件に応じて値を変更する必要があります。変更が完了したら、32 ビット全体を CSR に書き戻すことができます。

読み取り専用ビット

読み取り専用 (RO) ビットはステータス情報を提供します。生成された TLM コンポーネントは値を自動的に設定およびクリアし、イニシエーター モジュールはそれらを読み取ってステータスを確認できます。読み取り専用ビットは、CSR の読み取りまたは書き込み中に実際の値を変更しません。

レジスタの定義

次の表にはレジスタの定義全体が記載されています。

次の表は、ビットの定義方法を説明しています。

| ビット | 名前 | 読み取り/書き込みステータス | 説明 |

|---|---|---|---|

| CSR<0> | リセットコマンド | 書き込み専用 | 1 に設定すると、次のようになります。

コマンド実行後、自動的に 0 に戻ります。 |

| CSR<1> | コマンドの開始 | 書き込み専用 | 入力バッファリングがない場合、現在入力レジスタにある入力データ セットを使用して、TLM コンポーネント動作の実行を手動でトリガーします。 入力バッファリングが使用される場合、このコマンドは未定義になります。 |

| CSR<2> | 割り込みステータス | 読み取り専用 | 割り込み信号の現在の状態を反映します。ステータスのみを提供します。自動的に設定およびクリアされます。 |

| CSR<3> | 割り込み無効化 | 読み書き | 0 に設定すると、割り込み信号で割り込みが生成され、CSR の割り込みステータス ビットに反映されます。 1 に設定すると、割り込みの生成が無効になります。 |

| CSR<8> | プッシュ入力コマンド | 書き込み専用 | バッファリングが使用され、入力モードが 0 (手動モード) の場合、このコマンドにより、イニシエーター モジュールは入力データ セットを入力レジスタから入力バッファに移動できます。次に、TLM コンポーネントの動作の実行をトリガーします。 バッファリングが使用されていない場合、このコマンドは未定義になります。 入力モードが 1 (自動) の場合、このコマンドは未定義になります。 |

| CSR<9> | 入力モード | 読み書き | 1 (自動) に設定すると、入力レジスタに完全なデータ セットが書き込まれている場合、入力データ セットが入力レジスタから入力バッファに移動され、TLM コンポーネントの動作が自動的に実行されます。 0 (手動) に設定すると、入力レジスタから入力バッファへの入力データ セットの移動と動作の実行は手動で開始する必要があります。バッファリングを使用しない場合は、スタート コマンド ビットに 1 を書き込むか、バッファリングが存在する場合は、プッシュ入力コマンドに 1 を書き込むことによってこれを実行します。 デフォルトでは、入力モードは 1 (自動) に設定されています。0 (手動) に変更するには、TLM コンポーネント コンストラクター パラメーターで指定します。 |

| CSR<12> | プル出力コマンド | 書き込み専用 | バッファリングが使用され、出力モードが 0 (手動モード) に設定されている場合、このコマンドにより、イニシエーター モジュールは出力データ セットを出力バッファの先頭から出力レジスタに移動できます。 バッファリングが使用されていない場合、このコマンドは効果がありません。 出力モードが 1 (自動) の場合、このコマンドは未定義になります。 |

| CSR<13> | 出力モード | 読み書き | 1 (自動) に設定すると、TLM コンポーネント動作の実行によって、出力バッファの先頭から出力レジスタへのデータの移動が自動的にトリガーされます。 0 (手動) に設定すると、出力バッファの先頭から出力レジスタへのデータの移動を手動で開始する必要があります。バッファリングが存在する場合は、プル出力コマンドを 1 に書き込むことによってこれを実行します。 デフォルトでは、出力モードは 1 (自動) に設定されています。0 (手動) に変更するには、TLM コンポーネント コンストラクター パラメーターで指定します。 |

割り込み

生成された TLM コンポーネントに割り込み信号を追加できます。TLM コンポーネントは、出力レジスタで新しい出力が利用可能になるたびにこの信号をアサートします。出力レジスタから値が読み取られるたびに、信号は自動的にクリアされます。

割り込み信号は、アクティブハイの SystemC ブール信号です。ステータス レジスタの割り込みアクティブ ビットは、割り込み信号の状態を反映します。

テストとレジスタの設定

オプションのテストおよびセット レジスタを使用して、SystemC 環境内の共有 TLM コンポーネントへのアクセスを制御できます。このレジスタを読み取ると、現在の値が返され、アトミック操作でレジスタが新しいアサートされた値に設定されます。複数のイニシエーター モジュールを備えたシステムでは、通常、このタスクを実行するには同じターゲットにアクセスする必要があります。その場合、他のすべてのイニシエーター モジュールがそれに従う限り、イニシエーター モジュールは生成された TLM コンポーネントに排他的にアクセスできます。イニシエーター モジュールは、テストおよびセット レジスタを読み取り、その読み取り操作で値 0 が返される場合にのみターゲット デバイスを使用する必要があります。イニシエーター モジュールは、テストおよびセット レジスタのその後の読み取りで値 1 が返され、デバイスがビジー状態であることを他のイニシエーター モジュールに通知することを確認できます。イニシエーター モジュールは、TLM コンポーネントへの排他的アクセスを取得した後、ターゲット操作が完了すると、テストおよびセット レジスタに 0 を書き込んでコンポーネントを解放します。

レジスタと信号ポート

レジスタ

TLM コンポーネントは、アルゴリズム処理中にインターフェイス レジスタから直接入力と出力を読み取り、書き込みます。イニシエーターがすべての入力レジスタに書き込んだ後 (AUTO モードの場合)、またはイニシエーターが CSR に START コマンドを書き込んだ後、アルゴリズムが処理を開始します。SystemC 待機関数がすべてのタイミングを生成します。

注意

アルゴリズム処理結果の破損を防ぐために、処理中にイニシエーターがレジスタの読み取りまたは書き込みを実行できないようにします。

この図は、登録されたインターフェースを持つ TLM アダプタを示しています。

信号ポート

TLM コンポーネントは、sc_signal ポート (sc_in または sc_out) を介して入力と出力の読み取りと書き込みを行います。これらの入力/出力は登録されていません。ステップ関数が実行されると、sc_in ポートの現在の値が読み取られ、実行されて結果が sc_out ポートに書き込まれます。

この図は、レジスタ インターフェイスと sc_in ポート (赤) を備えた TLM アダプタを示しています。