階層的なモデル化に関するガイドライン

モデルを階層的にビルドして設計の HDL コードを生成する場合は、これらの推奨設定を使用することを検討してください。各ガイドラインに準拠要件のレベルを示す重大度レベルが割り当てられています。詳細については、HDL モデリング ガイドラインの重大度レベルを参照してください。

サブシステム端子の境界に Constant ブロックを接続しない

ガイドライン ID

1.2.4

重大度

必須

説明

Constant ブロックはサブシステムの出力端子に直接接続しないことをお勧めします。合成ツールによる最適化で、定数が削除されて未接続の端子が作成されることがあります。

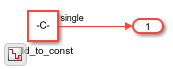

Native Floating Point モードを有効にして浮動小数点データ型を使用している場合に、Add ブロックなどの算術演算に定数値を入力すると、HDL Coder™ でのコード生成時に Add ブロックが Constant ブロックに置き換えられます。この最適化により、Constant ブロックが出力端子に直接接続されることがあります。そのため、このようなモデル構造は避けることをお勧めします。HDL Coder での定数演算の簡略化と設計の複雑度の低減も参照してください。

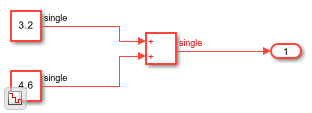

たとえば、モデル hdlcoder_constant_subsystem_boundary.slx を開きます。DUT に Constant_subsys1 と Constant_subsys2 の 2 つのサブシステムが含まれています。これらのサブシステムの出力は 3 つ目のサブシステムの入力になります。Constant_subsys1 には出力端子に直接接続された Constant ブロックが含まれており、Constant_subsys2 には Add ブロックへの入力となる single データ型の Constant ブロックが含まれています。

load_system('hdlcoder_constant_subsystem_boundary.slx') set_param('hdlcoder_constant_subsystem_boundary','SimulationCommand','Update') open_system('hdlcoder_constant_subsystem_boundary/DUT/Constant_subsys1')

open_system('hdlcoder_constant_subsystem_boundary/DUT/Constant_subsys2')

Constant_subsys2 で single データ型が使用されており、モデルで Native Floating Point モードが有効になっているため、この DUT の HDL コードを生成すると、Constant_subsys2 は定数演算を簡略化する最適化の候補になります。生成されたモデルを開いて確認すると、Constant ブロックが出力端子に直接接続されていることがわかります。

open_system('gm_hdlcoder_constant_subsystem_boundary.slx') set_param('gm_hdlcoder_constant_subsystem_boundary','SimulationCommand','Update') open_system('gm_hdlcoder_constant_subsystem_boundary/DUT/Constant_subsys2')

Constant ブロックと Gain ブロックのパラメーター化された HDL コードの生成

ガイドライン ID

1.2.5

重大度

推奨

説明

Constant ブロックと Gain ブロックのパラメーター化された HDL コードを生成するには以下に従います。

Constant ブロックと Gain ブロックを含むサブシステムはマスク サブシステムでなければなりません。それらのマスク パラメーターの値を Constant ブロックと Gain ブロックで使用します。サブシステムのマスク パラメーターは [マスク エディター] ダイアログ ボックスで定義します。

Gain ブロックと Constant ブロックを含むサブシステムは Atomic サブシステムでなければなりません。サブシステムを Atomic サブシステムにするには、そのサブシステムを右クリックして [Atomic サブシステムとして扱う] を選択します。

[コンフィギュレーション パラメーター] ダイアログ ボックスで [マスクされたサブシステムからのパラメーター化された HDL コードの生成] 設定を有効にするか、コマンド ラインで

makehdlまたはhdlset_paramを使用してMaskParameterAsGenericをonに設定します。詳細については、Generate parameterized HDL code from masked subsystemを参照してください。

たとえば、モデル hdlcoder_masked_subsystems を開きます。Top サブシステムに MASKSUB と MASKSUB1 の 2 つの Atomic マスク サブシステムが含まれています。これらは似ていますがマスク パラメーターの値が異なります。

load_system('hdlcoder_masked_subsystems') set_param('hdlcoder_masked_subsystems', 'SimulationCommand', 'Update') open_system('hdlcoder_masked_subsystems/TOP')

このモデルでは MaskParameterAsGeneric 設定が有効になっています。これは [マスクされたサブシステムからのパラメーター化された HDL コードの生成] 設定に対応する設定で、コマンド ラインで有効にしたものです。

hdlsaveparams('hdlcoder_masked_subsystems')

%% Set Model 'hdlcoder_masked_subsystems' HDL parameters

hdlset_param('hdlcoder_masked_subsystems', 'HDLSubsystem', 'hdlcoder_masked_subsystems/TOP');

hdlset_param('hdlcoder_masked_subsystems', 'MaskParameterAsGeneric', 'on');

Top サブシステムの VHDL® コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_masked_subsystems/TOP')

生成されたコードを確認すると、汎用の端子に異なるマスク パラメーターがマッピングされた 1 つの HDL ファイル MaskedSub が HDL Coder™ で生成されていることがわかります。

-- -------------------------------------------------------------

--

-- File Name: hdlsrc\hdlcoder_masked_subsystems\TOP.vhd

-- Created: 2018-10-08 13:30:02

--

-- Generated by MATLAB 9.6 and HDL Coder 3.13

--

--

-- -------------------------------------------------------------

--

--

ARCHITECTURE rtl OF TOP IS

-- Component Declarations

COMPONENT MASKSUB

GENERIC( m : integer;

b : integer

);

PORT( x : IN std_logic_vector(7 DOWNTO 0); -- uint8

y : OUT std_logic_vector(16 DOWNTO 0) -- ufix17

);

END COMPONENT;

-- Component Configuration Statements

FOR ALL : MASKSUB

USE ENTITY work.MASKSUB(rtl);

-- Signals

SIGNAL MASKSUB_out1 : std_logic_vector(16 DOWNTO 0); -- ufix17

SIGNAL MASKSUB1_out1 : std_logic_vector(16 DOWNTO 0); -- ufix17

BEGIN

u_MASKSUB : MASKSUB

GENERIC MAP( m => 5,

b => 2

)

PORT MAP( x => In1, -- uint8

y => MASKSUB_out1 -- ufix17

);

u_MASKSUB1 : MASKSUB

GENERIC MAP( m => 6,

b => 4

)

PORT MAP( x => In1, -- uint8

y => MASKSUB1_out1 -- ufix17

);

Out1 <= MASKSUB_out1;

Out2 <= MASKSUB1_out1;

END rtl;

サブシステム内の物理量信号線の配置

ガイドライン ID

1.2.6

重大度

必須

説明

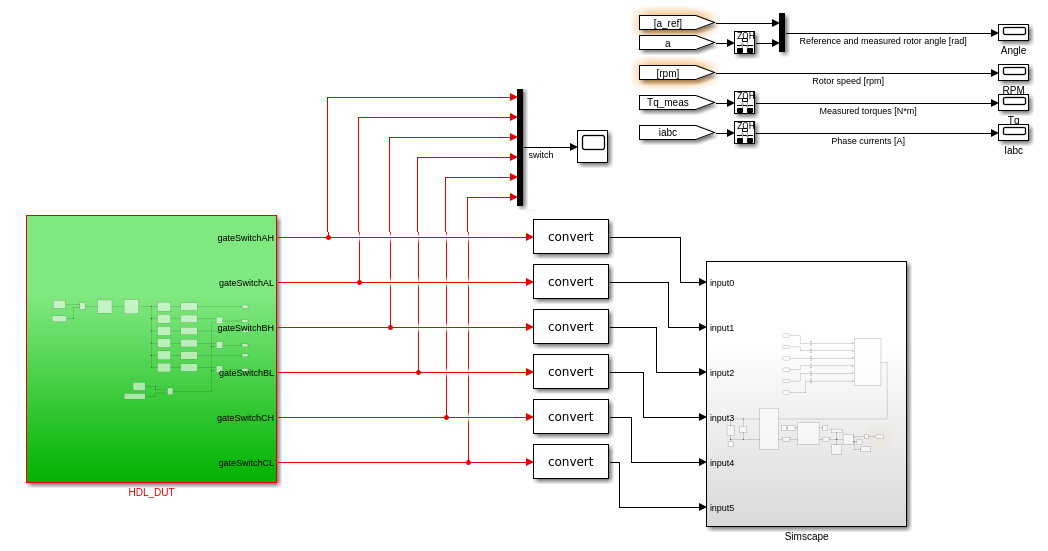

HDL テスト ベンチの生成時のエラーを回避するには、DUT サブシステムと同じレベルに存在する物理量信号線を Subsystem ブロック内に配置しなければなりません。たとえば、DUT サブシステム HDL_DUT の外側に物理量信号線をもつ、次の Simulink® モデルについて考えます。

物理量信号線と、これに接続するブロック (Subsystem ブロック内部で強調表示されている) を配置します。DUT サブシステムの HDL コードとテスト ベンチを生成できます。