HDL Coder での定数演算の簡略化と設計の複雑度の低減

HDL Coder™ は、生成された HDL コードの品質を向上させる特定の最適化手法を実行します。浮動小数点データ型を Native Floating Point モードで使用し、モデルからコードを生成するとき、コンパイル時に HDL Coder は特定のパターンに当てはまるブロックのサブセットを検索します。パターンを認識すると、コード ジェネレーターは特定の最適化手法を自動的に実行し、サブセットのブロックを別のよりシンプルなブロックに置き換えます。

最適化手法は、以下を行います。

冗長な実行時計算を除去

設計を簡素化

生成された HDL コードの品質と効率を向上

レイテンシと面積フットプリントを削減

ターゲット ハードウェア上の設計のタイミングを向上

定数演算の簡略化

HDL Coder は、定数の部分式を事前に評価することによって、設計に含まれる冗長な演算を除去します。この最適化手法は、モデルの中から、すべての入力端子が定数値を取る Simulink® ブロックを特定し、そのブロックを Constant ブロックに置き換えます。コード ジェネレーターは、ブロック内のその入力定数を伝播し、得られた定数値を計算します。たとえば、c = 3 * 5 は c = 15 になります。

この最適化は、HDL コード生成をサポートするあらゆる Simulink ブロックで動作します。以下に例を示します。

モデル

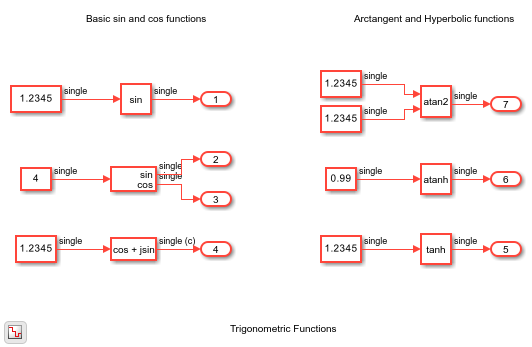

hdlcoder_constant_simplificationを開きます。Trigonometric Functionsサブシステムをダブルクリックします。

open_system('hdlcoder_constant_simplification') open_system('hdlcoder_constant_simplification/Trigonometric Functions') set_param('hdlcoder_constant_simplification', 'SimulationCommand', 'update');

hdlcoder_constant_simplificationモデルの HDL コードを生成するため、以下のコマンドを入力します。

makehdl('hdlcoder_constant_simplification')

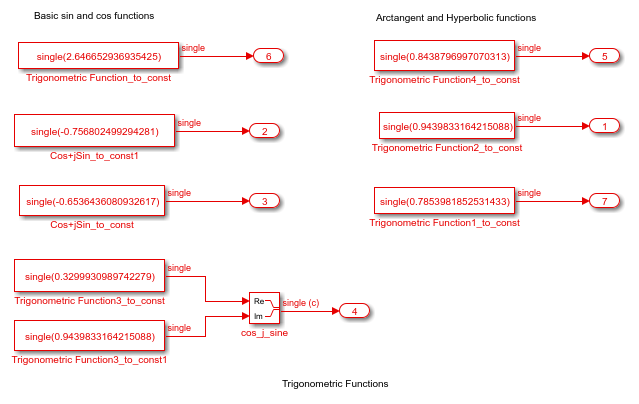

生成されたモデルを開き、

Trigonometric Functionsサブシステムをダブルクリックします。

HDL Coder がモデリング パターンを認識し、定数の単精度三角関数演算を定数に置き換えました。この最適化により、コードをターゲット プラットフォームに展開したときに、面積が大きく削減され、タイミングが向上します。

より高速な等価式での時間がかかる演算の置き換え

この最適化によって、時間がかかる演算がより高速な等価式に自動的に置き換えられます。たとえば、r1 = r2 / 2 は r1 = r2 >> 1 になります。

この最適化手法の例には、Product ブロックまたは Divide ブロックを Gain ブロックに置き換えることが含まれます。Product ブロックまたは Divide ブロックへの入力の 1 つが定数で、かつ 2 のべき乗である場合、コード ジェネレーターはそのブロックを Gain ブロックに置き換えます。コード ジェネレーターは、Product ブロックまたは Divide ブロック内の定数値を伝播し、Gain パラメーターを計算します。この最適化は、Native Floating Point モードの single データ型で動作します。

以下に例を示します。

モデル

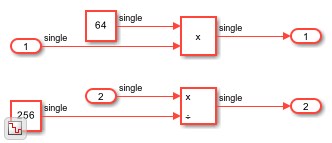

hdlcoder_slow_operation_replacementを開きます。DUT サブシステムをダブルクリックします。

open_system('hdlcoder_slow_operation_replacement') open_system('hdlcoder_slow_operation_replacement/DUT') set_param('hdlcoder_slow_operation_replacement', 'SimulationCommand', 'update');

DUT サブシステムの HDL コードを生成するため、以下のコマンドを入力します。

makehdl('hdlcoder_slow_operation_replacement/DUT')

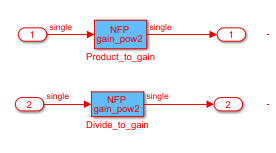

生成されたモデルを開き、

DUTサブシステムをダブルクリックします。

HDL Coder は、モデリング パターンを認識し、Product ブロックと Divide ブロックを Gain ブロックに置き換えました。この最適化により、設計のレイテンシが大きく削減され、ターゲット FPGA での面積とタイミングが改善されます。

複数の演算の結合

この最適化により、いくつかの演算が 1 つの等価な演算に置き換えられます。この最適化手法の例としては、Sin ブロックと Cos ブロックの 1 つの Sincos ブロックへの置き換えなどがあります。モデル内の Sin ブロックと Cos ブロックに同じ入力信号を提供し、Sin ブロックと Cos ブロックの HDL ブロック プロパティが一致する場合、コード ジェネレーターはこれらのブロックを 1 つの Sincos ブロックに置き換えます。この最適化は、Native Floating Point モードの single データ型で動作します。

以下に例を示します。

モデル

hdlcoder_combine_operationsを開きます。DUT サブシステムをダブルクリックします。

open_system('hdlcoder_combine_operations') open_system('hdlcoder_combine_operations/DUT') set_param('hdlcoder_combine_operations', 'SimulationCommand', 'update');

DUT サブシステムの HDL コードを生成するため、以下のコマンドを入力します。

makehdl('hdlcoder_combine_operations/DUT')

生成されたモデルを開き、DUT サブシステムをダブルクリックします。以下のように、生成されたモデルが表示されます。

HDL Coder は、モデリング パターンを認識し、Sin ブロックと Cos ブロックを 1 つの Sincos ブロックに置き換えました。この最適化手法は、ターゲット プラットフォームにおける設計のパフォーマンスを大きく向上します。

考慮事項

最適化は浮動小数点データ型で動作します。固定小数点設計はこの最適化の影響を受けません。single データ型を使用するときは、

Native Floating Pointモードを有効にします。[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成]、[浮動小数点] ペインで、[浮動小数点の使用] を選択します。HDL Coder におけるネイティブ浮動小数点のサポートの詳細については、ネイティブ浮動小数点を使用したターゲットに依存しない HDL コードの生成を参照してください。最適化は、生成されたコードに含まれるブロックのすべてのコメントを保持します。ブロックへのコメント指定の詳細については、注釈またはコメント付きの HDL コードの生成を参照してください。

調整可能なパラメーターは定数値として扱われないため、最適化は、調整可能なパラメーターまたは汎用的入力を使用するブロックを最適化しません。これらのブロックを最適化に含めるには、ブロックのマスク エディターで、[調整可能] チェック ボックスをオフにします。調整可能なパラメーターについては、調整可能なパラメーターの DUT 端子を生成するを参照してください。

最適化は、ワークスペース ブラウザーの列挙値と定数を、定数値として扱います。したがって、コード ジェネレーターは、さまざまなコンポーネント内でこれらの値を伝播し、定数演算を簡略化します。