生成された HDL コードの冗長なロジックと未使用ブロックの削除

設計に冗長なロジックまたは未使用ブロックが含まれている場合、HDL Coder™ はそのブロック、コンポーネント、または出力に影響しない HDL コードの一部を削除します。

冗長なロジックの考慮事項

設計で出力に影響しないコンポーネントが HDL コードの生成中に削除されます。冗長なロジックを削除することでコード サイズが縮小され、コードをターゲット プラットフォームに展開するときに下流のツールで合成が失敗する可能性が回避されます。HDL コード生成中にコンポーネントまたはロジックが保持されると、そのコンポーネントまたはロジックは "アクティブ" であると見なされます。この最適化により、ターゲット ハードウェアにおける設計のパフォーマンスが向上します。最適化は、トレーサビリティ サポートに影響しません。

設計内の冗長なロジックは、未使用の端子の削除の最適化と共に削除されます。この最適化の詳細については、Simulink モデルの HDL コードでの未接続の端子の最適化を参照してください。

次の場合、HDL Coder はコンポーネントまたはロジックを冗長として扱いません。

DUT 出力の評価に影響する出力端子が、コンポーネントに少なくとも 1 つ含まれている。

アクティブな Subsystem ブロックの制御端子の評価に影響する出力端子が、コンポーネントに少なくとも 1 つ含まれている。

HDL コード生成中に保持されるコンポーネントの入力の評価に影響する出力端子が、コンポーネントに少なくとも 1 つ含まれている。

後述のように、コンポーネントがアクティブなブラック ボックス サブシステムである、コンポーネントにアクティブなブラック ボックス サブシステムが含まれている、またはコンポーネントがアクティブなブラック ボックス サブシステムに接続している。

コンポーネントは FPGA Data Capture ブロックである。

その他の場合、コード ジェネレーターはロジックを冗長として扱い、関連するブロックまたはコンポーネントをコード生成中に削除します。さらに、Scope ブロック、Assertion ブロック、Terminator ブロック、および To Workspace ブロックなどの、HDL アーキテクチャが [No HDL] に設定されているブロックは冗長と見なされ、コード生成中に削除されます。

冗長なロジックの削除が動作する仕組み

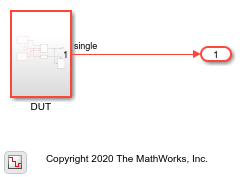

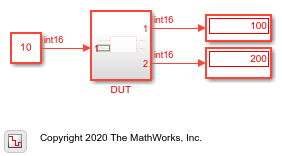

コード生成中、HDL Coder は DUT 出力に影響しない冗長なロジックまたは冗長なブロックを削除します。モデル hdlcoder_remove_redundant_logic を開きます。

open_system('hdlcoder_remove_redundant_logic') set_param('hdlcoder_remove_redundant_logic', 'SimulationCommand', 'update');

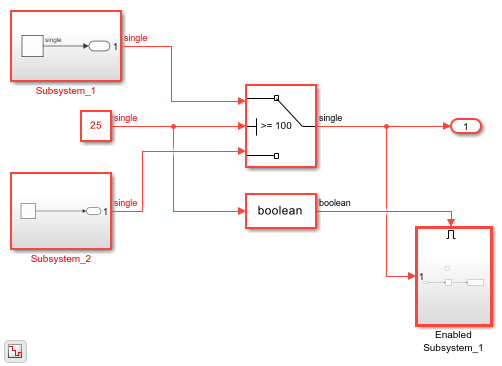

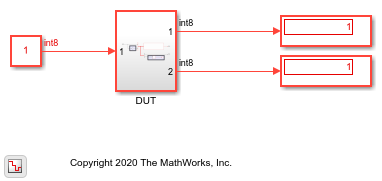

DUT サブシステム ブロックには、Switch ブロックと Enabled Subsystem ブロックが含まれます。Switch ブロックの制御入力に基づいて、Subsystem_2 からの false パスは出力に渡されます。EnabledSubsystem_1 ブロックの出力は Display ブロックで終端し、出力に積極的に影響することはありません。

open_system('hdlcoder_remove_redundant_logic/DUT')

設計の HDL コードを生成するには、MATLAB® コマンド プロンプトで次のように入力します。

makehdl('hdlcoder_remove_redundant_logic/DUT')

生成された VHDL® コードは、HDL Coder がコンパイル時に Switch ブロック条件を評価して、Subsystem_2 からの入力を出力に渡し、Subsystem_1 入力分岐を除去したことを示します。EnabledSubsystem_1 ブロックが HDL コード生成中に削除されるのは、このブロックにはアクティブな出力がないためです。

ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT Subsystem_2 PORT( Out1 : OUT std_logic_vector(31 DOWNTO 0) -- single ); END COMPONENT;

-- Component Configuration Statements FOR ALL : Subsystem_2 USE ENTITY work.Subsystem_2(rtl);

-- Signals SIGNAL Subsystem_2_out1 : std_logic_vector(31 DOWNTO 0); -- ufix32

BEGIN

u_Subsystem_2 : Subsystem_2

PORT MAP( Out1 => Subsystem_2_out1 -- single

);Out1 <= Subsystem_2_out1;

END rtl;

ブラック ボックス サブシステムでの冗長なロジック

ブラック ボックス サブシステムは、HDL アーキテクチャが [BlackBox] に設定されているサブシステム ブロックです。サブシステムのブラック ボックス インターフェイスは、生成された VHDL コンポーネントまたは Verilog® モジュールまたは SystemVerilog モジュールです。これらには、サブシステム用に HDL の入力および出力端子の定義のみが含まれています。生成されたインターフェイスを使用して、既存の手書きの HDL コード、サードパーティ製の IP または HDL Coder で生成された他のコードを統合します。サブシステムのブラック ボックス インターフェイスの生成を参照してください。

少なくとも 1 つの入力端子をもつブラック ボックス サブシステムは、HDL コード生成中にアクティブであると見なされ、保持されます。入力端子は、未接続でもかまいません。この場合、Simulink® は、ブロックへの入力が定数値 0 のバーチャル信号を挿入します。出力ポートの場合は、ブラック ボックス サブシステムには下流のブロックに接続している出力端子が少なくとも 1 つなければなりません。出力端子が接続している場合、コード ジェネレーターは、ブラック ボックス サブシステムを出力値の消費に影響するソースとして識別し、それをコード生成中に保持します。

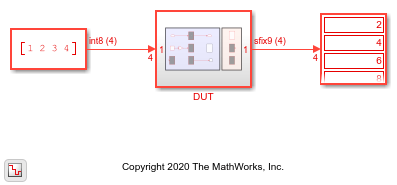

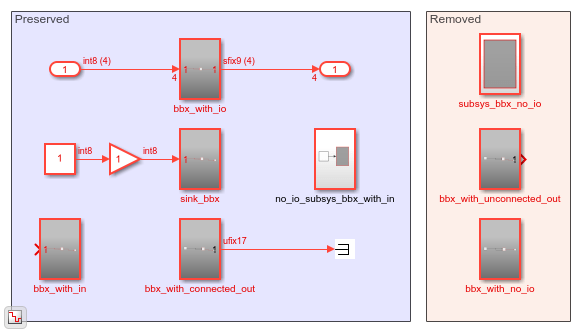

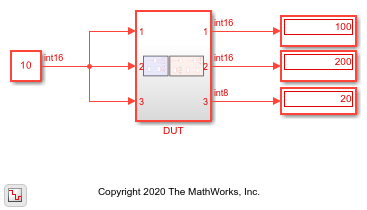

モデル hdlcoder_blackbox_redundant_logic を開きます。

open_system('hdlcoder_blackbox_redundant_logic') sim('hdlcoder_blackbox_redundant_logic');

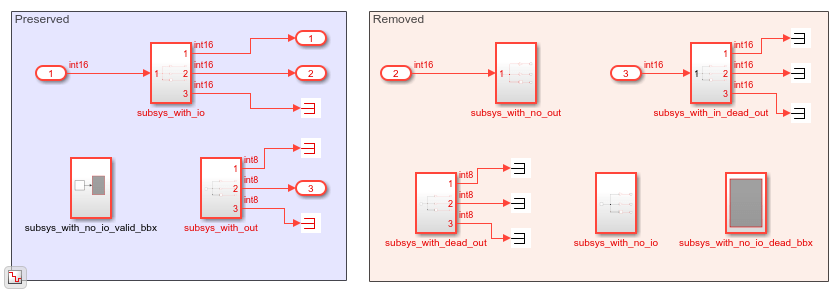

DUT サブシステムの Preserved と Removed というラベルが付いたボックス内にブラック ボックス サブシステムが含まれます。Preserved 内のブラック ボックス サブシステムは、入力端子を少なくとも 1 つもつため、コード生成中に削除されません。入力端子がないか、出力端子が接続されていない、その他のブラック ボックス サブシステムは、コード生成中に削除されます。

open_system('hdlcoder_blackbox_redundant_logic/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_blackbox_redundant_logic/DUT')

生成された HDL コードでは、サブシステムは Preserved セクションに示されます。未接続の入力端子は自動的に定数 0 に接続します。

ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT bbx_with_io PORT( clk : IN std_logic; clk_enable : IN std_logic; reset : IN std_logic; In1 : IN vector_of_std_logic_vector8(0 TO 3); -- int8 [4] Out1 : OUT vector_of_std_logic_vector9(0 TO 3) -- sfix9 [4] ); END COMPONENT;

COMPONENT no_io_subsys_bbx_with_in PORT( clk : IN std_logic; reset : IN std_logic; enb : IN std_logic ); END COMPONENT;

COMPONENT bbx_with_in PORT( clk : IN std_logic; clk_enable : IN std_logic; reset : IN std_logic; In1 : IN std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

COMPONENT sink_bbx PORT( clk : IN std_logic; clk_enable : IN std_logic; reset : IN std_logic; In1 : IN std_logic_vector(7 DOWNTO 0) -- int8 ); END COMPONENT;

COMPONENT bbx_with_connected_out PORT( clk : IN std_logic; clk_enable : IN std_logic; reset : IN std_logic; Output : OUT std_logic_vector(16 DOWNTO 0) -- ufix17 ); END COMPONENT;

...

END rtl;

Subsystem ブロックの冗長なロジック

Subsystem ブロックに DUT 出力の評価に影響する出力端子が少なくとも 1 つある場合、そのブロックは生成された HDL コードで保持されます。また、Subsystem ブロックは、有効なブラック ボックス サブシステムを含む場合にも保持されます。上記のように、ブラック ボックス サブシステムは、これに入力端子が含まれている場合、または出力端子が接続している場合は有効です。

さまざまな種類の Subsystem ブロックは、この規則に従います。

Subsystem

Atomic Subsystem

モデル参照

Variant Subsystem

ForEach Subsystem

Triggered Subsystem

Enabled Subsystem

Synchronous Subsystem

マスク サブシステム

個々のサブシステムの端子では、[コンフィギュレーション パラメーター] ダイアログ ボックスの未使用の端子を削除の設定を指定するかどうかによって、冗長なロジックの削除も異なります。

モデル hdlcoder_subsys_redundant_logic を開きます。

open_system('hdlcoder_subsys_redundant_logic') sim('hdlcoder_subsys_redundant_logic');

DUT サブシステムの Preserved と Removed というラベルが付いたボックス内にサブシステム ブロックが含まれます。Preserved 内のサブシステム ブロックは、DUT 出力の評価に影響する出力端子を少なくとも 1 つもつか、有効なブラック ボックス サブシステムをもつため、コード生成中に削除されません。アクティブな出力端子をもたない、その他のブラック ボックス サブシステムは、コード生成中に削除されます。

open_system('hdlcoder_subsys_redundant_logic/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_subsys_redundant_logic/DUT')

生成された HDL コードでは、サブシステムは Preserved セクションに示されます。

ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT subsys_with_io PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16 Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

COMPONENT subsys_with_out PORT( Out2 : OUT std_logic_vector(7 DOWNTO 0) -- int8 ); END COMPONENT;

COMPONENT subsys_with_no_io_valid_bbx PORT( clk : IN std_logic; reset : IN std_logic; enb : IN std_logic ); END COMPONENT;

...

END rtl;

サブシステムの端子の冗長なロジック

サブシステムのデータ端子の場合も、冗長なロジックの削除は [未使用の端子を削除] 設定を指定するかどうかによって決まります。Simulink モデルの HDL コードでの未接続の端子の最適化を参照してください。

制御端子は、[未使用の端子を削除] 設定の影響を受けません。制御端子と制御端子の評価に影響するコンポーネントは、サブシステムのインスタンス全体がアクティブであると見なされる場合にのみ生成された HDL コードで保持されます。

open_system('hdlcoder_control_redundant_logic') sim('hdlcoder_control_redundant_logic');

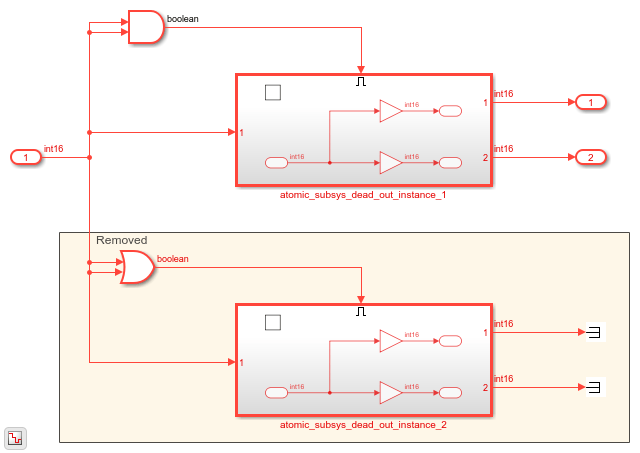

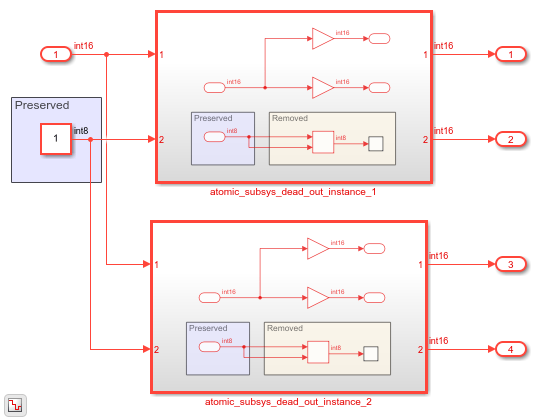

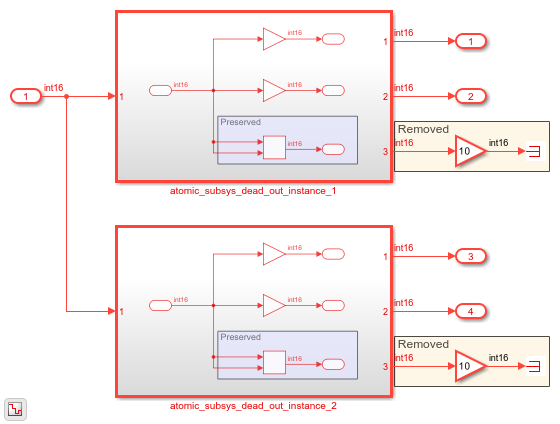

DUT サブシステムには、イネーブル端子を駆動する入力をもつ 2 つの Atomic サブシステムが含まれます。出力が終端処理されているため、サブシステム atomic_subsys_dead_out_instance_2 はアクティブではありません。

open_system('hdlcoder_control_redundant_logic/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_control_redundant_logic/DUT')

制御端子と入力信号を含む atomic_subsys_dead_out_instance_2 は、生成された HDL コードで削除されます。

ENTITY DUT IS

PORT( clk : IN std_logic;

reset : IN std_logic;

clk_enable : IN std_logic;

In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

ce_out : OUT std_logic;

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT atomic_subsys_dead_out_instance_1 PORT( clk : IN std_logic; reset : IN std_logic; enb : IN std_logic; In1 : IN std_logic_vector(15 DOWNTO 0); -- int16 Enable : IN std_logic; Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

...

END rtl;

Atomic サブシステムとモデル参照の冗長なロジック

Atomic サブシステム、モデル参照、および ForEach Subsystem ブロックの冗長なロジックは、HDL コード生成中と同様に処理されます。Atomic サブシステムの境界の冗長なロジックは、HDL コード生成中に削除されます。

モデル hdlcoder_atomic_subsys2_redundant を開きます。

open_system('hdlcoder_atomic_subsys2_redundant') sim('hdlcoder_atomic_subsys2_redundant');

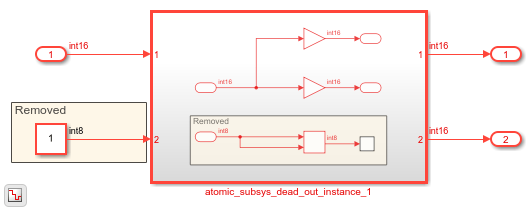

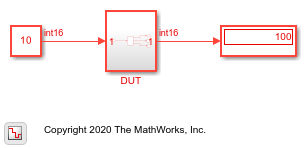

DUT サブシステムには、1 つの Atomic Subsystem ブロックが含まれます。Constant ブロックは、Terminator ブロックに接続している Add ブロックをもつサブシステムに対する入力です。

open_system('hdlcoder_atomic_subsys2_redundant/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_atomic_subsys2_redundant/DUT')

Add ブロックは DUT 出力端子の評価に影響しないため、HDL コードを生成すると Add ブロックと入力端子は削除されます。

ENTITY atomic_subsys_dead_out_instance_1 IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END atomic_subsys_dead_out_instance_1;ARCHITECTURE rtl OF atomic_subsys_dead_out_instance_1 IS

...

In1_signed <= signed(In1);

Gain_mul_temp <= to_signed(16#000A#, 16) * In1_signed; Gain_out1 <= Gain_mul_temp(15 DOWNTO 0);

Out1 <= std_logic_vector(Gain_out1);

Gain1_mul_temp <= to_signed(16#0014#, 16) * In1_signed; Gain1_out1 <= Gain1_mul_temp(15 DOWNTO 0);

Out2 <= std_logic_vector(Gain1_out1);

END rtl;

Atomic Subsystem ブロックのインスタンスが複数アクティブになっている場合、冗長なロジックの計算はサブシステム境界を超えず、ブロックは生成された HDL コードで保持されます。

モデル hdlcoder_atomic_subsys1_redundant を開きます。

open_system('hdlcoder_atomic_subsys1_redundant') sim('hdlcoder_atomic_subsys1_redundant');

DUT サブシステムには、2 つの Atomic サブシステムが含まれます。これらのサブシステムの中では、Add ブロックが Terminator ブロックに接続しています。

open_system('hdlcoder_atomic_subsys1_redundant/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_atomic_subsys1_redundant/DUT')

Add ブロックは DUT 出力端子の評価に影響しないため、Add ブロックは HDL コードを生成するときに削除されます。アクティブな Atomic サブシステムのインスタンスが 2 つ存在するため、Add ブロックへの入力端子は HDL コード生成中に保持されます。

Atomic サブシステムの HDL ファイル atomic_subsys_dead_out_instance_1 が 1 つ生成されます。このファイルには In2 端子宣言が含まれますが、HDL コードでは未使用です。DUT レベル DUT.vhd では、Constant ブロックは、Atomic Subsystem 内のコンポーネントを駆動しない入力端子に接続していますが保持されます。

ENTITY atomic_subsys_dead_out_instance_1 IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

In2 : IN std_logic_vector(7 DOWNTO 0); -- int8

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END atomic_subsys_dead_out_instance_1;ARCHITECTURE rtl OF atomic_subsys_dead_out_instance_1 IS

-- Signals SIGNAL In1_signed : signed(15 DOWNTO 0); -- int16 SIGNAL Gain_mul_temp : signed(31 DOWNTO 0); -- sfix32 SIGNAL Gain_out1 : signed(15 DOWNTO 0); -- int16 SIGNAL Gain1_mul_temp : signed(31 DOWNTO 0); -- sfix32 SIGNAL Gain1_out1 : signed(15 DOWNTO 0); -- int16

...

END rtl;

アクティブな Atomic Subsystem ブロックのインスタンスが複数ある場合、これらのインスタンスは生成されたコードで維持されます。

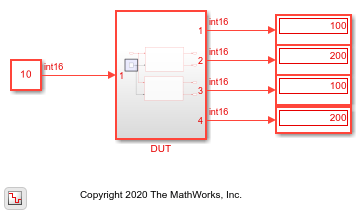

モデル hdlcoder_atomic_subsys1_ports_redundant を開きます。

open_system('hdlcoder_atomic_subsys1_ports_redundant') sim('hdlcoder_atomic_subsys1_ports_redundant');

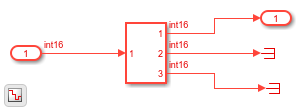

DUT サブシステムには、アクティブな Atomic サブシステムが 2 つ含まれます。

open_system('hdlcoder_atomic_subsys1_ports_redundant/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_atomic_subsys1_ports_redundant/DUT')

Atomic サブシステムは生成された HDL コードで保持されますが、Gain ブロックの計算はコードから削除されます。この場合、複数の Atomic サブシステムのインスタンスはアクティブであり、したがって冗長なロジックは端子境界全体から削除されます。

ENTITY DUT IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out3 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out4 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT atomic_subsys_dead_out_instance_1 PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16 Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out2 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out3 : OUT std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

...

Out1 <= atomic_subsys_dead_out_instance_1_out1;

Out2 <= atomic_subsys_dead_out_instance_1_out2;

Out3 <= atomic_subsys_dead_out_instance_2_out1;

Out4 <= atomic_subsys_dead_out_instance_2_out2;

END rtl;

Atomic Subsystem ブロックの少なくとも 1 つのインスタンスがアクティブでなく、未使用の出力端子が Atomic Subsystem ブロックの外にある場合、生成された HDL コードは [未使用の端子を削除] の設定に応じて変化します。Simulink モデルの HDL コードでの未接続の端子の最適化を参照してください。

マスク サブシステムの冗長なロジック

マスク サブシステムの冗長なロジックは、通常の Subsystem ブロックと同様に削除されます。MaskParameterAsGeneric を on に設定してマスク パラメーターを HDL コードのジェネリックとして生成する場合、汎用の端子はコードで保持されます。

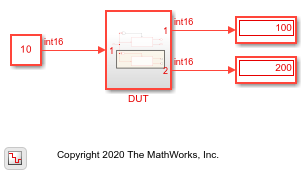

モデル hdlcoder_masked_subsys_redundant を開きます。

open_system('hdlcoder_masked_subsys_redundant') sim('hdlcoder_masked_subsys_redundant');

モデルには、2 つのマスク パラメーター Gain と Gain1 をもつマスク サブシステムが 1 つ含まれます。Gain の値は 10 で、}Gain1| の値は |20} です。

open_system('hdlcoder_masked_subsys_redundant/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_masked_subsys_redundant/DUT')

生成されたコードは、汎用の端子 Gain と Gain1 は保持されますが、出力端子 Out2 は削除されていることを示します。

ENTITY Subsystem IS

GENERIC( Gain : integer := 10;

Gain1 : integer := 20

);

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END Subsystem;ARCHITECTURE rtl OF Subsystem IS

...

kconst <= to_signed(Gain, 16);

In1_signed <= signed(In1);

Gain_mul_temp <= kconst * In1_signed; Gain_out1 <= Gain_mul_temp(15 DOWNTO 0);

Out1 <= std_logic_vector(Gain_out1);

END rtl;

DocBlock と注釈の冗長なロジック

アクティブなサブシステム内にある Annotations ブロックまたは DocBlock ブロックは、生成された HDL コードで保持されます。サブシステムに DUT 出力の評価につながる出力端子が少なくとも 1 つ含まれているか、上記のようにアクティブなブラック ボックス サブシステムが含まれている場合、そのサブシステムはアクティブです。HDL Coder は、注釈または DocBlock を含むサブシステムは冗長であると判別し、その注釈または DocBlock も生成されたコードから削除されます。

モデル hdlcoder_annotations_redundant_logic を開きます。

open_system('hdlcoder_annotation_redundant_logic') sim('hdlcoder_annotation_redundant_logic');

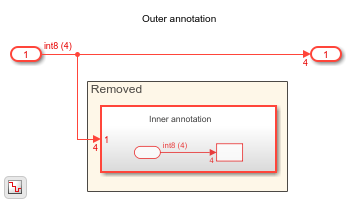

DUT サブシステムには Inner annotation サブシステムが含まれます。このサブシステムは、アクティブな出力端子をもたないため冗長です。

open_system('hdlcoder_annotation_redundant_logic/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_annotation_redundant_logic/DUT')

生成された HDL コードは、注釈 Inner annotation を含む Inner annotation サブシステムが生成された HDL コードから削除されることを示します。

ENTITY DUT IS

PORT( In1 : IN vector_of_std_logic_vector8(0 TO 3); -- int8 [4]

Out2 : OUT vector_of_std_logic_vector8(0 TO 3) -- int8 [4]

);

END DUT;ARCHITECTURE rtl OF DUT IS

BEGIN -- Removed -- -- Outer annotation

Out2 <= In1;

END rtl;

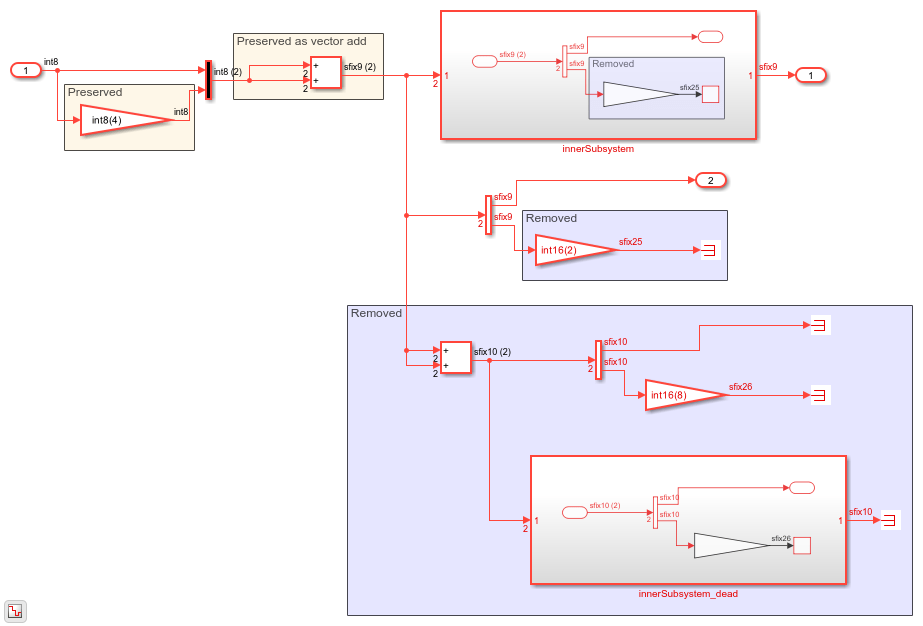

バス信号とバス要素端子の冗長なロジック

冗長なロジックと未使用ブロックは、バスを含む場合にモデルから削除されます。冗長なロジックの最適化は、バーチャル バス、非バーチャル バス、およびバス要素端子と同様に適用されます。

モデル hdlcoder_virtual_bus_redundant を開きます。

open_system('hdlcoder_virtual_bus_redundant') sim('hdlcoder_virtual_bus_redundant');

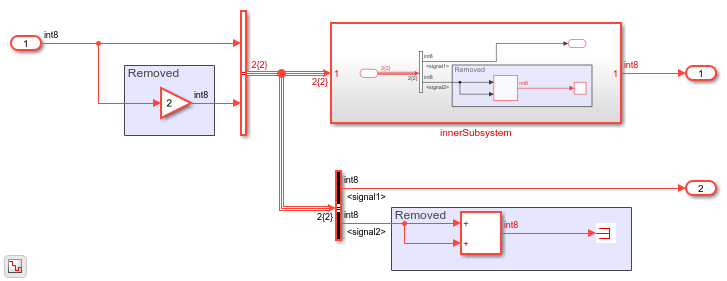

DUT サブシステムには、innerSubsystem ブロックと Add ブロックを駆動するバーチャル バスが含まれます。バス信号の 1 つは、出力で Terminator ブロックに接続しています。

open_system('hdlcoder_virtual_bus_redundant/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_virtual_bus_redundant/DUT')

生成された HDL コードは、設計の冗長なロジックは削除され、アクティブな入力端子と出力端子は保持されることを示します。

ENTITY DUT IS

PORT( In1 : IN std_logic_vector(7 DOWNTO 0); -- int8

Out1 : OUT std_logic_vector(7 DOWNTO 0); -- int8

Out2 : OUT std_logic_vector(7 DOWNTO 0) -- int8

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT innerS PORT( In1_signal1 : IN std_logic_vector(7 DOWNTO 0); -- int8 Out1 : OUT std_logic_vector(7 DOWNTO 0) -- int8 ); END COMPONENT;

...

END rtl;

innerSubsystem ブロック内では、Terminator ブロックに接続している Add ブロックが削除されます。

ENTITY innerSubsystem IS

PORT( In1_signal1 : IN std_logic_vector(7 DOWNTO 0); -- int8

Out1 : OUT std_logic_vector(7 DOWNTO 0) -- int8

);

END innerSubsystem;ARCHITECTURE rtl OF innerSubsystem IS

-- Signals SIGNAL signal1 : signed(7 DOWNTO 0); -- int8

BEGIN -- Removed

signal1 <= signed(In1_signal1);

Out1 <= std_logic_vector(signal1);

END rtl;

ブロックの接続状態の定義

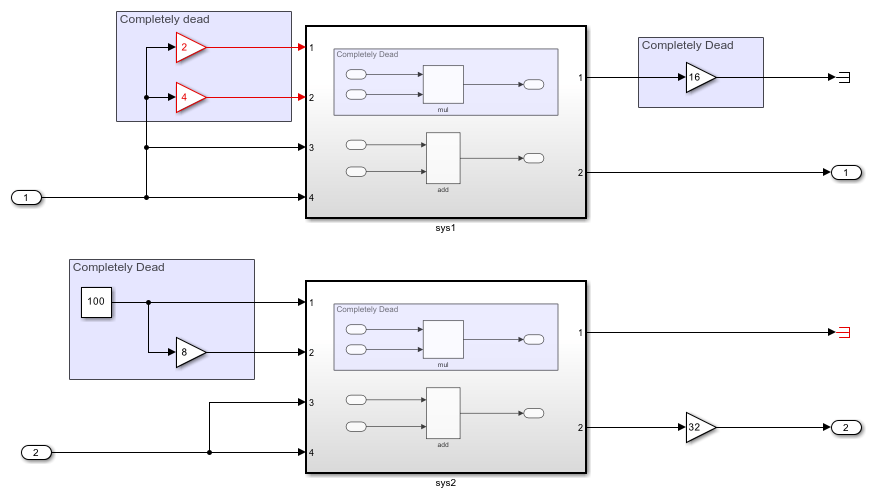

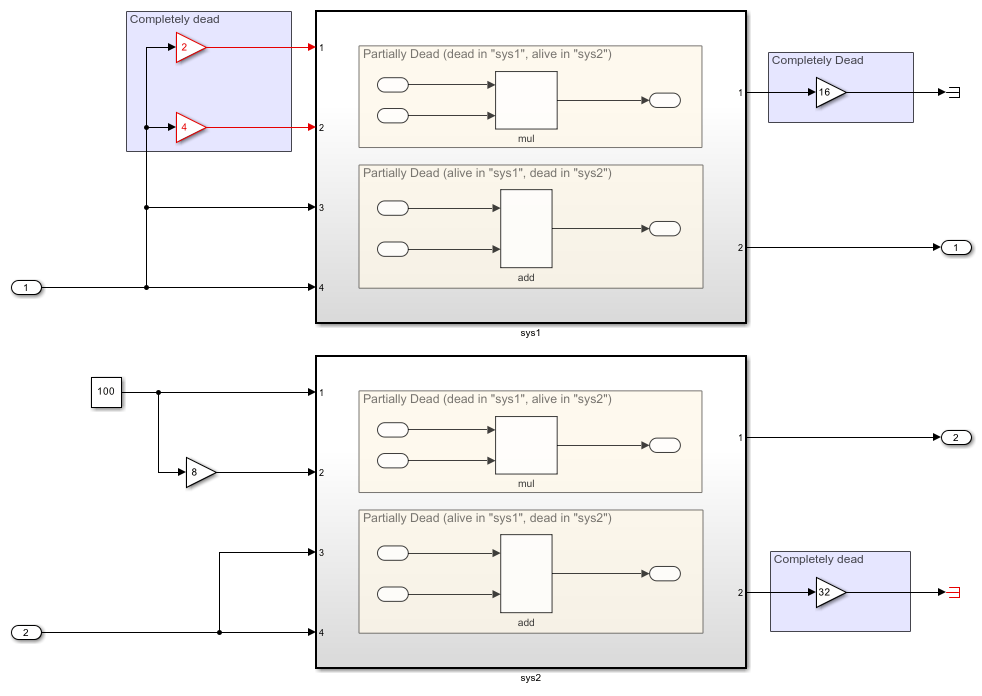

HDL Coder は、ブロックの接続状態を完全に未接続または部分的に接続済みとして分類し、未使用のロジックを検出して削除します。完全に未接続: 複数のインスタンス間で再利用されている同一の Atomic サブシステム、Model ブロック、または ForEach Subsystem ブロックから生成されたモジュールでは、内部モジュールのロジックとモジュールに接続されているブロックのロジックは、モジュールのすべてのインスタンスでそのロジックが使用されていない場合にのみ完全に未接続として分類されます。たとえば、モデル atomic_complete_unconnected.slx を開きます。

open_system('atomic_complete_unconnected') open_system('atomic_complete_unconnected/DUT')

mul ブロックは sys1 と sys2 の両方のサブシステムで使用されていないため、生成されたコードから削除されます。mul ブロックへの入力も完全に未接続であるため、生成されたコードから削除されます。

部分的に接続済み: 複数のインスタンス間で再利用されている同一の Atomic サブシステム、Model ブロック、または ForEach Subsystem ブロックから生成されたモジュールでは、内部モジュールのロジックとモジュールに接続されているブロックのロジックは、モジュールのインスタンスのうち 1 つでもその繰り返しロジックを使用していると部分的に接続済みとして分類されます。たとえば、モデル atomic_partial_connected.slx を開きます。

open_system('atomic_partial_connected')

mul ブロックは sys2 で使用されているため、このブロックは部分的に接続済みとして分類され、ブロックのロジックは生成されたコードで保持されます。mul ブロックへの入力は完全に未使用であるため、生成されたコードから削除されます。

制限

1. モデルに Atomic サブシステム、モデル参照、または ForEach Subsystem ブロックの複数のインスタンスが含まれている場合に、これらのブロックが HDL コード生成中に部分的に接続済みであると判定されると、すべての端子は生成されたコードで保持されます。

2. ベクトル信号をもつモデルでは、Demux ブロックは冗長なロジックの最適化の境界として機能します。Demux ブロックの下流の冗長なロジックとコンポーネントは HDL コード生成中に削除されます。最適化は Demux ブロックの境界を超えず、したがって、Demux ブロックの上流のコンポーネントは保持されます。ベクトルを使用するときの制限は、バスをベクトルに変換するときにも適用されます。

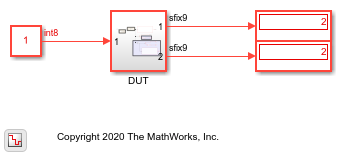

モデル hdlcoder_vector_redundant_logic を開きます。

open_system('hdlcoder_vector_redundant_logic') sim('hdlcoder_vector_redundant_logic');

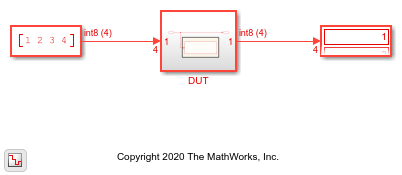

DUT サブシステムには、innerSubsystem ブロックが含まれます。サブシステムにはアクティブな出力端子が 1 つあり、もう 1 つの端子は終端処理されています。

open_system('hdlcoder_vector_redundant_logic/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_vector_redundant_logic/DUT')

生成された HDL コードは、Add ブロックがベクトルの加算計算を実行することを示します。冗長なロジックの最適化が Demux ブロックの境界を越えないため、Gain ブロックと Add ブロックの両方が、生成された HDL コードで保持されます。

ENTITY DUT IS

PORT( In1 : IN std_logic_vector(7 DOWNTO 0); -- int8

Out1 : OUT std_logic_vector(8 DOWNTO 0); -- sfix9

Out2 : OUT std_logic_vector(8 DOWNTO 0) -- sfix9

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT innerSubsystem PORT( In1 : IN vector_of_std_logic_vector9(0 TO 1); -- sfix9 [2] Out1 : OUT std_logic_vector(8 DOWNTO 0) -- sfix9 ); END COMPONENT;

...

In1_signed <= signed(In1);

Gain1_cast <= resize(In1_signed & '0' & '0', 16); Gain1_out1 <= Gain1_cast(7 DOWNTO 0);

Mux_out1(0) <= signed(In1); Mux_out1(1) <= Gain1_out1;

Add_out1_gen: FOR t_0 IN 0 TO 1 GENERATE Add_out1(t_0) <= resize(Mux_out1(t_0), 9) + resize(Mux_out1(t_0), 9); END GENERATE Add_out1_gen;

outputgen: FOR k IN 0 TO 1 GENERATE Add_out1_1(k) <= std_logic_vector(Add_out1(k)); END GENERATE;

Out2 <= std_logic_vector(Add_out1(0));

...

END rtl;