サブシステムのブラック ボックス インターフェイスの生成

ブラック ボックス インターフェイスとは

サブシステムの "ブラック ボックス" インターフェイスは、生成された VHDL® コンポーネントまたは Verilog® モジュールまたは SystemVerilog モジュールです。これらには、サブシステム用に HDL の入力および出力端子の定義のみが含まれています。このようなコンポーネントを生成することで、モデル内のサブシステムを使用して既存の手書きの HDL コード、サードパーティ製の IP または HDL Coder™ で生成された他のコードへのインターフェイスを生成できます。

要件

ブラック ボックスの実装は、DUT より低いレベルのサブシステム ブロックでのみ使用できます。また、DUT より低いレベルのカスタム ライブラリのバーチャルおよび Atomic Subsystem ブロックでも、ブラック ボックス実装を使用できます。

サブシステム用のブラック ボックス インターフェイスの生成

インターフェイスを生成するには、1 つ以上の Subsystem ブロックで BlackBox 実装を選択します。

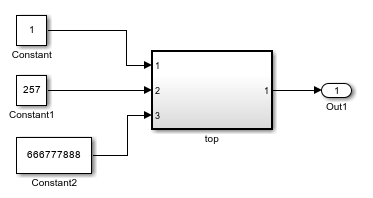

テスト対象デバイス (DUT) となるサブシステム top を含む ex_blackbox_subsys モデルについて考えます。ex_blackbox_subsys モデルを開きます。

load_system("ex_blackbox_subsys.slx") open_system("ex_blackbox_subsys.slx")

サブシステム top には 2 つの下位レベルのサブシステムが含まれています。

open_system("ex_blackbox_subsys/top")

Interface サブシステムのブラック ボックス インターフェイスを使用して top モデルから HDL コードを生成するには、次の手順に従います。

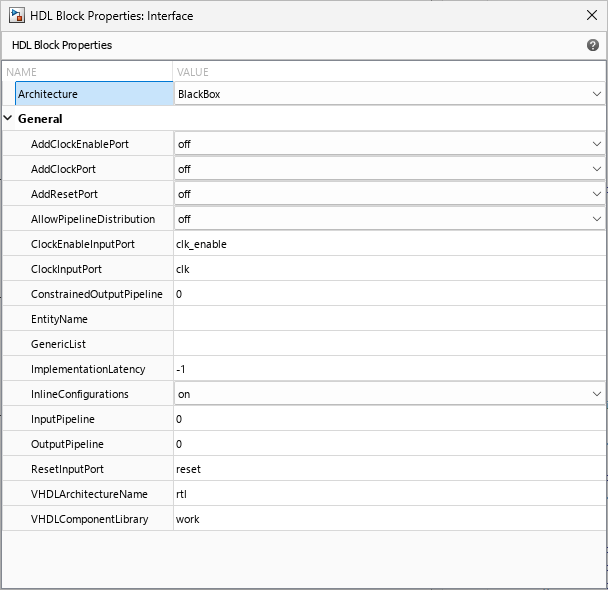

Interfaceサブシステムを右クリックします。コンテキスト メニューに HDL Coder アプリのオプションを追加するには、[アプリの選択] をポイントし、[HDL Coder] をクリックします。次に、HDL Coder アプリのセクションで [HDL ブロック プロパティ] を選択します。[Architecture] を

BlackBoxに設定します。

次のパラメーターがブラック ボックスの実装に使用できます。ブラック ボックスの実装に使用できる HDL ブロック パラメーターで、生成されるインターフェイスをカスタマイズできます。これらのパラメーターについては、ブラック ボックスまたは HDL コシミュレーション インターフェイスのカスタマイズを参照してください。

ブラック ボックス インターフェイスをもつサブシステムに渡す VHDL generic および generic map を生成するには、[HDL ブロック プロパティ] ダイアログ ボックスで "GenericList" パラメーターを {{'Param1','234'},{'Param2','"1"','STD_LOGIC'},{'Param3'','"1101"','STD_LOGIC_VECTOR(3 DOWNTO 0)'}} に設定します。

あるいは、hdlset_param 関数を使用して、モデル内のブラック ボックス Interface サブシステムの "GenericList" パラメーターを設定します。MATLAB コマンド ウィンドウで次のように入力します。

hdlset_param('ex_blackbox_subsys/top/Interface','GenericList',... '{{''Param1'',''234''},{''Param2'',''"1"'',''STD_LOGIC''},{''Param3'',''"1101"'',''STD_LOGIC_VECTOR(3 DOWNTO 0)''}}');

"GenericList" ブロック パラメーターへの入力は、それぞれ 2 つまたは 3 つの文字配列をもつ 3 つの cell 配列を含む cell 配列変数です。これらの文字配列は、VHDL generic の名前、値、およびデータ型を表します。この例では、Param1 のデータ型は integer、Param2 は STD_LOGIC、Param3 は STD_LOGIC_VECTOR です。スカラーおよびベクトルの値を示すには二重引用符を使用します。"GenericList" パラメーターの構文の詳細については、ブラック ボックスまたは HDL コシミュレーション インターフェイスのカスタマイズを参照してください。

ブラック ボックス サブシステム実装のためのコードの生成

ex_blackbox_subsys モデル内の DUT のコードを生成する場合、次のメッセージが表示されます。

makehdl("ex_blackbox_subsys/top")### Working on the model ex_blackbox_subsys ### Generating HDL for ex_blackbox_subsys/top ### Using the config set for model ex_blackbox_subsys for HDL code generation parameters. ### Running HDL checks on the model 'ex_blackbox_subsys'. ### Begin compilation of the model 'ex_blackbox_subsys'... ### Working on the model 'ex_blackbox_subsys'... ### Working on... GenerateModel ### Begin model generation 'gm_ex_blackbox_subsys'... ### Rendering DUT with optimization related changes (IO, Area, Pipelining)... ### Model generation complete. ### Generated model saved at hdlsrc/ex_blackbox_subsys/gm_ex_blackbox_subsys.slx ### Begin VHDL Code Generation for 'ex_blackbox_subsys'. ### Working on ex_blackbox_subsys/top/gencode as hdlsrc/ex_blackbox_subsys/gencode.vhd. ### Working on ex_blackbox_subsys/top as hdlsrc/ex_blackbox_subsys/top.vhd. ### Code Generation for 'ex_blackbox_subsys' completed. ### Generating HTML files for code generation report at index.html ### Creating HDL Code Generation Check Report top_report.html ### HDL check for 'ex_blackbox_subsys' complete with 0 errors, 1 warnings, and 0 messages. ### HDL code generation complete.

この進行状況メッセージ内で、gencode サブシステムがその VHDL エンティティの定義用に別のファイル gencode.vhd を生成していることが確認できます。Interface サブシステムでは、このようなファイルは生成されません。このサブシステムのインターフェイス コードは、ex_blackbox_subsys/top から生成される top.vhd 内にあります。次のコード リストは、Interface サブシステム用に生成されたコンポーネントの定義とインスタンス化を説明しています。

COMPONENT Interface

GENERIC( Param1 : integer;

Param2 : STD_LOGIC;

Param3 : STD_LOGIC_VECTOR(3 DOWNTO 0)

);

PORT( clk : IN std_logic;

clk_enable : IN std_logic;

reset : IN std_logic;

In1 : IN std_logic_vector(7 DOWNTO 0); -- uint8

In2 : IN std_logic_vector(15 DOWNTO 0); -- uint16

In3 : IN std_logic_vector(31 DOWNTO 0); -- uint32

Out1 : OUT std_logic_vector(31 DOWNTO 0) -- uint32

);

END COMPONENT;

...

u_Interface : Interface

GENERIC MAP( Param1 => 234,

Param2 => "1",

Param3 => "1101"

)

PORT MAP( clk => clk,

clk_enable => enb_const_rate,

reset => reset,

In1 => gencode_out1, -- uint8

In2 => gencode_out2, -- uint16

In3 => gencode_out3, -- uint32

Out1 => Interface_out1 -- uint32

);

enb_const_rate <= clk_enable;

Out1 <= Interface_out1;

既定では、サブシステム用に生成されたブラック ボックス インターフェイスにはクロック、クロック イネーブルおよびリセット端子が含まれます。これらの信号の名前の変更方法や生成の抑制方法および生成されたインターフェイスの他の要素のカスタマイズ方法については、ブラック ボックスまたは HDL コシミュレーション インターフェイスのカスタマイズを参照してください。

制限

[Architecture] HDL ブロック プロパティが

[BlackBox]に設定されたマスク サブシステムには、双方向端子は使用できません。DocBlock を含むブラック ボックス サブシステムが別のブラック ボックス サブシステムに配置されている場合、内側の DocBlock の HDL コードは HDL Coder によるコード生成時に統合されません。

カスタムの

packageの宣言を含む DocBlock がブラック ボックス サブシステムに含まれている場合、それらのパッケージのデータ型は HDL Coder で生成されるインターフェイス コードに含まれません。HDL アーキテクチャが

[BlackBox]である Subsystem ブロックにリセット信号が必要な場合、[MinimizeGlobalResets] パラメーターを選択しても HDL Coder でリセット ロジックが生成されます。アーキテクチャが

[BlackBox]であるサブシステムで [ImplementationLatency] ブロック プロパティが負の値に設定されている場合、遅延の均衡化は実行できません。[Architecture] HDL ブロック プロパティが

[BlackBox]に設定されたサブシステムまたは Model ブロックには、クロックレート パイプラインは使用できません。[Architecture] HDL ブロック プロパティが

[BlackBox]に設定されたマスク サブシステムには、バス要素端子は使用できません。