このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

DocBlock を使用したカスタム HDL コードの統合

1 つ以上の DocBlock ブロックを使用してカスタム HDL コードを設計に統合できます。

カスタム コードの統合に DocBlock を使用する場合

HDL コードを個別のファイルとしてではなくモデルで維持する場合は、DocBlock を使用してカスタム HDL コードを統合します。DocBlock 内のテキストはカスタム VHDL®、Verilog®、または SystemVerilog コードです。

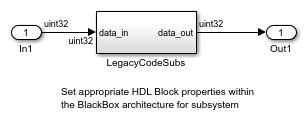

カスタム HDL コードが含まれる各 DocBlock を含めるには、それぞれをブラック ボックス サブシステムに配置し、そのブラック ボックス サブシステムをテスト対象設計 (DUT) に含めます。ブラック ボックス サブシステムごとに 1 つの HDL ファイルが生成されます。

カスタム コード統合の代替方法

カスタム コードが知的所有権 (IP) またはサードパーティ ベンダーのライブラリなどの場合にカスタム HDL コードをモデルとは別に維持するには、ブラック ボックス サブシステムまたはブラック ボックス モデル参照を使用します。

DocBlock を使用したカスタム コードの統合

DUT 内の任意の階層レベルで、Subsystem ブロックを追加します。

Subsystem ブロックの場合は、[HDL ブロック プロパティ] ダイアログ ボックスで次の手順に従います。

[Architecture] を

[BlackBox]に設定します。カスタム HDL コード インターフェイスと一致するように、ブラック ボックス サブシステム インターフェイスをカスタマイズします。ブラック ボックスまたは HDL コシミュレーション インターフェイスのカスタマイズを参照してください。

サブシステムで、DocBlock ブロックを追加します。

DocBlock の場合は、[HDL ブロック プロパティ] ダイアログ ボックスで次を行います。

[Architecture] を

[HDLText]に設定します。[TargetLanguage] を、

[Verilog]、[SystemVerilog]、[VHDL]などのターゲット言語に設定します。

DocBlock に、カスタムの Verilog または SystemVerilog

module、あるいは VHDLentityに対する HDL コードを入力します。言語は DocBlock [TargetLanguage] 設定と一致していなければなりません。

制限

DocBlock を含むブラック ボックス サブシステムを最上位 DUT にすることはできません。

ブラック ボックス サブシステムは最大 2 つの DocBlock ブロックをもつことができます。2 つの DocBlock ブロックがある場合、1 つのブロックで [TargetLanguage] を

[VHDL]に設定し、もう 1 つのブロックで [TargetLanguage] を[Verilog]または[SystemVerilog]のいずれかに設定しなければなりません。コードを生成する場合、HDL Coder™ はコード生成のターゲット言語と一致する DocBlock からコードを統合します。

DocBlock を含むブラック ボックス サブシステムが別のブラック ボックス サブシステムに配置されている場合、その DocBlock の HDL コードは HDL Coder によるコード生成時に統合されません。

カスタムの

packageの宣言を含む DocBlock がブラック ボックス サブシステムに含まれている場合、それらのパッケージのデータ型は HDL Coder で生成されるインターフェイス コードに含まれません。

Doc ブロックを使用してカスタム HDL コードを含める

hdlcoderIncludeCustomHdlUsingDocBlockExample モデルは、DocBlock ブロックを使用してカスタムの VHDL コードと Verilog コードを設計に統合する方法を示したものです。

hdlcoderIncludeCustomHdlUsingDocBlockExample モデルを開くには、次のコマンドを実行します。

load_system('hdlcoderIncludeCustomHdlUsingDocBlockExample.slx'); open_system('hdlcoderIncludeCustomHdlUsingDocBlockExample/DUT');

LegacyCodeSubs サブシステムに、従来の VHDL コードと Verilog コードを含む 2 つの DocBlock ブロックがあります。makehdlコマンドを使用して DUT サブシステムの HDL コードを生成できます。