このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

Simulink モデルの HDL コードでの未接続の端子の最適化

HDL コード生成において、生成されたコードから未接続の端子を削除することで、コードの可読性が向上し、コード サイズと使用面積が削減されます。この改善には、未接続のベクトル端子とスカラー端子、バス要素端子およびバス端子の削除が含まれます。未接続の端子の削除により、生成されたコードの未使用の端子が原因の合成の失敗を回避できることがあります。

未使用の端子の削除

未使用の端子の削除は、設計での未使用のブロックの削除と共に行われます。生成された HDL コードの冗長なロジックと未使用ブロックの削除を参照してください。

未使用の端子を削除した効果は、生成された HDL コードで確認できます。最上位の DUT モデルまたはサブシステム、実装モデル、検証モデルからは端子は削除されません。

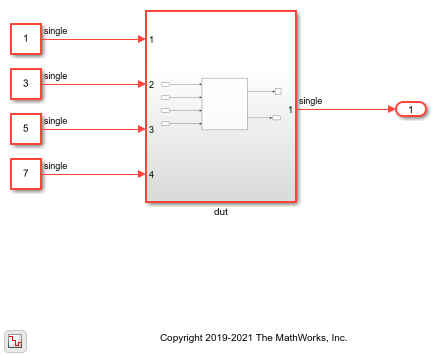

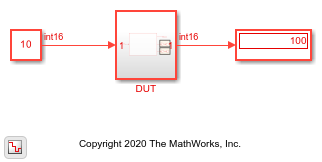

バス要素端子および非アクティブな出力に接続している端子を含むモデル hdlcoder_RemoveUnconnectedPorts を開きます。

open_system('hdlcoder_RemoveUnconnectedPorts') set_param('hdlcoder_RemoveUnconnectedPorts', 'SimulationCommand', 'update');

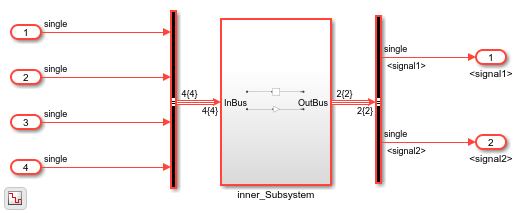

dut Subsystem ブロックを開いてから、mid_Subsystem ブロックを開きます。mid_Subsystem には、バス要素端子が含まれます。出力信号の 1 つは Terminator ブロックに接続されています。

open_system('hdlcoder_RemoveUnconnectedPorts/dut/mid_Subsystem')

設計の HDL コードを生成するには、MATLAB® コマンド プロンプトで次のように入力します。

makehdl('hdlcoder_RemoveUnconnectedPorts/dut')

生成されたコード mid_Subsystem.vhd は、未接続の端子が HDL コード生成中に削除されることを示します。DUT 入力端子の入力 InBus_signal3 は、Gain ブロックで乗算され、出力端子 OutBus_signal2 に接続されてから DUT 出力端子に渡されます。その他の入力端子と出力端子は DUT レベルで未使用であるため、これらの端子は生成された HDL コードから削除されます。

ARCHITECTURE rtl OF mid_Subsystem IS

-- Component Declarations COMPONENT inner_Subsystem PORT( clk : IN std_logic; reset : IN std_logic; enb : IN std_logic; InBus_signal3 : IN std_logic_vector(31 DOWNTO 0); -- single OutBus_signal2 : OUT std_logic_vector(31 DOWNTO 0) -- single ); END COMPONENT;

...

END rtl;

未使用の端子の削除の最適化の無効化

既定では、最適化は有効になっていて、未使用の端子は生成された HDL コードで削除されます。

接続されていない端子が設計から削除されないようにするには、以下を実行します。

[コンフィギュレーション パラメーター] ダイアログ ボックスで、未使用の端子を削除のチェック ボックスをオフにします。

HDL ワークフロー アドバイザーの実行時に、[コード生成オプションを設定]、[最適化オプションを設定] タスクで [未使用の端子を削除] チェック ボックスをオフにします。

コマンド ラインで、

hdlset_paramまたはmakehdlを指定してDeleteUnusedPortsをoffに設定します。たとえば、hdlcoder_RemoveUnconnectedPortsモデルの未使用の端子を保持すると指定するには、次のコマンドを実行します。

makehdl('hdlcoder_RemoveUnconnectedPorts/dut', 'DeleteUnusedPorts', 'off')

生成された HDL コードでは、未使用のバス要素端子が保持されます。

ARCHITECTURE rtl OF mid_Subsystem IS

-- Component Declarations COMPONENT inner_Subsystem PORT( clk : IN std_logic; reset : IN std_logic; enb : IN std_logic; InBus_signal1 : IN std_logic_vector(31 DOWNTO 0); -- single InBus_signal2 : IN std_logic_vector(31 DOWNTO 0); -- single InBus_signal3 : IN std_logic_vector(31 DOWNTO 0); -- single InBus_signal4 : IN std_logic_vector(31 DOWNTO 0); -- single OutBus_signal1 : OUT std_logic_vector(31 DOWNTO 0); -- single OutBus_signal2 : OUT std_logic_vector(31 DOWNTO 0) -- single ); END COMPONENT;

...

END rtl;

サブシステムの端子の未使用の端子の削除

この最適化は、未使用のサブシステムのデータ端子を削除できます。制御端子と参照モデルの端子は削除されません。

サブシステムのデータ端子は、DUT 出力端子のダウンストリームに影響する場合、またはアクティブなブラック ボックス サブシステムに接続している場合や HDL コード生成中に保持されるコンポーネントに接続している場合に、アクティブであると見なされます。

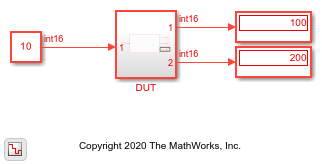

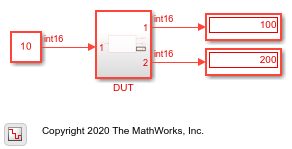

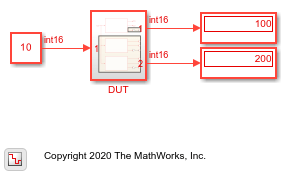

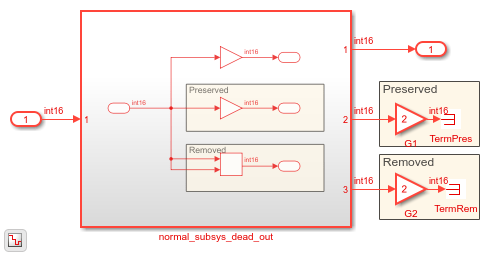

モデル hdlcoder_subsys_ports_unused を開きます。

open_system('hdlcoder_subsys_ports_unused') sim('hdlcoder_subsys_ports_unused');

モデルには、終端処理され、DUT 出力に影響しない出力端子 out3 を含む normal_subsys_dead_out サブシステムが含まれます。

open_system('hdlcoder_subsys_ports_unused/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_subsys_ports_unused/DUT')

既定では、DeleteUnusedPorts が on に設定されている場合、Add ブロックの計算と出力端子 Out3 は生成された HDL コードで削除されます。

ENTITY normal_subsys_dead_out IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END normal_subsys_dead_out;ARCHITECTURE rtl OF normal_subsys_dead_out IS

...

Out1 <= std_logic_vector(Gain_out1);

...

Out2 <= std_logic_vector(Gain1_out1);

END rtl;

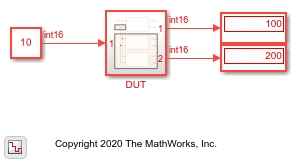

DeleteUnusedPorts 最適化を無効にするには、次のコマンドを実行します。

makehdl('hdlcoder_subsys_ports_unused/DUT', 'DeleteUnusedPorts', 'off')

DeleteUnusedPorts を off に設定すると、この端子と Add ブロックの計算は生成された HDL コードで保持されます。

ENTITY normal_subsys_dead_out IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out3 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END normal_subsys_dead_out;ARCHITECTURE rtl OF normal_subsys_dead_out IS

...

Out1 <= std_logic_vector(Gain_out1);

...

Out2 <= std_logic_vector(Gain1_out1

Add_out1 <= to_signed(16#0000#, 16);

Out3 <= std_logic_vector(Add_out1);

END rtl;

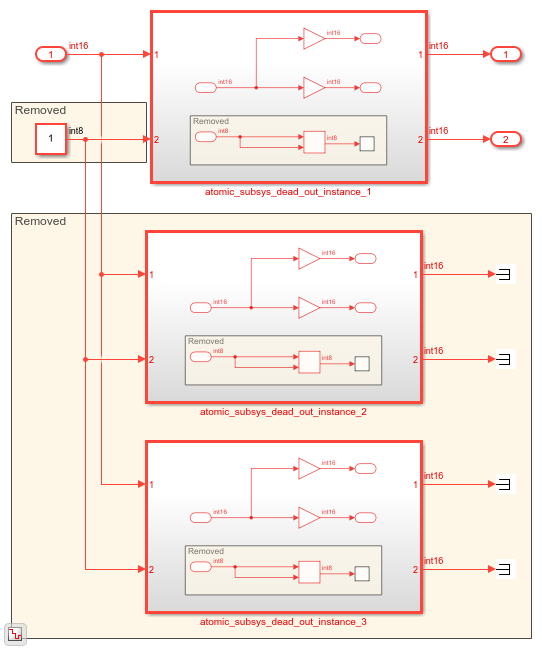

Atomic サブシステムの未使用の端子の削除

Atomic サブシステムの外にある未使用の端子の場合、Atomic サブシステムのインスタンスは生成された HDL コードから削除されます。

モデル hdlcoder_atomic_subsys3_redundant を開きます。

open_system('hdlcoder_atomic_subsys3_redundant') sim('hdlcoder_atomic_subsys3_redundant');

DUT サブシステムには、Atomic サブシステムのインスタンスが 3 つあります。Atomic サブシステムのインスタンスの 2 つの出力は、Terminator ブロックに接続しています。

open_system('hdlcoder_atomic_subsys3_redundant/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_atomic_subsys3_redundant/DUT')

ENTITY DUT IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT atomic_subsys_dead_out_instance_1 PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16 Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

...

END rtl;

DeleteUnusedPorts を off に設定するには、次のコマンドを実行します。

makehdl('hdlcoder_atomic_subsys3_redundant/DUT', 'DeleteUnusedPorts', 'off')

DeleteUnusedPorta を off に設定する場合、入力端子 In2 は、生成された HDL コードで保持されますが、未使用のコンポーネントを駆動する入力端子に接続しています。

ENTITY DUT IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT atomic_subsys_dead_out_instance_1 PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16 In2 : IN std_logic_vector(7 DOWNTO 0); -- int8 Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

...

END rtl;

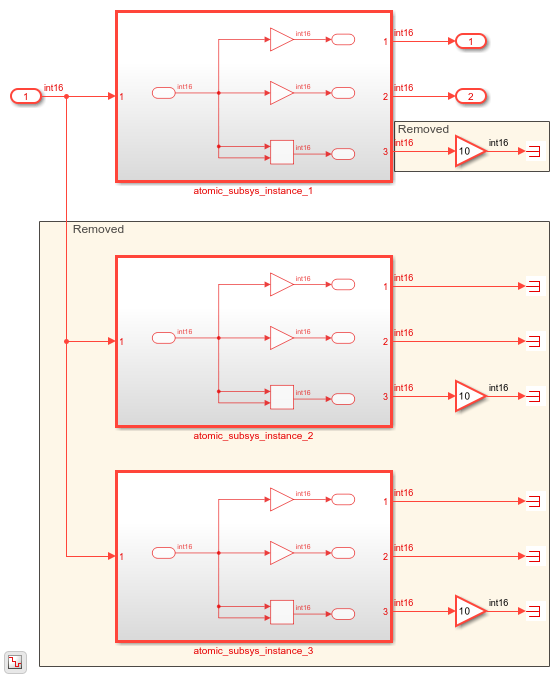

Atomic サブシステムの出力端子の未使用の端子の削除

アクティブな Atomic サブシステムのインスタンスが複数ある場合、任意の端子を含む境界を超える冗長なロジックは DeleteUnusedPorts 設定に関係なく HDL コードで保持されます。DeleteUnusedPorts が on に設定されていて、既定で、Atomic サブシステムのインスタンスが 1 つしかない場合、サブシステムの境界を超える冗長なロジックと端子は削除されます。DeleteUnusedPorts を off に設定すると、未使用の端子は、ロジックが冗長であっても保持されます。

モデル hdlcoder_atomic_subsys2_ports_redundant を開きます。

open_system('hdlcoder_atomic_subsys2_ports_redundant') sim('hdlcoder_atomic_subsys2_ports_redundant');

DUT サブシステムには、サブシステムの外で終端処理される出力端子に接続している Add ブロックを含む Atomic Subsystem ブロックが含まれます。

open_system('hdlcoder_atomic_subsys2_ports_redundant/DUT')

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_atomic_subsys2_ports_redundant/DUT')

Add ブロックはアクティブな出力に影響しないため、生成された HDL コードでは、Add ブロックと対応する出力端子 Out3 は削除されます。

ENTITY DUT IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT single_instance_atomic_subsys_dead_out PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16 Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

...

END rtl;

DeleteUnusedPorts を off に設定するには、次のコマンドを実行します。

makehdl('hdlcoder_atomic_subsys2_ports_redundant/DUT', 'DeleteUnusedPorts', 'off')

DeleteUnusedPorts を off に設定すると、出力端子 Out3 は生成された HDL コードで保持されます。

ENTITY DUT IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT single_instance_atomic_subsys_dead_out PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16 Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16 Out3 : OUT std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

...

END rtl;

ENTITY single_instance_atomic_subsys_dead_out IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out3 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END single_instance_atomic_subsys_dead_out;ARCHITECTURE rtl OF single_instance_atomic_subsys_dead_out IS

...

Add_out1 <= to_signed(16#0000#, 16);

Out3 <= std_logic_vector(Add_out1);

END rtl;

アクティブではない Atomic サブシステムのインスタンスが複数ある場合、未使用の端子とロジックは削除されるか、DeleteUnusedPorts 設定に応じて保持されます。

モデル hdlcoder_atomic_subsys3_ports_redundant を開きます。

open_system('hdlcoder_atomic_subsys3_ports_redundant') sim('hdlcoder_atomic_subsys3_ports_redundant');

DUT サブシステムには、サブシステムの外で終端処理される出力端子に接続している Add ブロックを含む Atomic Subsystem ブロックが含まれます。

open_system('hdlcoder_atomic_subsys3_ports_redundant/DUT')

終端処理されている出力端子をもつ 2 つの Atomic サブシステムのインスタンスは、生成された HDL コードから削除されます。その他の Atomic Subsystem ブロックでは、Add ブロックの計算とその出力は削除されます。

ENTITY DUT IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT atomic_subsys_instance_1 PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16 Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

...

-- Removed -- -- Removed

u_atomic_subsys_instance_1 : atomic_subsys_instance_1

PORT MAP( In1 => In1, -- int16

Out1 => atomic_subsys_instance_1_out1, -- int16

Out2 => atomic_subsys_instance_1_out2 -- int16

);Out1 <= atomic_subsys_instance_1_out1;

Out2 <= atomic_subsys_instance_1_out2;

END rtl;

DeleteUnusedPorts を off に設定するには、次のコマンドを実行します。

makehdl('hdlcoder_atomic_subsys3_ports_redundant/DUT', 'DeleteUnusedPorts', 'off')

DeleteUnusedPorts を off に設定すると、出力端子 Out3 は生成された HDL コードで保持されます。

ENTITY DUT IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END DUT;ARCHITECTURE rtl OF DUT IS

-- Component Declarations COMPONENT atomic_subsys_instance_1 PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16 Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out2 : OUT std_logic_vector(15 DOWNTO 0); -- int16 Out3 : OUT std_logic_vector(15 DOWNTO 0) -- int16 ); END COMPONENT;

Atomic サブシステムのインスタンスの生成された HDL コードを表示すると、Add ブロックの計算と Out3 は生成された HDL コードで保持されていることが示されます。

ENTITY atomic_subsys_instance_1 IS

PORT( In1 : IN std_logic_vector(15 DOWNTO 0); -- int16

Out1 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out2 : OUT std_logic_vector(15 DOWNTO 0); -- int16

Out3 : OUT std_logic_vector(15 DOWNTO 0) -- int16

);

END atomic_subsys_instance_1;ARCHITECTURE rtl OF atomic_subsys_instance_1 IS

...

Add_out1 <= In1_signed + In1_signed;

Out3 <= std_logic_vector(Add_out1);

END rtl;

上流のロジックにおける未使用の端子の保持

Terminator ブロックの上流にある未使用のロジックを保持して、それ以外の未接続の端子と未使用のロジックを削除できます。生成された HDL コードで保持する特定の未使用のブロックを選択し、モデルの残りの部分を最適化できます。上流のロジックを保持する Terminator ブロックで HDL ブロック プロパティ PreserveUpstreamLogic を有効にします。PreserveUpstreamLogicを参照してください。

モデル hdlcoder_subsys_port_preserve を開きます。

open_system('hdlcoder_subsys_ports_preserved') sim('hdlcoder_subsys_ports_preserved');

このモデルに含まれる DUT サブシステムには、サブシステムの出力端子として 2 つの Terminator ブロックがあります。Terminator ブロック TermPres では、HDL ブロック プロパティ PreserveUpstreamLogic がオンに設定されています。これは Terminator ブロック TermRem にはありません (既定の設定です)。モデル プロパティ DeleteUnusedPorts が既定で有効になっています。

open_system('hdlcoder_subsys_ports_preserved/DUT') hdlget_param('hdlcoder_subsys_ports_preserved/DUT/TermPres', 'PreserveUpstreamLogic')

ans =

'on'

HDL コードを生成すると、normal_subsys_dead_out サブシステムからの出力端子 Out2 など、TermPres ブロックの上流で接続されたロジックは HDL コードで保持されます。Terminator ブロックで PreserveUpstreamLogic を有効にすると、有効になっている DeleteUnusedPorts オプションよりも優先されます。TermRem ブロックの上流で接続されたロジックは保持されず、normal_subsys_dead_out サブシステムからの出力端子も保持されません。

DUT サブシステムの HDL コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_subsys_ports_preserved/DUT')

コードのトレーサビリティ レポートで、TermPres に接続された Gain G1 をクリックします。対応する HDL コードで、G1 などの TermPres の上流で接続されたロジックは保持されています。TermRem の上流のロジックについては、対応する HDL コードは存在しません。

makehdl コマンドの出力でスクリプト highlightRemovedDeadBlocks.m をクリックすると、TermRem の上流で削除された論理ブロックを強調表示できます。削除されたブロックはモデル内で赤色で表示されます。強調表示を解除するには、スクリプト clearHighlightingRemovedDeadBlocks.m をクリックします。

すべての削除されたバーチャル ブロックもコード生成レポートで表示できます。[トレーサビリティ レポート] をクリックして、[削除された / バーチャル ブロック] セクションを表示します。

モデルの DeleteUnusedPorts を無効にすると、TermRem に接続された normal_subsys_dead_out サブシステムからの出力端子は保持して、残りの上流のロジックを削除できます。

hdlset_param('hdlcoder_subsys_ports_preserved', 'DeleteUnusedPorts', 'off')

DUT サブシステムの HDL コードを生成します。

makehdl('hdlcoder_subsys_ports_preserved/DUT');

トレーサビリティ レポートで、前回生成された HDL コードと今回の HDL コードで異なる部分が強調表示されます。PreserveUpstreamLogic がオフであるため、Gain ブロック G2 など、TermRem の上流のロジックは今回も削除されます。モデルの DeleteUnusedPorts が off に設定されているため、出力端子 Out3 は生成された HDL コードに含まれています。

制限

モデルに Atomic サブシステムの複数のインスタンス、モデル参照、または Foreach Subsystem ブロックが含まれている場合に、これらのブロックが HDL コード生成中にアクティブであると、端子は生成されたコードで保持されます。これらの端子に上流で接続しているコンポーネントもアクティブであると見なされます。DeleteUnusedPorts 設定を有効または無効にしているかに関係なく、端子は保持されます。

この制限は、バス信号にも適用されます。この場合、生成された HDL コードでバス全体が保持されます。例については、生成された HDL コードの冗長なロジックと未使用ブロックの削除を参照してください。