このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

HDL QPSK 送信機および受信機

この例では、Simulink® で HDL コード生成とハードウェア実装用に最適化された QPSK 送受信機を実装する方法を示します。

この例で示すモデルは、直交位相偏移変調 (QPSK) に基づいてデータを変調します。この例の目標は、リアルタイム システム用に情報を送信して復元できる HDL QPSK 通信システムをモデル化することです。受信機で、単一搬送波通信システムに欠かせないシンボル タイミング同期および搬送波の周波数と位相の同期を実装します。

システム仕様

このセクションでは、この例で使用する送信機と受信機の仕様について説明します。送信機はパケットベースのフレーム形式を使用します。プリアンブル シーケンスを生成するには、QPSK 変調器で同一のビットが同相と直交位相で変調されるように、13 ビットのバーカー シーケンスの各ビットを 2 回繰り返します。プリアンブル シーケンスの後に、2240 ビットのペイロード データが続きます。送信機はルート レイズド コサイン (RRC) パルス整形フィルターを使用して実行されます。ロールオフ係数は 0.5 であるため、帯域幅はシンボル レートの 1.5 倍になります。これは、シンボルごとに 4 つのサンプルを使用するため、サンプル レートはシンボル レートの 4 倍になります。RRC インパルス応答は隣接する 4 つのシンボルにまたがります。ビット レートは、シンボル レートの 2 倍です。実効平均ビット レートは、ビット レートにフレーム効率を掛けて求められます。フレーム効率は (2240/(2240+26)) で、これは 0.9885 になります。

既定のシンボル レートは 1.92 Mbaud に設定されています。したがって、帯域幅は 1.92e6 の 1.5 倍で 2.88 MHz、サンプル レートは 1.92e6 の 4 倍で 7.68 Msps、ビット レートは 1.92e6 の 2 倍で 3.84 Mbps になります。このシステムでサポートされる実効平均ビット レートは、3.84e6 に 0.9885 を掛けて 3.7959 Mbps となります。システム全体は、最大シングル クロック レート 7.68 MHz で動作します。より低いサンプル レートを実現するため、有効な信号が適切に処理されます。これらの仕様はシンボル レートを変更すると変わります。

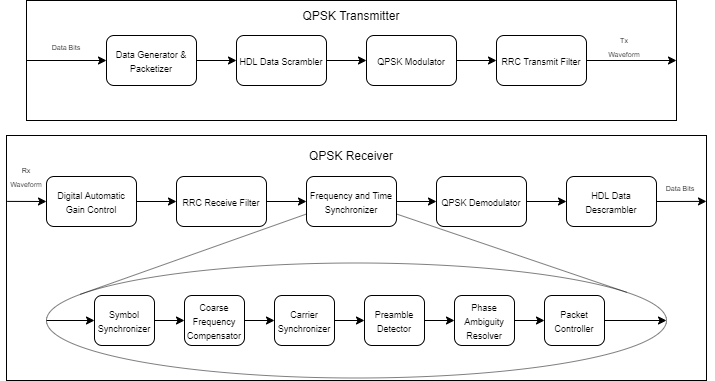

モデル アーキテクチャ

このセクションでは、ブロック線図に示す QPSK 送受信機の大まかなアーキテクチャについて説明します。QPSK 送信機は、シンボル レートの 2 倍のビット レートで入力をサンプリングします。Data Generator & Packetizer は、データ ビットを収集し、プリアンブル ビットを生成し、パケット ビットを形成します。HDL Data Scrambler は、各パケットのデータ ビットをスクランブルしてビット遷移を増やし、同じビットの実行シーケンスが長くならないようにします。QPSK Modulator は、パケット ビットを変調して QPSK シンボルを生成します。RRC Transmit Filter は、QPSK シンボルをアップサンプリングしてパルス整形し、シンボル レートの 4 倍のサンプル レートの Tx 波形を生成します。QPSK 受信機は、伝送速度で入力をサンプリングします。Digital AGC は、受信波形が目的の振幅レベルになるようにゲイン制御を実行します。RRC Receive Filter は、AGC の出力に対して整合フィルター処理を実行します。Frequency and Time Synchronizer は、同期処理を実行し、各パケットの QPSK シンボルを生成します。QPSK Demodulator は、QPSK シンボルを復調してパケット ビットを生成します。HDL Data Descrambler は、受信機からストリーミングされるパケットのデータ ビットをデスクランブルします。

ファイル構造

この例には、以下の Simulink モデルと MATLAB® スクリプトが含まれています。

commhdlQPSKTxRx— 最上位の Simulink モデルcommhdlQPSKTxRxParameters— 初期化に必要な QPSK Tx と QPSK Rx のパラメーターを生成commhdlQPSKTxRxModelInit—commhdlQPSKTxRxモデルを初期化generateHelloworldMsgBits— "Hello world xxx " メッセージ ビットを生成。"xxx" は 000 から 100 までの値を表す。

システム インターフェイス

次の図は、QPSK 送受信機システムの最上位モデルを示しています。

送信機の入力

dataIn — 入力データ。boolean スカラーとして指定します。

validIn — "dataIn" を有効にするための制御信号。boolean スカラーとして指定します。

送信機の出力

dataOut — 出力送信波形。シンボル レートの 4 倍のサンプル レートの 16 ビット複素数データとして返されます。

validOut — "dataOut" を有効にするための制御信号。boolean スカラーとして返されます。

txDiagBus — 診断出力を含むステータス信号。バス信号として返されます。

dataReady — 入力信号に対する準備状況を示す信号。boolean スカラーとして返されます。

受信機の入力

dataIn — 入力データ。送信機出力と同じサンプル レートの 16 ビット複素数データとして指定します。

validIn — "dataIn" を有効にするための制御信号。boolean スカラーとして指定します。

受信機の出力

dataOut — 復号化された出力データ ビット。boolean スカラーとして返されます。

ctrlOut — start、end、valid の信号を含むバス信号。バス信号として返されます。

rxDiagBus — 診断出力を含むステータス信号。バス信号として返されます。

送信機の構造

次の図は、QPSK Tx サブシステムの最上位モデルを示しています。

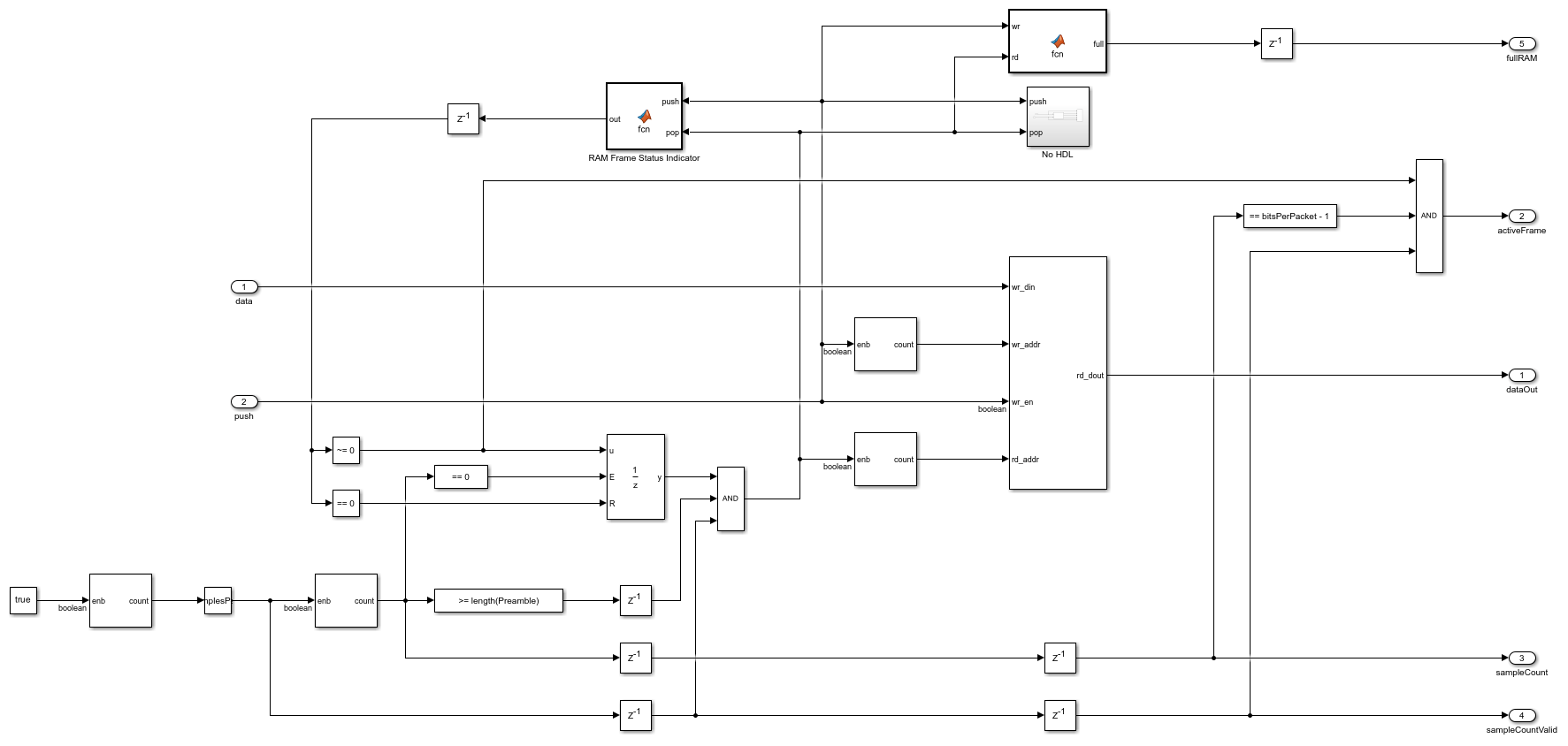

Bit Packetizer

Bit Packetizer サブシステムは、Data Bits FIFO サブシステムおよび Preamble Bits Generator サブシステムで構成されます。これは、入力データを保存し、必要なときにそれを読み取ります。また、これは、送信機が入力ビットを受け入れる準備ができると、dataReady 信号を生成してそれを示します。

Data Bits FIFO サブシステムは、入力データ ビットを収集して RAM に格納します。RAM は 2 つのデータ パケットを収容できるため、前のデータ パケットを読み取っている間に現在のデータ パケットを格納することができます。関数 RAM Frame Status Indicator は、現在 RAM に格納されているパケットの数をカウントします。このサブシステムは、RAM に少なくとも 1 つのパケットが格納されている場合にのみ RAM からデータを読み取ります。

Preamble Bits Generator サブシステムは、RAM に少なくとも 1 つのパケットが格納されている場合、有効なプリアンブル シーケンスを出力します。そうでない場合はランダムなシーケンスを出力します。

HDL Data Scrambler

HDL Data Scrambler サブシステムは、Bits Generator サブシステムによって生成される制御信号を使用して各パケットのデータ ビットをスクランブルします。

QPSK 変調器

QPSK Modulator サブシステムは、QPSK Modulator Basebandブロックを使用してプリアンブル ビットとデータ ビットを変調することで QPSK シンボルを生成します。次の表に示すグレイ マッピングが使用されます。

Bits Mapping

____ _________________

00 0.70711+0.70711i

01 -0.70711+0.70711i

11 -0.70711-0.70711i

10 0.70711-0.70711i

RRC Transmit Filter

RRC Transmit Filter サブシステムは、シンボル レートの 4 倍のクロック レートで入力信号を受け入れ、有効なシンボルの後ろに 3 つのゼロを追加します。この有効な離散信号は、単位遅延が有効になっているブロックを使用して連続信号に変換されます。これは、4 倍にアップサンプリングされるのと等価です。このアップサンプリングされた信号が、RRC インパルス応答をもつDiscrete FIR Filter (DSP HDL Toolbox)ブロックに渡され、送信機の波形がパルス整形されます。QPSK 受信機の受信フィルターで、この送信フィルターに対する整合フィルターが形成されます。

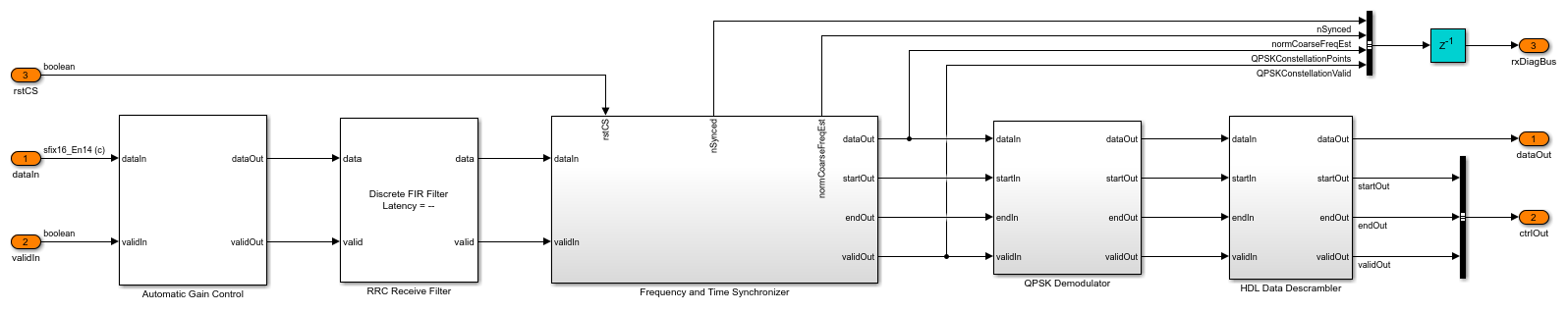

受信機の構造

次の図は、QPSK Rx サブシステムの最上位の概要を示しています。

Automatic Gain Control

シンボル同期装置とキャリア同期装置の位相同期回路 (PLL) の性能には入力信号の振幅が影響するため、それらの前に Automatic Gain Control サブシステムを配置しています。振幅の二乗の出力を AGC の基準と比較して振幅の誤差が生成されます。この誤差にループ ゲインを乗算して積分器を通過させることで、必要なゲインが計算されます。結果のゲインに AGC の入力を乗算して AGC の出力が生成されます。詳細については、[ 1 ] の Chapter 9.5 を参照してください。

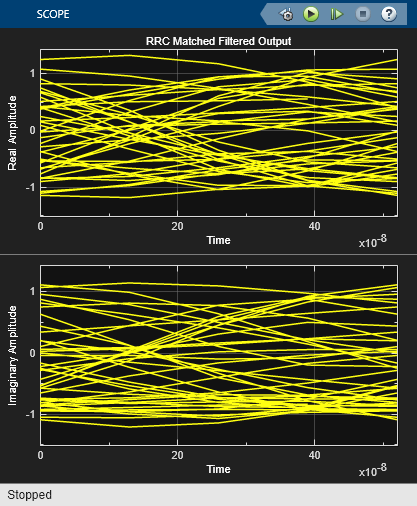

RRC Receive Filter

RRC Receive Filter は、送信機でパルス整形に使用されたフィルターの整合フィルター係数をもつDiscrete FIR Filter (DSP HDL Toolbox)ブロックです。RRC 整合フィルター処理により、波形のアイ ダイアグラムのアイ開口が最大になる時点においてゼロ ISI 特性となる RC パルス整形波形が生成されます。また、整合フィルター処理の過程で、フィルター出力の信号のノイズ パワーに対する割合 (SNR) が最大化されます。

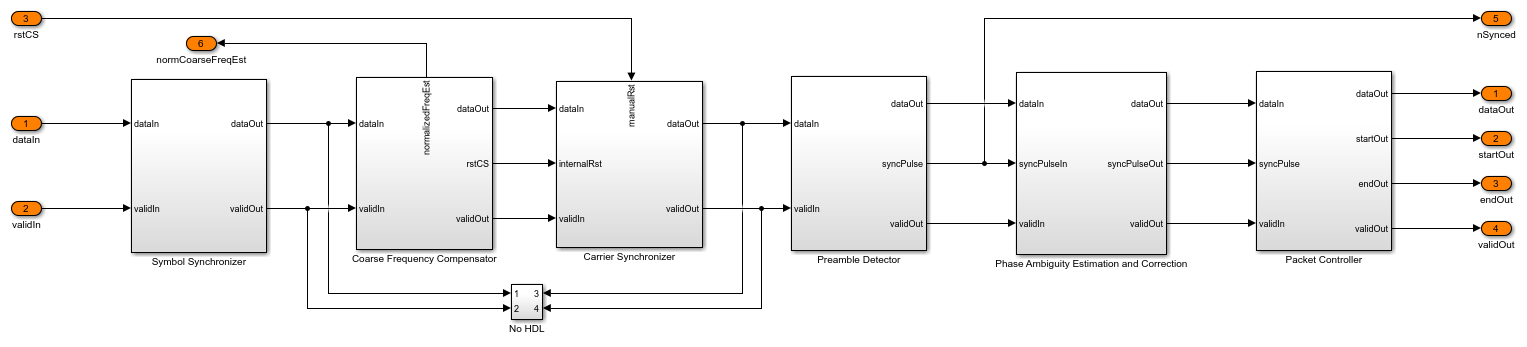

Frequency and Time Synchronizer

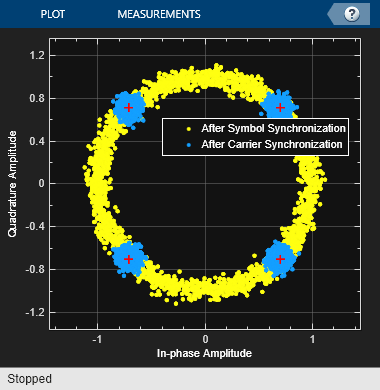

Frequency and Time Synchronizer サブシステムは、シンボル同期、大まかな周波数補正、搬送波同期、およびパケット同期用のプリアンブル検出を実行します。また、搬送波同期で補正されずに残る位相不確定性を推定して解決します。

Symbol Synchronizer サブシステムは PLL ベースの実装です。[ 1 ] の Chapter 8.5 で説明されているように、最適な時点 (アイ開口が最大になる時点) でサンプルを生成します。このサブシステムは 4 つの入力サンプルごとに 1 つの出力サンプルを生成します。Interpolation Filter サブシステムは、[1] の Chapter 8.4.2 で説明されているハードウェア リソース効率に優れた Farrow 構造をもつ区分的な放物線内挿器を実装します。Farrow の係数は Table 8.4.1 (係数の自由パラメーター ![]() は 0.5) に示されています。このフィルターは入力波形に非整数遅延を導入します。

は 0.5) に示されています。このフィルターは入力波形に非整数遅延を導入します。Gardner TED サブシステムは、ガードナー法によるタイミング誤差検出器を実装します。タイミング誤差検出器については、[ 1 ] の Chapter 8.4.1 で説明されています。Loop Filter サブシステムでタイミング誤差がフィルター処理され、そのタイミング誤差が Interpolation Control 関数ブロックに渡されます。このブロックは、[ 1 ] の Chapter 8.4.3 で説明されている剰余 1 の減算カウンターを実装することで、ループ フィルターでフィルター処理されたタイミング誤差に基づいて非整数遅延を計算し、最適なサンプリング時点で内挿を生成します。ストローブ信号が存在する場合、Rate Handle サブシステムによってサンプルが選択されて FIFO に格納されます。このサンプルは、シンボル同期前のアイ ダイアグラムのアイ開口が最大になる時点に対応します。

Coarse Frequency Compensator サブシステムは、Raise Power to 4 サブシステムで入力シーケンスを 4 のべき乗にします。これによって、入力シーケンスの QPSK 位相マッピングの依存関係は排除されますが、推定範囲が 4 分の 1 になります。このシーケンスが Coarse Frequency Estimator サブシステムにストリーミングされます。4 のべき乗に起因する係数 4 を削除し、正規化された大まかな周波数推定を取得するため、Coarse Frequency Estimator サブシステムから取得された推定を 4 で除算します。この推定で駆動されるNCO (DSP HDL Toolbox)ブロックにより、周波数オフセットを補正するための入力シーケンスで共役と乗算を行った複素指数位相が生成されます。

Coarse Frequency Estimator サブシステムは、差分で入力シーケンスを検出し、入力の複素周波数オフセット推定を抽出します。Integrator サブシステムにおいて、連続する 2^15 個の推定が平均化され、最終的な複素推定が得られます。Extract Frequency サブシステムで、Complex to Magnitude-Angle (DSP HDL Toolbox)ブロックによって複素推定から周波数が抽出されます。

周波数推定器で推定されるのは、正規化周波数 (シンボル レート基準) の範囲で -0.125 ~ 0.125 になります。これは、1.92 Mbaud のシンボル レートでは、周波数オフセット範囲 -240 KHz ~ 240 KHz に対応します。推定の精度については、大まかな周波数オフセット補正後の残留周波数オフセットが正規化周波数の範囲 -0.0016 ~ 0.0016 に収まるようになります。これは、1.92 Mbaud のシンボル レートでは、キャリア同期装置の PLL が周波数オフセット範囲 -3 KHz ~ 3 KHz に収束することに対応します。

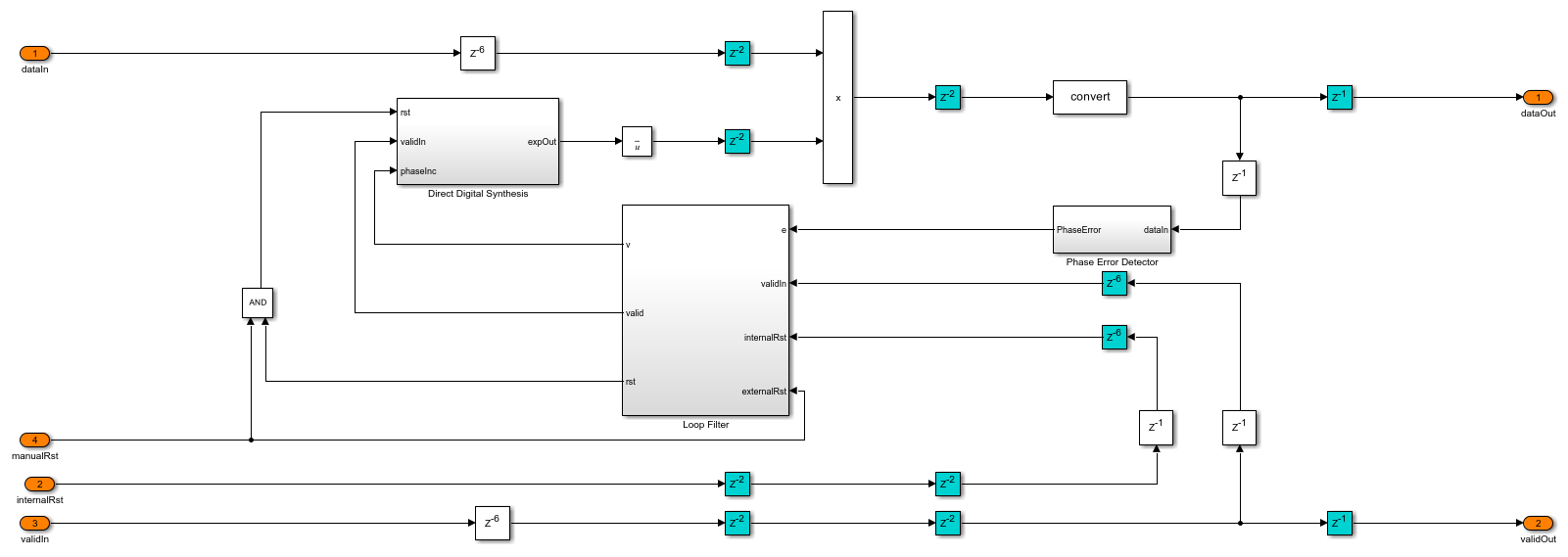

Carrier Synchronizer サブシステムは、正弦波位相誤差検出器をもつ TYPE II PLL で、45 度の動作点で動作します。位相誤差検出器については [ 1 ] の Chapter 7.2.2、設計方程式については Appendix C で説明されています。動作点がゼロの正弦波位相誤差検出器をもつ TYPE II PLL の詳しい解析については、[ 2 ] の Chapter 4 で説明されています。位相検出器の実数部と虚数部の符号関数は、4 象限のすべての角度を第 1 象限の角度 (0 ~ 90 度) に変換します。これにより、第 2 象限 (90 ~ 180 度) の 90 度、第 3 象限 (-180 ~ -90 度) の 180 度、および第 4 象限 (-90 ~ 0 度) の 270 度の角度について不確定性が生じます。位相誤差は、位相検出器の動作点 (45 度) からの偏差として計算されます。Loop Filter サブシステムの比例積分器フィルターで位相誤差がフィルター処理されます。ループ フィルターで正規化ループ帯域幅 (サンプル レートで正規化) とループ減衰係数が設定されます。既定の正規化ループ帯域幅は 0.005、既定の減衰係数は 0.7071 に設定されています。フィルター処理された誤差が位相インクリメントのソースとして Direct Digital Synthesis サブシステムに与えられます。このサブシステムでは、複素指数位相の生成にNCO (DSP HDL Toolbox)ブロックを使用します。この複素指数位相を使用して入力の周波数と位相が補正されます。直接デジタル合成の詳しい解析については、[ 1 ] の Chapter 9.2.2 で説明されています。

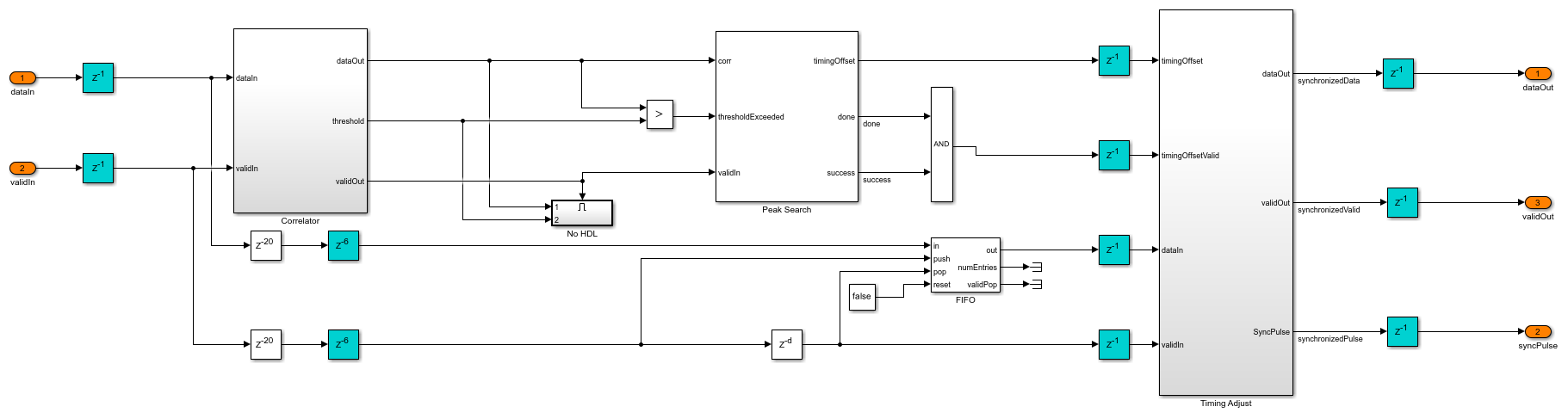

Preamble Detector サブシステムは、バーカー シーケンスを使用して入力の連続相関を実行します。この相関は、反転したバーカー シーケンスをDiscrete FIR Filter (DSP HDL Toolbox)ブロックの係数とする畳み込みとして実装されます。相関後の出力の振幅は、Correlator サブシステム内のComplex to Magnitude-Angle (DSP HDL Toolbox)ブロックを使用して求められます。相関の振幅がしきい値と比較されます。Peak Search サブシステムは、しきい値を超えた最大相関ピークの検索を 1 フレーム時間ごとに開始し、タイミング オフセットを記録します。Timing Adjust サブシステムは、パケットのタイミングをタイミング オフセットに基づいて同期し、パケット同期済みのサンプルであることを後続のサブシステムに示す "syncPulse" 信号を生成します。

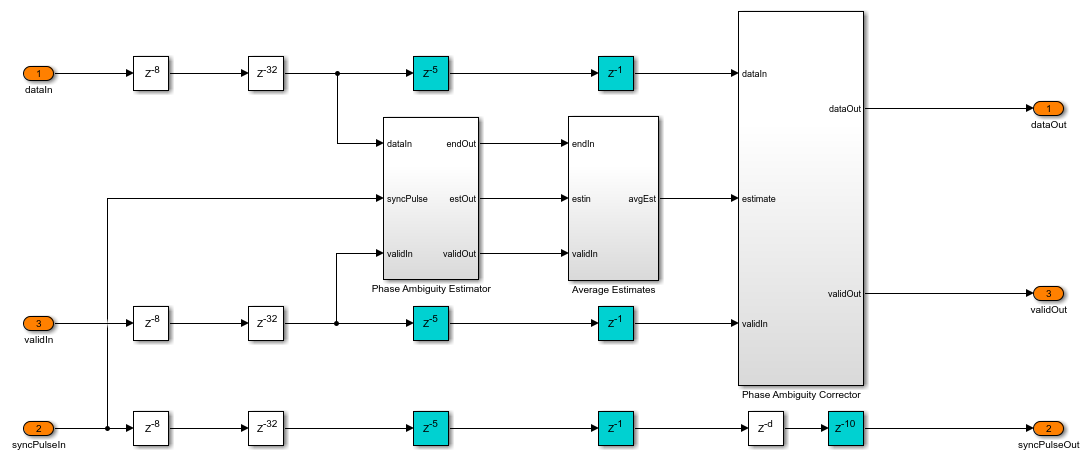

Phase Ambiguity Estimation and Correction サブシステムは、[1] の Chapter 7.7.1 で説明されているユニーク ワード方式に基づいて位相不確定性の解決を行います。この方式では、プリアンブル シーケンスを参照シーケンスとして使用します。入力のプリアンブル シーケンスで参照シーケンスの共役と乗算を行い、残留位相を位相不確定性の推定として抽出します。この推定を使用して、コンスタレーションを不確定性と反対方向に回転させることで不確定性を補正します。

Packet Controller サブシステムは、パケット境界の制御信号を生成します。

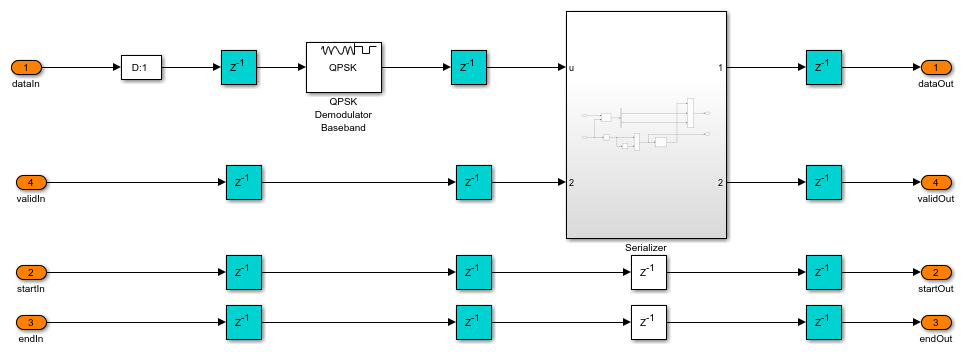

QPSK Demodulator

QPSK Demodulator サブシステムは、QPSK Demodulator Basebandブロックを使用して、パケット同期済みのシンボルを復調することでビットを生成します。

HDL Data Descrambler

HDL Data Descrambler サブシステムは、復調されたビットをデスクランブルしてユーザー ビットを生成します。このサブシステムは送信機側で使用されるスクランブラと同じです。

モデルの実行

commhdlQPSKTxRx モデルを開きます。Input Data サブシステム マスクでカスタム データを設定し、Channel サブシステム マスクでチャネル構成を設定できます。モデルを実行します。シミュレーションが終了すると、QPSKTxRxVerification スクリプトによって commhdlQPSKTxRx モデルの出力が検証されます。このスクリプトは、基準波形を生成して送信機出力と比較し、送信されたビットと受信機の復号化されたユーザー ビットを比較します。

Simulation completed Running the verification script QPSK Tx: Maximum absolute symbol error: Real:1.4496e-05 Imaginary:1.4496e-05 Maximum absolute RRC output error: Real:7.8708e-05 Imaginary:7.8708e-05 QPSK Rx: Initial frames not compared : 29 Number of packets missed = 0 out of 30 Number of packets false detected = 0 out of 30 Number of bits errored = 0 out of 67200

HDL コードの生成

HDL コードのチェックと生成を行うには、HDL Coder™ ライセンスが必要です。

QPSK Tx サブシステムと QPSK Rx サブシステムの HDL コードを生成するには、次のコマンドを使用します。

makehdl('commhdlQPSKTxRx/QPSK Tx') および makehdl('commhdlQPSKTxRx/QPSK Rx')

テスト ベンチを生成するには、次のコマンドを使用します。

makehdltb('commhdlQPSKTxRx/QPSK Tx') および makehdltb('commhdlQPSKTxRx/QPSK Rx')

テスト ベンチの生成時間はシミュレーション時間に依存します。

結果の HDL コードは、AMD® Zynq®-7000 ZC706 評価ボード用に合成されたものです。配置配線後のリソース使用状況を次の表に示します。最大動作周波数は、送信機が 320 MHz、受信機が 196 MHz です。

Resources Tx Usage Rx Usage

_______________ ________ ________

Slice Registers 250 14303

Slice LUT 137 8884

RAMB36 0 5

RAMB18 1 1

DSP48 18 118

その他の調査

次の表に示す変数を調整することで、チャネル条件を変更できます。これらの値は commhdlQPSKTxRx モデルの Channel サブシステム マスクで変更できます。

Variable Name Description

______________________ _______________________________________________________________________________________

fractionalTimingOffset Normalized timing phase offset specified in the range >= 0 and < 1

timingFrequencyOffset Timing frequency offset specified in PPM

EbN0dB Energy per information bit to single sided noise power spectral density specified in dB

CFO Carrier frequency offset specified in Hz

CPO Carrier phase offset specified in degrees

参考文献

1.Michael Rice, Digital Communications - A Discrete-Time Approach, Prentice Hall, April 2008.

2.Floyd M.Gardner, Phaselock Techniques, Third Edition, John Wiley & Sons, Inc., 2005.