HDL コード生成

Simulink® モデルと MATLAB® コードから HDL コードを生成する

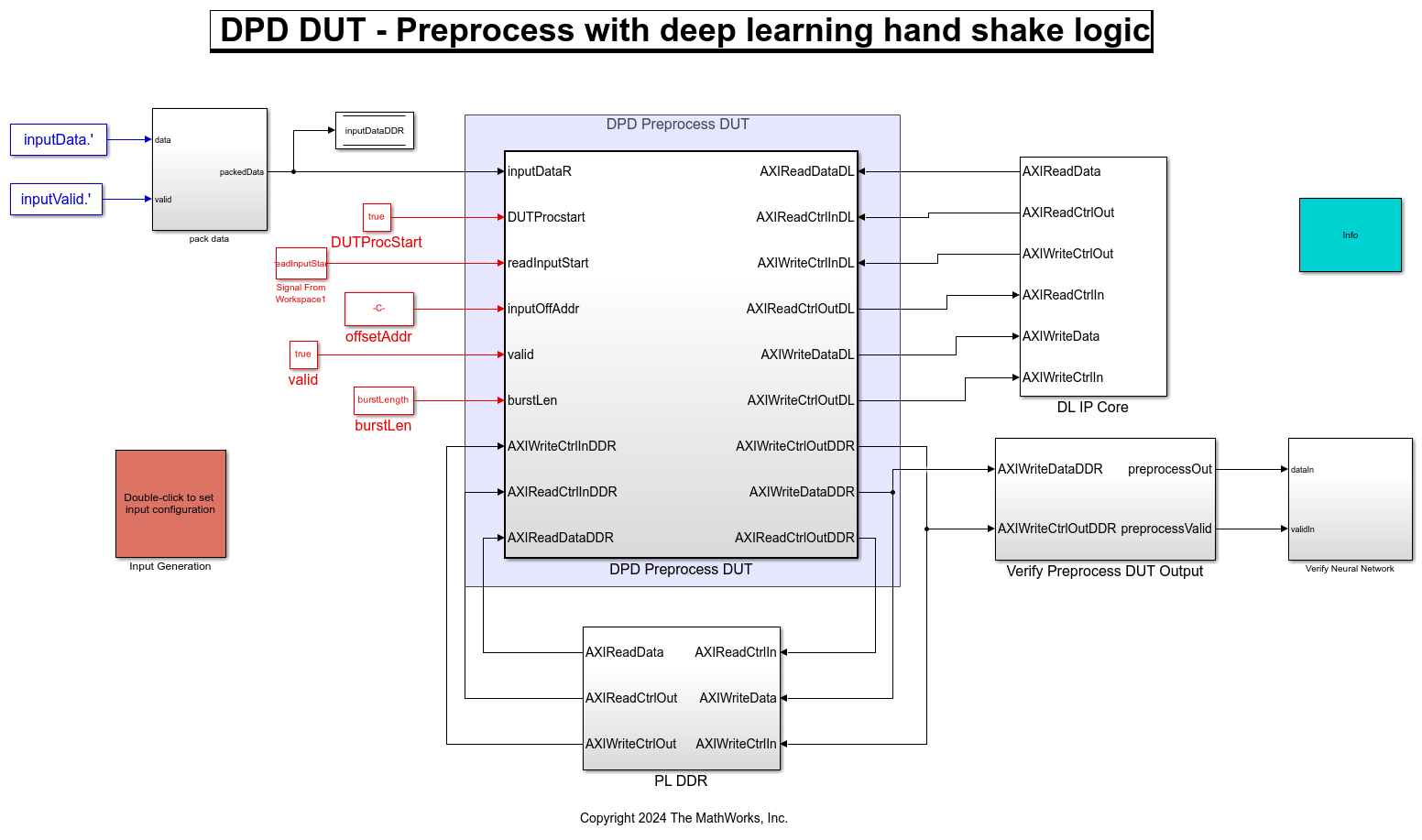

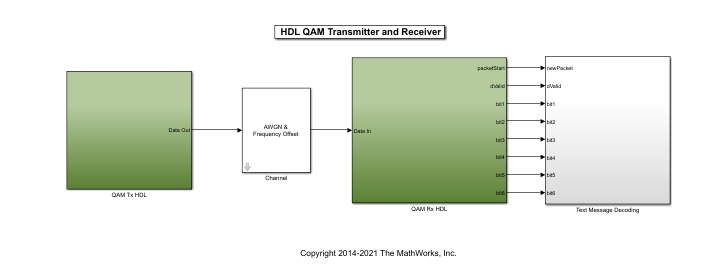

HDL Coder™ の機能を使用して、FPGA または ASIC で通信システム設計を実装できます。合成可能で移植可能な VHDL® や Verilog® のコードを生成し、生成されたコードのシミュレーションやテスト、検証をすばやく行うための VHDL や Verilog のテスト ベンチも生成できます。Simulink や MATLAB の設計からコードを生成できます。このサポートには、誤りの訂正と検出、変調、フィルター、数学演算と信号処理のほか、NCO (DSP HDL Toolbox) ブロックなど、リソースの使用とパフォーマンスについて最適化されたアルゴリズムが含まれています。HDL コードを生成する方法の基本的な例については、プログラミング可能な FPGA 用 FIR フィルターを参照してください。

Simulink または MATLAB で設計をデバッグするには、ロジック アナライザーの波形ビューアーを使用します。

トピック

- HDL コード生成をサポートするブロックの検索

Simulink ライブラリ ブラウザーおよびドキュメンテーション内で、HDL コード生成をサポートするブロックを検索。

- ASIC、FPGA、および SoC の無線通信の設計

Wireless HDL Toolbox™ ブロックを使用したハードウェアの無線通信アルゴリズムの設計。

Simulink 可視化ツール

| ロジック アナライザー | 時間の経過に沿った遷移と状態の可視化、測定および解析 |