このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

イーサネットベースの AXI マネージャーを使用して FPGA メモリにアクセスする

この例では、イーサネットベースの AXI マネージャーを使用して、異なる UDP ポートを介して FPGA の内部メモリと外部メモリにアクセスする方法を示します。FPGA には、DDR メモリと BRAM にアクセスするための Xilinx® DDR メモリ コントローラと BRAM コントローラが存在します。これらのメモリ コントローラは、FPGA 内の他のコンポーネントによる書き込みおよび読み取り操作用の AXI4 スレーブ インターフェイスを提供します。イーサネットベースの AXI マネージャーは、FPGA 内の AXI 従属 IP にアクセスするために使用できる AXI マネージャー コンポーネントを提供します。この例では、イーサネットベースの AXI マネージャーを Xilinx Vivado® プロジェクトに統合する方法と、MATLAB® を使用して DDR メモリと BRAM に書き込みおよび読み取りを行う方法を示します。

要件

Xilinx Vivado Design Suite(サポートされているバージョンはに記載されています)

Xilinx Kintex®-7 KC705 評価キット

HDL Verifier™ Support Package for Xilinx FPGA Boards

イーサネットケーブルとJTAGケーブル

設定

1. FPGAボードをセットアップします。イーサネット ケーブルと JTAG ケーブルを介して Xilinx KC705 ボードをホスト コンピューターに接続します。JTAG ケーブルはデバイスのプログラミングに使用されます。

2. MATLAB で例を準備します。Xilinx Vivado ツール パスを設定します。コマンドを実行するときに独自の Xilinx Vivado インストール パスを使用します。

hdlsetuptoolpath('ToolName','Xilinx Vivado', ...

'ToolPath','C:\Xilinx\Vivado\2020.2\bin\vivado.bat');この例では、Vivado プロジェクトを作成します。このプロジェクトには、IP インテグレーターのブロック図と制約ファイルが含まれています。

system('vivado -mode batch -source createProjectEthAxim.tcl')このコマンドの実行には約 1 分かかります。実行が完了すると、現在のディレクトリに ethernetaximaster.xpr という名前の Vivado プロジェクトが表示されます。

3. Vivado IP を使用して Vivado プロジェクトを構成します。Vivado IP インテグレーター内で UDP AXI Manager IP を使用するには、IP を含むフォルダーを Vivado プロジェクトの IP リポジトリ パス設定に追加します。MATLAB でこのコマンドを実行して、プロジェクトへのパスを追加します。

setupAXIManagerForVivado ethernetaximaster.xpr

ファイル ブラウザーでプロジェクトをダブルクリックするか、MATLAB でこのコマンドを実行して、生成された Vivado プロジェクトを GUI モードで開きます。

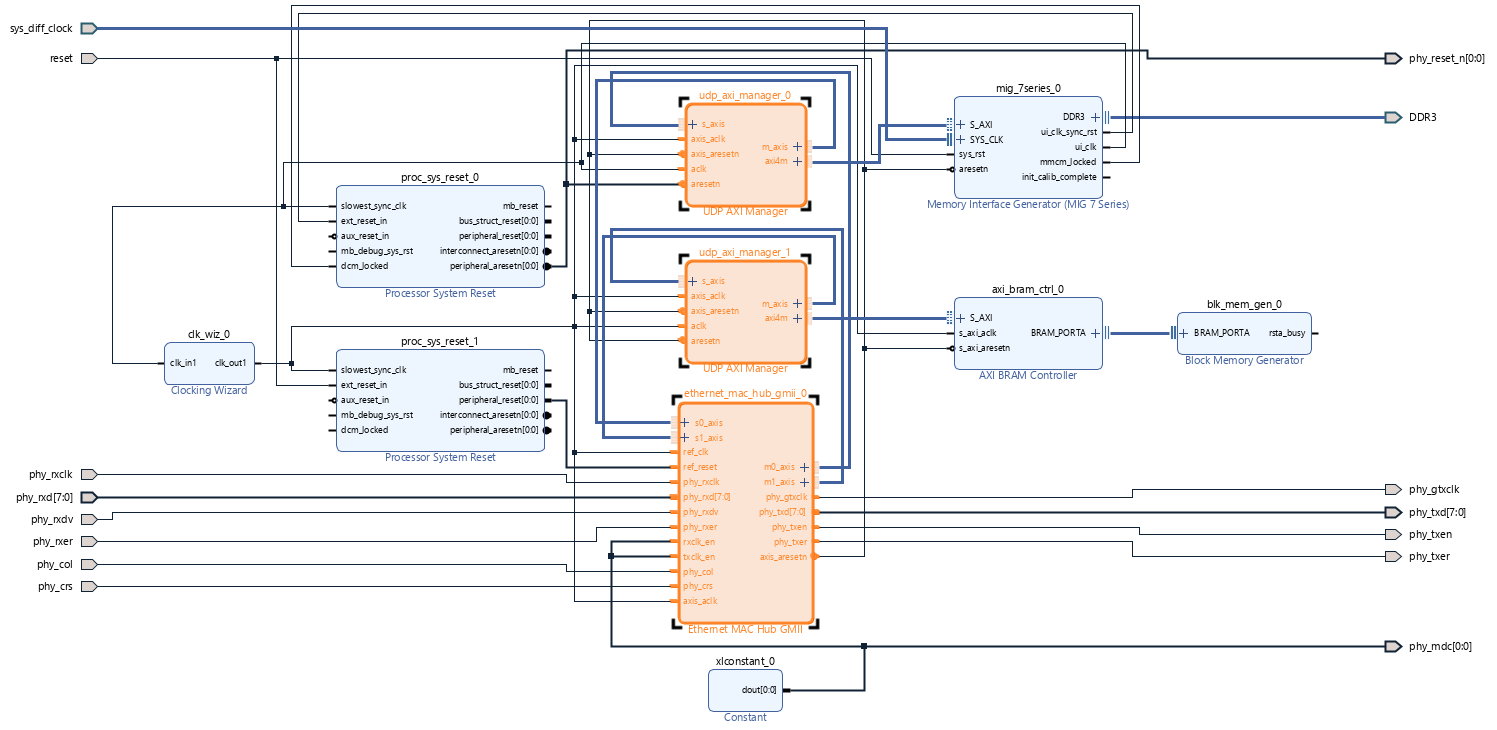

system('vivado ethernetaximaster.xpr &')4. Vivado GUI で、ブロック ダイアグラム デザイン ファイル design_1.bd を開きます。ブロック図はソース ファイルのサブウィンドウにあります。Ethernet MAC Hub GMII および UDP AXI Manager IP を FPGA デザインに追加します。Ethernet MAC Hub GMII IP のデフォルトのターゲット IP アドレスは 192.168.0.2 で、デフォルトの UDP ポート値は 50101 です。Ethernet MAC Hub の AXI Stream チャネル数を 2 に変更します。これらの値は、ブロック デザインで ethernet_mac_hub_gmii_0 IP をダブルクリックすることで変更できます。この図に示すように、ethernet_mac_hub_gmii_0 パラメータを変更します。

この図に示すように、IP 間の接続を作成します。DDR メモリと BRAM には、それぞれ UDP ポート 50101 と 50102 を介してアクセスできます。

この図に示すように、mig_7series_0 (DDR コントローラ) と axi_bram_ctrl_0 (BRAM コントローラ) のアドレスをそれぞれ 0x0000_0000 と 0x1000_0000 に設定します。

あるいは、Vivado で Tcl コマンドを実行して上記のセットアップ手順を完了することもできます。

source ./modifyDesignEthAxim.tcl

5. FPGA プログラミング ファイルを生成し、FPGA をプログラムします。Vivado ウィンドウで Generate Bitstream をクリックして、FPGA プログラミング ファイルを生成します。Vivado では、次の手順に進む前にプロジェクトを保存するように求められる場合があります。Vivado がビットストリーム ファイルを生成するには、約 5 ~ 10 分かかります。

Vivado がビットストリームを生成した後、FPGA ボードが Digilent® JTAG および Ethernet ケーブルで接続されていることを確認します。MATLAB でこのコマンドを実行して FPGA をプログラムします。

filProgramFPGA('Xilinx Vivado','ethernetaximaster.runs\impl_1\design_1.bit',1)6. ホスト ネットワーク接続がハードウェア ボードと同じサブネット上にあることを確認してください。この例では、ホスト ネットワーク IP アドレスを 192.168.0.x に設定します。ここで、x は 2 を除く 1 ~ 255 の範囲の任意の数字です。この例では、192.168.0.2 がハードウェア ボードの IP アドレスです。

FPGAの書き込みおよび読み取り操作

FPGA をプログラミングした後、UDP AXI マネージャー IP に接続されている AXI 下位デバイスに対して書き込みと読み取りを行うことができます。この例では、FPGA と BRAM に接続された DDR メモリにデータを書き込み、次にデータを MATLAB に取得します。

DDR メモリへの書き込みと読み取りを行うために、MATLAB に AXI マネージャー オブジェクトを作成します。デフォルトのポート アドレスは 50101 です。単一の場所に書き込み、同じ場所からデータを読み取ります。この場合、読み戻されるデータは 100 です。

hDDR = aximanager('Xilinx','interface','PLEthernet', ...

'DeviceAddress','192.168.0.2');

writememory(hDDR,'00000000',100);

readmemory(hDDR,'00000000',1);AXI マネージャー オブジェクトを解放して、他の UDP ポートを介して通信を開きます。

release(hDDR);

BRAM への書き込みと読み取りを行うために、異なる UDP ポートを持つ新しい AXI マネージャー オブジェクトを作成します。単一の場所に書き込み、同じ場所からデータを読み取ります。この場合、読み戻されるデータは 1000 です。

hBRAM = aximanager('Xilinx','interface','PLEthernet', ...

'DeviceAddress','192.168.0.2','Port','50102');

writememory(hBRAM,'10000000',1000);

readmemory(hBRAM,'10000000',1);

release(hBRAM);参考

aximanager | writememory | readmemory | release