このページは機械翻訳を使用して翻訳されました。最新版の英語を参照するには、ここをクリックします。

AXI Manager

MATLAB® または Simulink® から FPGA ボード上の AXI 従属メモリにアクセスする

メモ

MATLAB AXI マスターの名前が AXI manager に変更されました。ソフトウェアとドキュメントでは、「マスター」と「スレーブ」という用語がそれぞれ「マネージャー」と「従属」に置き換えられます。

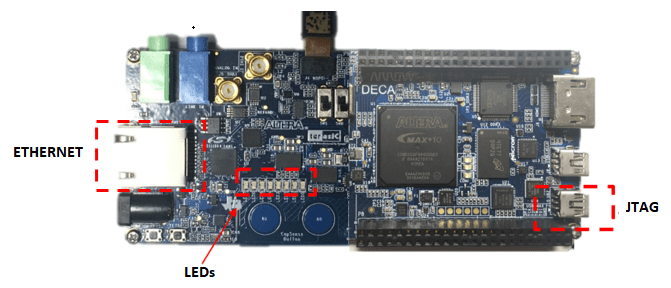

FPGA デザインで AXI manager IP を使用して、MATLAB または Simulink からオンボード メモリの場所にアクセスします。この IP はボード上の下位のメモリ位置に接続します。IP は、JTAG、PCI Express®、または PL イーサネット インターフェイスを介して、MATLAB または Simulink からの読み取りおよび書き込みコマンドにも応答します。

関数

setupAXIManagerForQuartus | Quartus プロジェクトに AXI マネージャー IP パスを追加します |

readmemory | AXI4メモリマップされた下位からデータを読み取る |

writememory | AXI4メモリマップされた下位にデータを書き込む |

release | JTAGまたはイーサネットケーブルリソースを解放する |

copyImageToHostSDCardPath | ボード固有のSDカードイメージファイルをホストのSDカードの場所にコピーする |

loadBitstream | カスタム FPGA ビットストリームと対応する DTB ファイルをターゲット SoC デバイスにロードします。 |

オブジェクト

aximanager | MATLAB からの FPGA ボード上のメモリ位置の読み取りと書き込み |

ブロック

| AXI Manager Read | Simulink から FPGA ボード上のメモリ位置を読み取る |

| AXI Manager Write | Simulink から FPGA ボード上のメモリ位置を書き込む |

トピック

- AXI Manager のセットアップ

MATLAB または Simulink から FPGA ボード上のメモリマップされた場所にアクセスするための高レベルの手順。

- イーサネットAXIマネージャー

Ethernet AXI マネージャーを統合および構成します。

- PCI Express AXI マネージャー

PCI Express 経由で AXI マネージャー IP を統合および構成します。

- Simulink を使用して FPGA の場所にアクセスする

Simulink から FPGA ボード上のメモリマップされた場所にアクセスします。