Stateflow HDL コード生成の紹介

Stateflow® チャートは、階層型有限ステート マシン (FSM) 理論、流れ図の表記法、および状態遷移図を使用して複雑なシステム動作を記述します。

Stateflow チャートを使用して、有限ステート マシンまたは ASIC や FPGA 用の複雑な制御アルゴリズムをモデル化できます。モデルが設計要件を満たす場合、設計を実装する VHDL®、Verilog®、または SystemVerilog のコードを生成します。生成された HDL コードは業界標準ツールを使用してシミュレーションと合成ができ、その後システム設計を FPGA および ASIC にマッピングできます。有限ステート マシン用の HDL コードを生成する方法の詳細については、Mealy および Moore 有限ステート マシンでの HDL 生成を参照してください。

Stateflow チャートからの HDL コードの生成

この例では、Stateflow チャートを含むサブシステムの HDL コードを生成する方法を示します。

モデルを開く

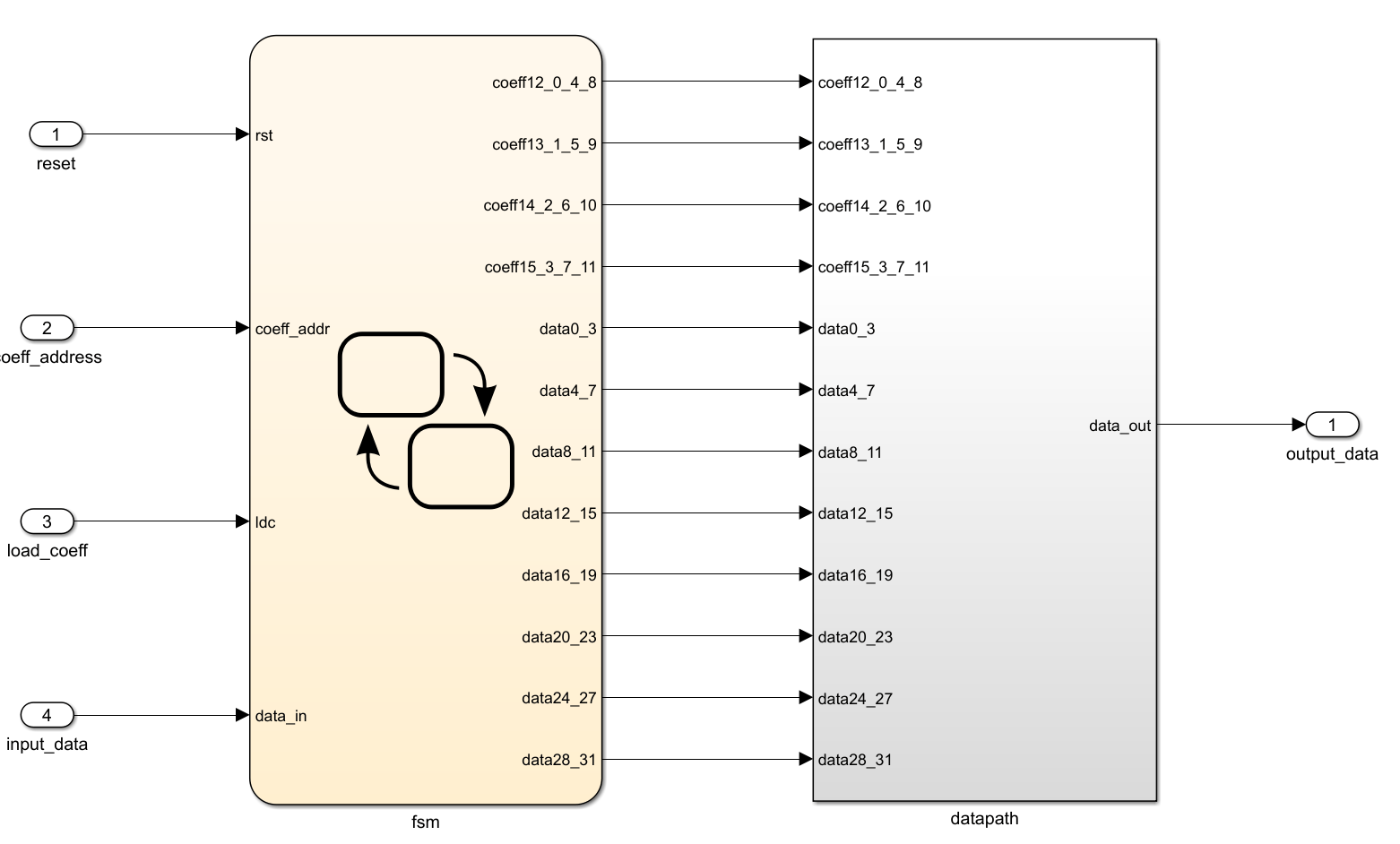

モデル hdlcodercfir は、パイプライン化された構成可能な対称 FIR フィルターを実装します。

モデルを開くには、MATLAB コマンド ウィンドウで次のコマンドを実行します。

open_system("hdlcodercfir");

サブシステム内部の Stateflow チャートでリソース共有を制御しています。サブシステムを開くには、cfir_system をダブルクリックします。

チャートのプロパティの構成

1. Stateflow チャートを開くには、fsm チャートをダブルクリックします。

2. Simulink ツールストリップの [モデル化] タブで [チャート プロパティ] をクリックします。HDL コードを生成するには、[アクション言語] プロパティが C、[ステート マシン タイプ] プロパティが Classic でなければなりません。

3. チャートの初期化後に直ちにチャートを更新するために、[初期化時に指定されたチャートを実行 (入力)] プロパティを有効にします。リセット アクションでは組み合わせ論理に関連するレイテンシを管理できないため、初期化アクションで算術演算は実行できません。詳細については、チャートの初期化実行 (Stateflow)を参照してください。

4. [チャート実行ごとに出力を初期化] プロパティを選択します。このプロパティをオフにすると、生成される HDL コードにステート マシンの出力値のための追加のレジスタが含まれます。

5. [OK] をクリックします。

サブシステムの HDL コードの生成

HDL コードを生成する前に、生成コードでトレーサビリティを有効にします。トレーサビリティを有効にすると、コード ジェネレーターで双方向トレーサビリティを備えたコードが生成されます。生成コードは [HDL コード] ペインまたは HTML コード生成レポートで確認できます。トレース可能な生成コードを使用して、生成コードが設計要件を満たすことを検証できます。生成コードでトレーサビリティを有効にするには、以下を行います。

1. [アプリ] タブで、[HDL Coder] をクリックします。

2. [HDL コード] タブで、[設定] をクリックします。

3. [HDL コード生成]、[レポート] ペインで、[トレーサビリティ レポートの生成] パラメーターを選択します。既定では、コード ジェネレーターは、ラインレベルのスタイルを使用してトレーサビリティを生成します。[トレーサビリティ スタイル] パラメーターを変更してスタイルをカスタマイズできます。

4. [OK] をクリックします。

5. Stateflow チャートを含むサブシステムの HDL コードを生成するには、[HDL コード] タブで [HDL コードを生成] をクリックします。

6. HTML レポートまたは [HDL コード] ペインで生成コードを確認します。HTML レポートに含まれる他のレポートから、生成コードに関する洞察が得られます。

[HDL コード] ペインを使用すると、対応する Stateflow 要素の生成コードに移動してトレースできます。たとえば、Stateflow チャートで idle ステートを選択すると、HDL Coder により、その生成コードが [HDL コード] ペインで強調表示されます。

サブシステムのテスト ベンチの生成

cfir_system サブシステムのテスト ベンチを生成するには、[HDL コード] タブで [テストベンチの生成] をクリックします。

Stateflow ブロックのレイテンシ

最適化やブロック実装によってモデルにレイテンシが導入される場合、Stateflow ブロックに関連する合計レイテンシがブロックの出力で結合されます。最適化要求や特定のブロック アーキテクチャの実装が原因でレイテンシを導入するブロックの詳細な情報は、[遅延の均衡化] 最適化レポートで確認できます。詳細については、HDL Coder での遅延の均衡化の理解を参照してください。

たとえば、次の図に示す Stateflow チャートでは、HDL ブロック プロパティ [DistributedPipelining] を有効にし、HDL ブロック プロパティ [OutputPipeline] を 8 に設定しています。これらの HDL 最適化により、HDL Coder™ でブロックに 8 サイクルのレイテンシが導入されます。最適化が原因で導入されるレイテンシの詳細な情報を確認するには、モデルの最適化レポートを生成し、[遅延の均衡化] レポートを確認します。

Stateflow ブロックの最適化

Stateflow ブロックに以下の最適化を適用して、生成コードの速度と面積を最適化できます。

制限

HDL コード生成では、メッセージが含まれる Stateflow ブロックはサポートされません。

モデル内でのチャートの位置

チャートから HDL コードを生成するには、チャートが Simulink® サブシステムの一部でなければなりません。コードを生成するチャートがモデルのルート レベルにある場合、サブシステム内にチャートを組み込み、関連する信号をサブシステムの入力と出力に接続します。

データ型

コード ジェネレーターは、次の MATLAB® データ型をチャート内でサポートします。

符号付き整数と符号なし整数

固定小数点

ネイティブ浮動小数点

boolean

列挙型

メモ

コード ジェネレーターでは、条件付きでトリガーされるか有効化される Stateflow チャートや Moore チャートでのネイティブ浮動小数点データ型はサポートされません。

single および double のデータ型を使用する場合、HDL Coder は HDL コード内で実数データ型を生成します。ModelSim™ などのサードパーティ製シミュレーターを使用して、コードのシミュレーションと検証を実行できます。

インポートされるコード

チャートは完全に自己完結型でなければなりません。次の制限が適用されます。

minとmaxを除き、それ以外の MATLAB 関数は呼び出さないでください。MATLAB System object™ は Chart ブロックで使用しないでください。

MATLAB ワークスペース データは使用しないでください。

C の数学関数は呼び出さないでください。HDL には C の数学ライブラリに対応するライブラリはありません。

[C 言語のビット演算が可能] プロパティをオフにしている場合、指数演算子 (

^) は使用しないでください。指数演算子は C の数学ライブラリの関数powを使用します。カスタム コードは含めないでください。[コンフィギュレーション パラメーター] ダイアログ ボックスの [シミュレーション ターゲット] 、 [カスタム コード] ペインの情報はコード ジェネレーターで無視されます。

チャート間で Data Store Memory ブロックを使用してデータを共有しないでください。グローバル データは HDL ではサポートされないため、HDL Coder で HDL にマッピングされません。

調整可能なパラメーターのベクトル

HDL コード生成では、調整可能なパラメーターのベクトルを Chart ブロックのデータ型として使用することはサポートされていません。

入力イベントと出力イベント

HDL Coder では、Stateflow チャートでの入力イベントと出力イベントの使用がサポートされますが、次の制約があります。

定義および使用できる入力イベントの数は Stateflow チャートごとに 1 つだけです。出力イベントの数に制限はありません。

コード ジェネレーターでは、入力イベントが 1 つで出力端子の初期値が非ゼロのチャートについては HDL コード生成はサポートされません。

入力イベントと出力イベントはいずれもエッジトリガー イベントでなければなりません。

入力イベントと出力イベントの詳細については、入力イベントの送信による Stateflow チャートのアクティブ化 (Stateflow)および出力イベントの送信による Simulink ブロックのアクティブ化 (Stateflow)を参照してください。

メッセージ

Stateflow メッセージは HDL コード生成ではサポートされていません。

ループ

HDL コード生成用のチャートでは、for ループを除き、それ以外のループは明示的に使用しないでください。for ループについては、次の制限が適用されます。

ループ カウンター変数のデータ型は

int32でなければなりません。HDL Coder では、定数で制限されたループのみがサポートされます。

for ループの例 sf_for は、グラフィカル関数を使用する for ループの設計パターンを示しています。

その他の制限

汎用の逐次プログラミング言語の一部の機能が HDL コードでサポートされないため、Stateflow チャートは次の追加の制限を満たさなければなりません。

Atomic サブチャートのインスタンスごとに別個のコピーを作成する必要があります。詳細については、Atomic サブチャートから通常のサブチャートへの変換 (Stateflow)を参照してください。

Simulink Function ブロックの HDL コードは生成しないでください。

チャートでローカル イベントは定義しないでください。

次の暗黙的なイベントは使用しないでください。

enterexitchange

時相論理を使用する場合は、次の暗黙的なイベントを使用できます。

wakeuptick

グラフィカル関数による再帰は使用しないでください。HDL Coder では再帰はサポートされていません。

構造化されていないコードの使用は避けてください。構造化されていないコードをチャートにおいて遷移フロー図およびグラフィカル関数の形式で使用することは可能ですが、使用すると

gotoステートメントと複数の関数の return ステートメントが生成されます。HDL ではgotoステートメントまたは複数の関数の return ステートメントはサポートされません。[チャート実行ごとに出力を初期化] チャート オプションをオフにしている場合、出力端子からの読み取りは行わないでください。

データ ストア メモリ オブジェクトは使用しないでください。

ポインター (

&) 演算子または間接参照 (*) 演算子は使用しないでください。ポインター演算とアドレス演算 (Stateflow)を参照してください。シミュレーション中に実行時オーバーフロー エラーがチャートから返される場合、データ範囲エラーのチェックを無効にしてチャートの HDL コードを生成することができます。この場合、生成された HDL コードから取得された一部の結果が、シミュレーションの結果に対してビットトゥルーにならないことがあります。オーバーフローのチェックを有効にし、モデルでオーバーフロー状態を解消することをお勧めします。

参考

State Transition Table (Stateflow) | Truth Table (Stateflow) | Sequence Viewer (Stateflow)