Mealy および Moore 有限ステート マシンでの HDL 生成

Stateflow® チャートは、3 つのタイプのステート マシンのモデル化をサポートしています。

Classic (既定の設定)

Mealy

Moore

HDL コードの生成には、Mealy タイプまたは Moore タイプのステート マシンを使用します。Mealy および Moore ステート マシンは、次の点で異なっています。

Mealy ステート マシンの出力は、現在のステートと入力の関数。

Moore ステート マシンの出力は、現在のステートのみの関数。

Mealy または Moore チャートを Classic チャートの代替として使用する主な利点は、次のとおりです。

Moore チャートは、Classic チャートよりも効率的なコードを生成できる。

コンパイル時に、Mealy および Moore チャートは正式な定義とセマンティクス ルールに一致しているか検証され、違反は報告される。

チャートの HDL コード生成ガイドラインの詳細については、Chart (Stateflow) ブロックを参照してください。

Moore 有限ステート マシン用の HDL コードの生成

この例は、MATLAB® をアクション言語として使用する Moore ステート マシンの Stateflow チャートを示しています。

モデルを開く

hdlcoder_fsm_mealy_moore モデルを読み込みます。hdlcoder_fsm_mealy_moore 内の Moore サブシステムには、Moore ステート マシンをモデル化する Stateflow チャート Moore_Chart が含まれています。Moore_Chart を開くには、次のコマンドを実行します。

load_system('hdlcoder_fsm_mealy_moore.slx'); open_system('hdlcoder_fsm_mealy_moore/Moore/Moore_Chart');

Moore ステート マシンをモデル化するチャートの HDL コードを生成する場合は、次の条件が適用されます。

チャートが、Chart ブロックで説明されているコード生成の一般的な要件を満たしていなければなりません。

アクションが発生するのはステートのみでなければなりません。これらはラベル付けされていないアクションでなければなりません。出力計算は入力ではなくステートのみに依存するため、Moore アクションは、ステートと関連付けられなければなりません。タイム ステップ

tのアクティブ ステートの構成によって出力が決まります。チャートが時間tに起動したときにステートSがアクティブな場合、ステートSは時間t+1までアクティブなままかどうかに関係なく、出力に関与します。

Simulink® 関数を呼び出さないでください。この制限によって、出力が入力に依存するために HDL コード ジェネレーターでの検証が困難になるのを防ぎます。

[チャート実行ごとに出力を初期化] パラメーターを無効にすると、生成される HDL コードにステート マシンの出力値のための追加のレジスタが含まれます。

Stateflow チャートの HDL ブロック プロパティ [ClockDrivenOutput] を

[on]に設定して、Moore チャートのクロック駆動の出力を有効にできます。詳細については、Stateflow チャートを使用した HDL コード生成に関するガイドラインを参照してください。

Mealy 有限ステート マシン用の HDL の生成

この例は、MATLAB をアクション言語として使用する Mealy ステート マシンをモデル化する Stateflow チャートを示しています。HDL Coder™ を使用して Stateflow の HDL コードを生成することもできます。

モデルを開く

hdlcoder_fsm_mealy_moore モデルを読み込みます。hdlcoder_fsm_mealy_moore 内の Mealy サブシステムには、Mealy ステート マシンをモデル化する Stateflow チャート Mealy_Chart が含まれています。Mealy_Chart を開くには、次のコマンドを実行します。

load_system('hdlcoder_fsm_mealy_moore.slx'); open_system('hdlcoder_fsm_mealy_moore/Mealy/Mealy_Chart');

Mealy ステート マシンをモデル化するチャートの HDL コードを生成する場合は、次の条件が適用されます。

チャートが、Chart ブロックで説明されているコード生成の一般的な要件を満たしていなければなりません。

アクションが内部遷移と外部遷移のみに関連付けられていなければなりません。

[チャート実行ごとに出力を初期化] パラメーターを無効にすると、生成される HDL コードにステート マシンの出力値のための追加のレジスタが含まれます。

Mealy のアクションは遷移に関連付けられます。Mealy マシンでは、入力値の変更により出力計算が駆動されます。この出力の入力への依存は、Mealy マシンと Moore マシンの正式な定義を区別する基本的な要素となっています。アクションが遷移の結果発生するという要件は、Mealy セマンティクスを適用するうえで、必須というよりは、ある程度様式的といえます。どのマシン タイプでも遷移の条件は基本的に入力条件であるため、どちらのタイプでも出力計算は最終的に入力条件に従うことになります。

Mealy チャートの生成される HDL コード

次のコードは、Mealy チャート用に生成された Verilog® コードです。

always @(posedge clk or posedge reset) begin : Mealy_Chart_1_process if (reset == 1'b1) begin is_Mealy_Chart <= is_Mealy_Chart_IN_S0; end else begin if (enb) begin is_Mealy_Chart <= is_Mealy_Chart_next; end end end

always @(is_Mealy_Chart, u) begin is_Mealy_Chart_next = is_Mealy_Chart; y_1 = 2'b00; case ( is_Mealy_Chart) is_Mealy_Chart_IN_S0 : begin if (u == 8'sb00000001) begin y_1 = 2'b00; is_Mealy_Chart_next = is_Mealy_Chart_IN_S1; end end is_Mealy_Chart_IN_S1 : begin if (u == 8'sb00000001) begin y_1 = 2'b01; is_Mealy_Chart_next = is_Mealy_Chart_IN_S2; end end is_Mealy_Chart_IN_S2 : begin if (u == 8'sb00000001) begin y_1 = 2'b10; is_Mealy_Chart_next = is_Mealy_Chart_IN_S3; end end default : begin if (u == 8'sb00000001) begin y_1 = 2'b11; is_Mealy_Chart_next = is_Mealy_Chart_IN_S0; end end endcase end

assign y = y_1;

チャート実行ごとに出力を初期化

Mealy チャートと Moore チャートには、出力信号がステートまたは遷移によって駆動されない場合に出力信号を初期値に戻すためのオプションがあります。この動作は、[チャート実行ごとに出力を初期化] パラメーターをオンにすると有効になります。このパラメーターをオフにすると、生成される HDL コードにステート マシンの出力値を格納するための追加のレジスタが含まれます。

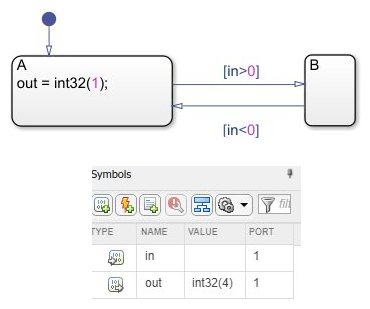

次の図は、2 つのステートと 1 つの出力をもつシンプルな Moore チャートを示しています。出力はステート A で 1 に設定され、出力の初期値は 4 です。

[チャート実行ごとに出力を初期化] パラメーターをオンにすると、ステート マシンのステートが A である場合を除き、出力値が 4 に戻ります。ステート A では出力が 1 に設定されます。[チャート実行ごとに出力を初期化] パラメーターをオフにした場合は、マシンがステート A を通過した後も出力値は 1 のままになり、4 に戻りません。

次の図は、この Moore チャートに対して生成される Verilog® コードについて、[チャート実行ごとに出力を初期化] をオンにした場合のコードとオフにした場合のコードをそれぞれ示しています。

次の表に、これらの 2 つの Moore マシンを Xilinx® Vivado® Virtex 7 デバイス用に合成した場合のリソースの使用を示します。[チャート実行ごとに出力を初期化] をオフにすると、生成される HDL コードに出力のステートのための追加のレジスタが含まれます。

| リソース | [チャート実行ごとに出力を初期化] をオンにした場合 | [チャート実行ごとに出力を初期化] をオフにした場合 |

|---|---|---|

| LUT | 18 | 20 |

| レジスタ | 1 | 3 |

| DSP | 0 | 0 |

| ブロック RAM | 0 | 0 |

参考

Chart (Stateflow)