このページの内容は最新ではありません。最新版の英語を参照するには、ここをクリックします。

クロック信号およびリセット信号のガイドライン

Simulink® モデリング環境では、クロック、リセット、クロック イネーブルなどのグローバル信号を作成しません。これらの信号はモデルの HDL コードを生成すると作成されます。Simulink でサンプル時間を使用して、クロック サイクルを指定できます。

モデルがシングル レートの場合、すべてのブロックが同じサンプル時間で動作することを意味します。合成ツールは、モデルに追加するレジスタまたは Delay ブロックがクロック レートで実行されることを推定します。合成ツールでは、データは転送元レジスタから転送先レジスタに 1 クロック サイクルで伝播されます。

これらのガイドラインは、HDL コードでクロック信号を生成する方法について示したものです。各ガイドラインに準拠要件のレベルを示す重大度レベルが割り当てられています。詳細については、HDL モデリング ガイドラインの重大度レベルを参照してください。

グローバル オーバーサンプリングを使用した周波数分割クロックの作成

ガイドライン ID

1.4.1

重大度

情報

説明

Simulink の基本サンプル レートの倍数として、HDL コード生成で使用する周波数分割クロック レートを設定できます。たとえば、Simulink の基本レートが 1 MHz で、ターゲット ハードウェアのクロック周波数を 50 MHz で実行するには、[ターゲット周波数] を 50 に設定し、[Simulink のレートを実際のハードウェアのレートとして扱う] を有効にします。これにより、目的のクロック周波数を実現する最適化されたオーバーサンプリング値を HDL Coder™ が決定できるようになります。詳細については、Simulink のレートを実際のハードウェアのレートとして扱うを参照してください。詳細については、グローバル オーバーサンプリング クロックの生成を参照してください。

クロック分周による整数倍クロックをもつマルチレート モデルを作成

ガイドライン ID

1.4.2

重大度

必須

説明

クロックレートの分周または複数クロックを使用して、マルチレート モデルを生成できます。マルチレート モデルの場合、Simulink® モデルの最速のサンプル時間は基本クロック レートに対応します。タイミング コントローラー エンティティは遅いサンプルレートで動作するブロックのクロックを制御するように作成されます。必要なレートと位相の情報をもつクロック イネーブル信号は、設計でこれらのブロックのクロックを制御します。

マルチレート モデルは、Simulink モデルで特定のブロックを使用したり、特定のブロック アーキテクチャを指定したり、リソース共有などの操作を使用したりすると作成されます。たとえば、次のブロック アーキテクチャの組み合わせによってマルチレート モデルが生成されます。

ニュートン・ラフソン実装による Divide ブロック。

ReciprocalSqrtBasedNewton 実装による Reciprocal ブロック。

カスケード アーキテクチャによる Sum of Elements ブロックと Product of Elements ブロック。

SqrtBasedNewton による Sqrt と ReciprocalSqrtBasedNewton 実装による Reciprocal Sqrt。

また、Simulink でマルチレート設計をモデル化するには、次のブロックを使用します。

[Simulink]、[Signal Attributes] ライブラリで、Rate Transition ブロックを使用します。

[DSP System Toolbox]、[Signal Operations] ライブラリで、Upsample ブロック、Downsample ブロック、Repeat ブロックを使用できます。

[HDL Coder]、[HDL RAMs] ライブラリで、HDL FIFO ブロックを使用します。

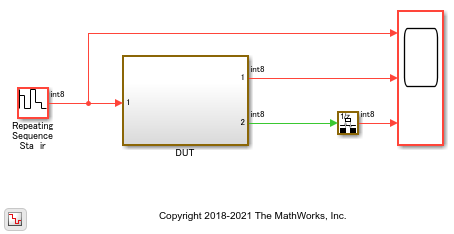

このモデルは、Rate Transition ブロックを使用してマルチレート設計を作成する方法を示します。

load_system('hdlcoder_multiclock') set_param('hdlcoder_multiclock','SimulationCommand','Update') open_system('hdlcoder_multiclock')

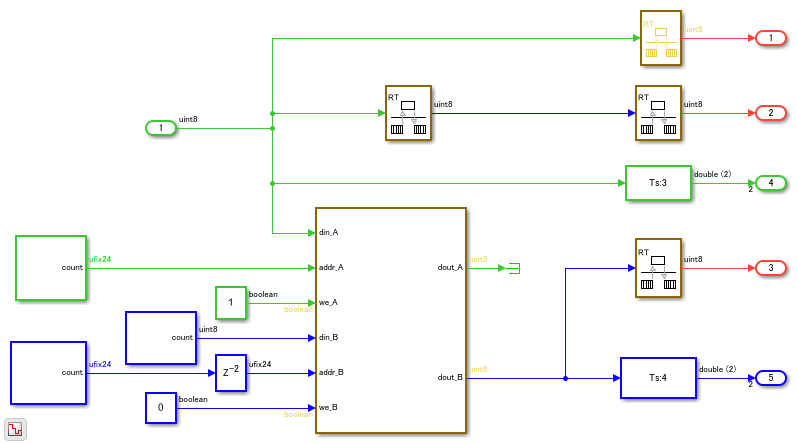

モデルのさまざまな色は、モデルがマルチレートであり、速いレートの D1 と遅いレートの D2 があることを示します。さまざまなサンプルレートを生成する Rate Transition ブロックを表示するには、DUT サブシステムをダブルクリックします。

open_system('hdlcoder_multiclock/DUT')

モデルのサンプル時間を表示するには、次のコマンドを実行します。

ts = Simulink.BlockDiagram.getSampleTimes('hdlcoder_multiclock');

sampletime_D1 = ts(1)

sampletime_D2 = ts(2)

sampletime_D1 =

SampleTime with properties:

Value: [1.0000e-03 0]

Description: 'Discrete 1'

ColorRGBValue: [1 0.2706 0.2275]

Annotation: 'D1'

OwnerBlock: []

ComponentSampleTimes: [0×0 Simulink.SampleTime]

sampletime_D2 =

SampleTime with properties:

Value: [0.0030 0]

Description: 'Discrete 2'

ColorRGBValue: [0.2275 0.7843 0.1922]

Annotation: 'D2'

OwnerBlock: []

ComponentSampleTimes: [0×0 Simulink.SampleTime]

マルチレート設計のモデルで Rate Transition ブロックを使用する場合、[データ転送中の整合性を確保] と [確定的にデータ転送を確保 (最大遅延))] のブロック パラメーターを選択します。出力サンプルレートが入力サンプルレートの整数倍であることを確認します。

マルチレート設計では、単一のクロック信号または複数のクロック信号を生成してさまざまなサンプルレートで動作するブロックのクロックを制御できます。この設定を指定するには、[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成]、[グローバル設定] ペインで、[クロックの入力] 設定を指定します。

既定では、[クロックの入力] は single として指定されます。単一のクロックは、モデルですべてのレジスタまたは Delay ブロックのクロックを制御するために生成されます。タイミング コントローラー イネーブル信号により、設計内のさまざまなブロックのクロックが制御されます。このモードでは、単一の高速なクロックが設計内のすべてのレジスタに接続されるため、電力の浪費が増加する可能性があります。

[クロックの入力] を multiple として指定すると、設計内のサンプルレートごとにクロック信号が生成されます。ただし、このモードではクロック端子、クロック イネーブル端子、リセット端子をそれぞれ外部に接続しなければなりません。HDL 設計には遅いクロック信号に接続されたレジスタが含まれるため、このモードでは電力が減少します。詳細については、HDL Coder での複数のクロックの使用を参照してください。

非整数の複数のサンプル時間に対する Dual Rate Dual Port RAM の使用

ガイドライン ID

1.4.3

重大度

必須

説明

Rate Transition ブロック、Upsample ブロック、Downsample ブロックを使用してマルチレート モデルを作成する場合、クロック レートは基本レートの整数倍でなければなりません。非整数倍であるクロックでマルチレート モデルを作成するには、Dual Rate Dual Port RAM ブロックを使用します。整数倍のクロックでは、HDL FIFO ブロックまたは Dual Rate Dual Port RAM ブロックを使用できます。

このモデルは、サンプルレートの非整数倍を作成する方法を示します。

load_system('hdlcoder_dual_rate_dual_port_RAM') set_param('hdlcoder_dual_rate_dual_port_RAM','SimulationCommand','Update') open_system('hdlcoder_dual_rate_dual_port_RAM/DUT')

Rate Transition ブロックの [データ転送中の整合性を確保] ブロック パラメーターがオフになっているため、このモデルの HDL コードは生成できません。RAM ブロックを使用する場合のアドレス制御の管理方法については、RAM ブロックや HDL Operations ライブラリのブロックを設計する際の考慮事項を参照してください。

HDL Coder での非同期クロックのモデル化

ガイドライン ID

1.4.4

重大度

推奨

説明

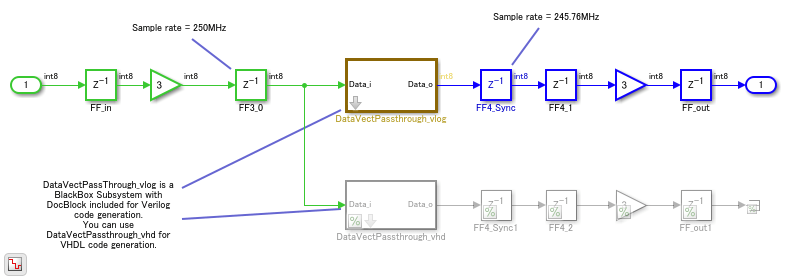

ほとんどの FPGA 設計には、さまざまな周波数で動作する複数の設計部分が含まれる複数のクロック領域がなければなりません。さまざまなサンプル レート間の遷移に対するパススルー実装を使用して、Simulink® でさまざまなクロック領域をモデル化できます。これらのサンプルレートは FPGA デバイスのクロック レートに対応します。

たとえば、モデル hdlcoder_multi_clock_domain を開いてから、DUT サブシステムを開きます。

load_system('hdlcoder_multi_clock_domain') set_param('hdlcoder_multi_clock_domain', 'SimulationCommand', 'Update') open_system('hdlcoder_multi_clock_domain/DUT')

DocBlock が含まれる BlackBox Subsystem が表示されます。これは、パススルー実装の Verilog® コードに対応するテキスト ファイルです。DocBlock を開いて Verilog コードを表示できます。このサブシステムの出力が異なるサンプルレートで動作しているか、サブシステムの入力のサンプルレートとは異なるクロック領域にあることがわかります。サブシステムにはパススルー実装に等価の VHDL® が含まれるコメント アウトされたパスも含まれます。VHDL コードを生成するには、このパスのコメントを解除し、Verilog BlackBox 実装が含まれるパスをコメント アウトします。

このモデルの Verilog コードを生成するには、次のコマンドを実行します。

makehdl('hdlcoder_multi_clock_domain/DUT')

生成された Verilog ヘッダー ファイルでは、モデル内にさまざまなクロック領域が表示されます。

// ------------------------------------------------------------- // // File Name: hdlsrc\hdlcoder_multi_clock_domain\DUT.v // Created: 2018-10-05 11:30:21 // // Generated by MATLAB 9.6 and HDL Coder 3.13 // // // -- ------------------------------------------------------------- // -- Rate and Clocking Details // -- ------------------------------------------------------------- // Model base rate: 1.30208e-12 // Target subsystem base rate: 2.65428e-12 // // // Clock Domain Description // -- ------------------------------------------------------------- // clk_1_3072 1 3072x slower than base rate clock // clk_1_3125 2 3125x slower than base rate clock // -- ------------------------------------------------------------- // // Output Signal Clock Domain Sample Time // -- ------------------------------------------------------------- // Output1 (no clock) 0 4.06901e-09 // -- ------------------------------------------------------------- // // -------------------------------------------------------------

ターゲット ハードウェアに基づくグローバル リセット タイプ設定の使用

ガイドライン ID

1.4.5

重大度

推奨

説明

リセット タイプを FPGA アーキテクチャと一致させると、ターゲット ハードウェアでの設計実行時におけるリソース使用率と速度が改善されます。この設定を制御するには、[コンフィギュレーション パラメーター] ダイアログ ボックスの [HDL コード生成] 、 [グローバル設定] 設定で、[リセット タイプ] を指定します。

Xilinx® デバイスをターゲットにする場合、[リセット タイプ] を Synchronous に設定します。Intel® デバイスまたは Altera® デバイスの場合、[リセット タイプ] を Asynchronous に設定します。

ターゲットにしているハードウェアで正しいリセット タイプが使用されていることを確認するには、HDL コード アドバイザーでXilinx デバイスと Altera デバイスのグローバル リセット設定をチェックのモデル チェックを実行します。

メモ

一部の Intel デバイスでは同期リセットの使用が推奨されます。推奨されるリセット設定については、そのデバイスの Intel または Xilinx のドキュメンテーションを参照してください。